Technical Reference Manual Version 1.3

www.espressif.com

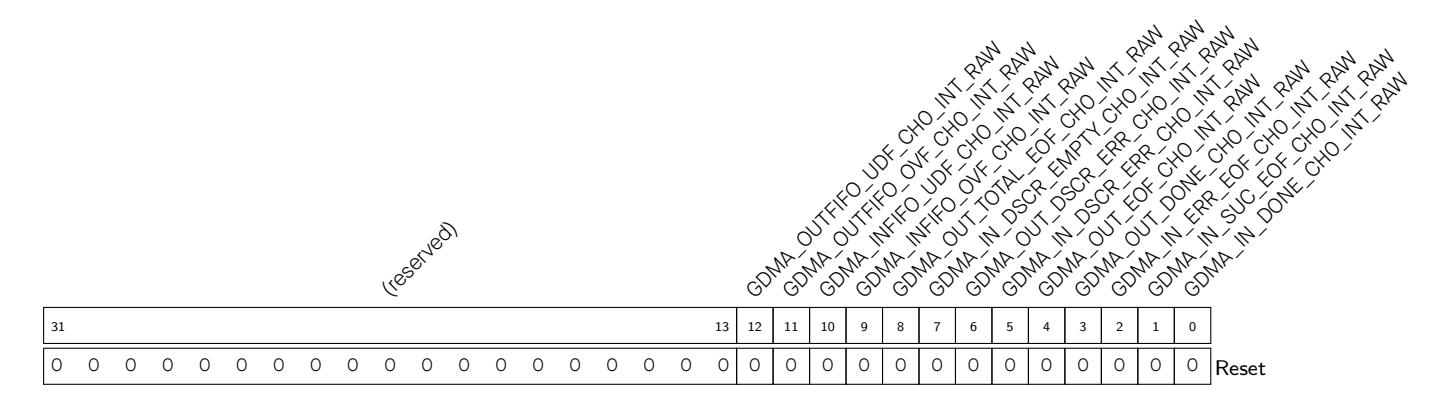

The ESP32-C3 Technical Reference Manual is targeted at developers working on low level software projects that use the ESP32-C3 SoC. It describes the hardware modules listed below for the ESP32-C3 SoC and other products in ESP32-C3 series. The modules detailed in this document provide an overview, list of features, hardware architecture details, any necessary programming procedures, as well as register descriptions.

Here are some tips on navigation through this extensive document:

| Release Status at a Glance | |||

| No. | Chapter | Progress | |

| Part I. Microprocessor and Master | |||

| 1 | ESP-RISC-V CPU | Published | |

| 2 | GDMA Controller (GDMA) | Published | |

| 3 |

Part II. Memory Organization

System and Memory |

Published | |

| 4 | eFuse Controller (EFUSE) | Published | |

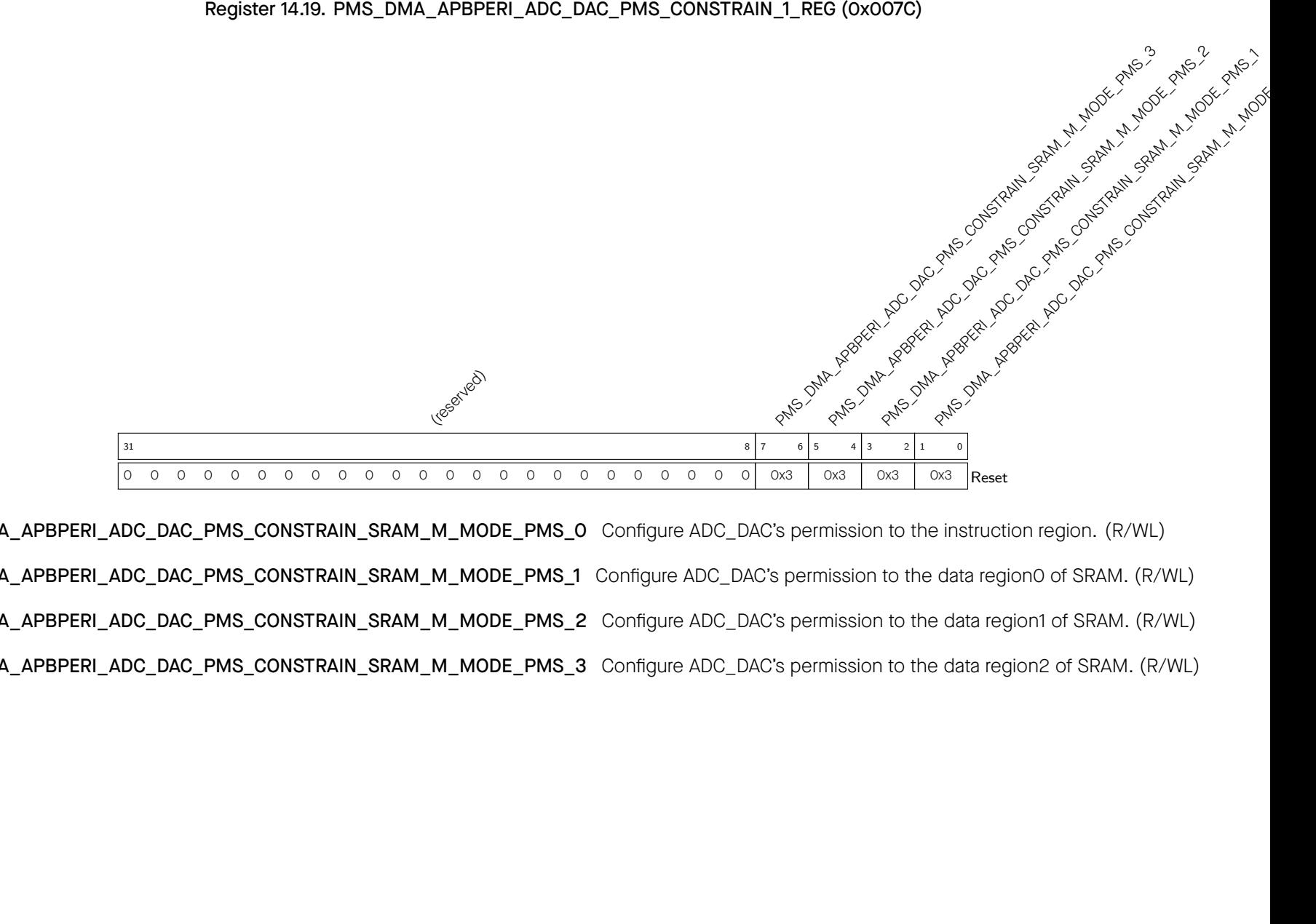

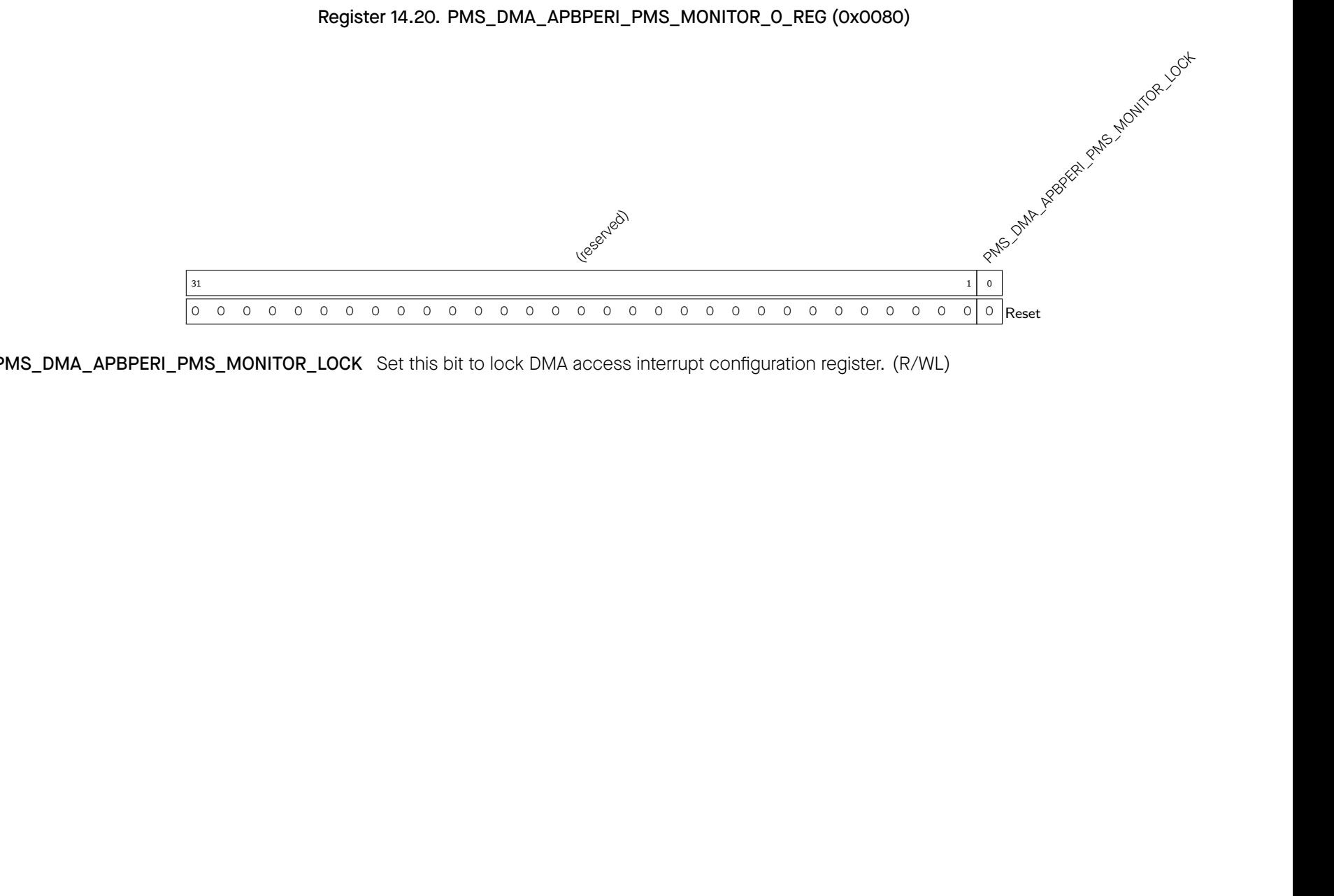

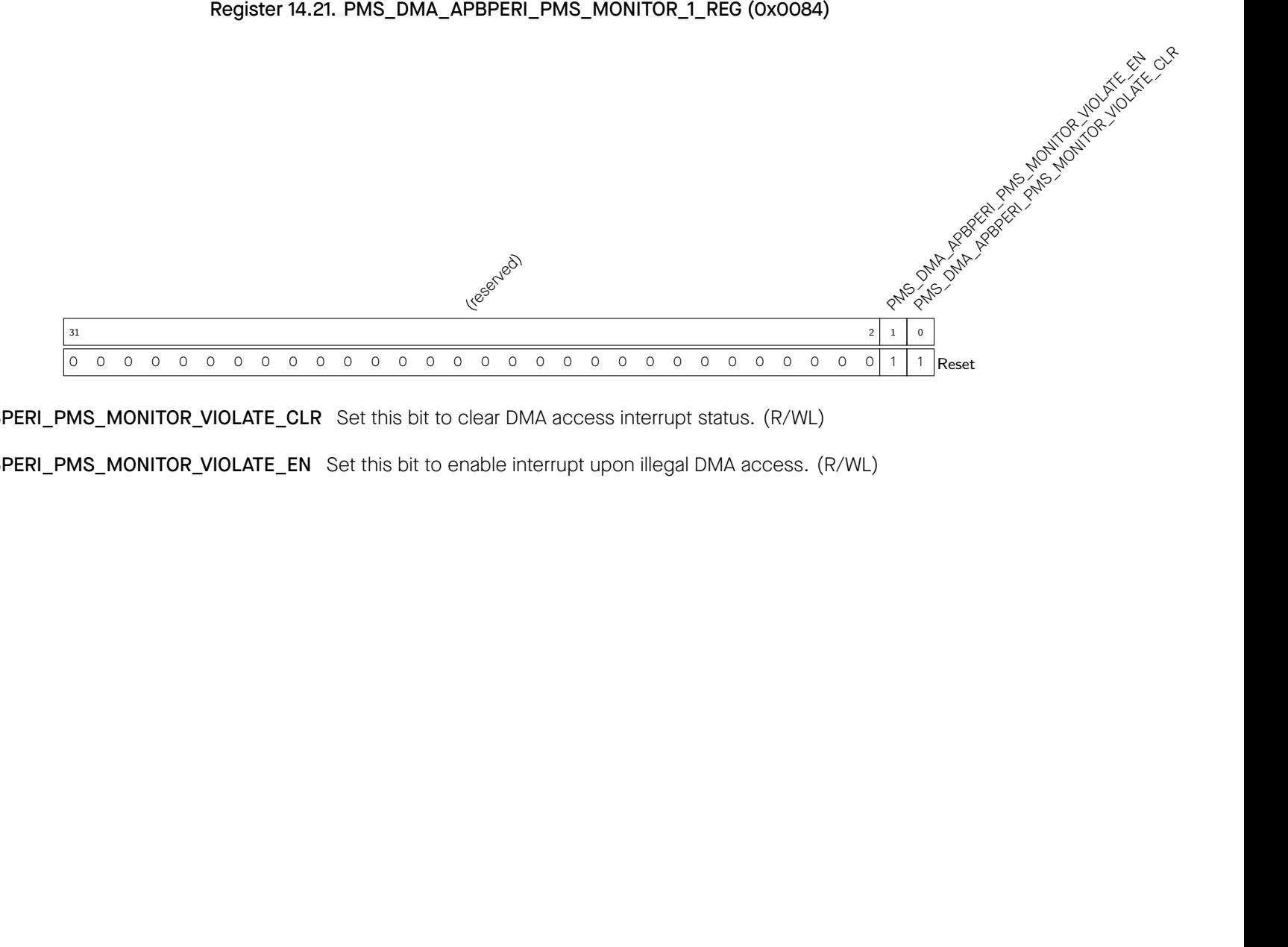

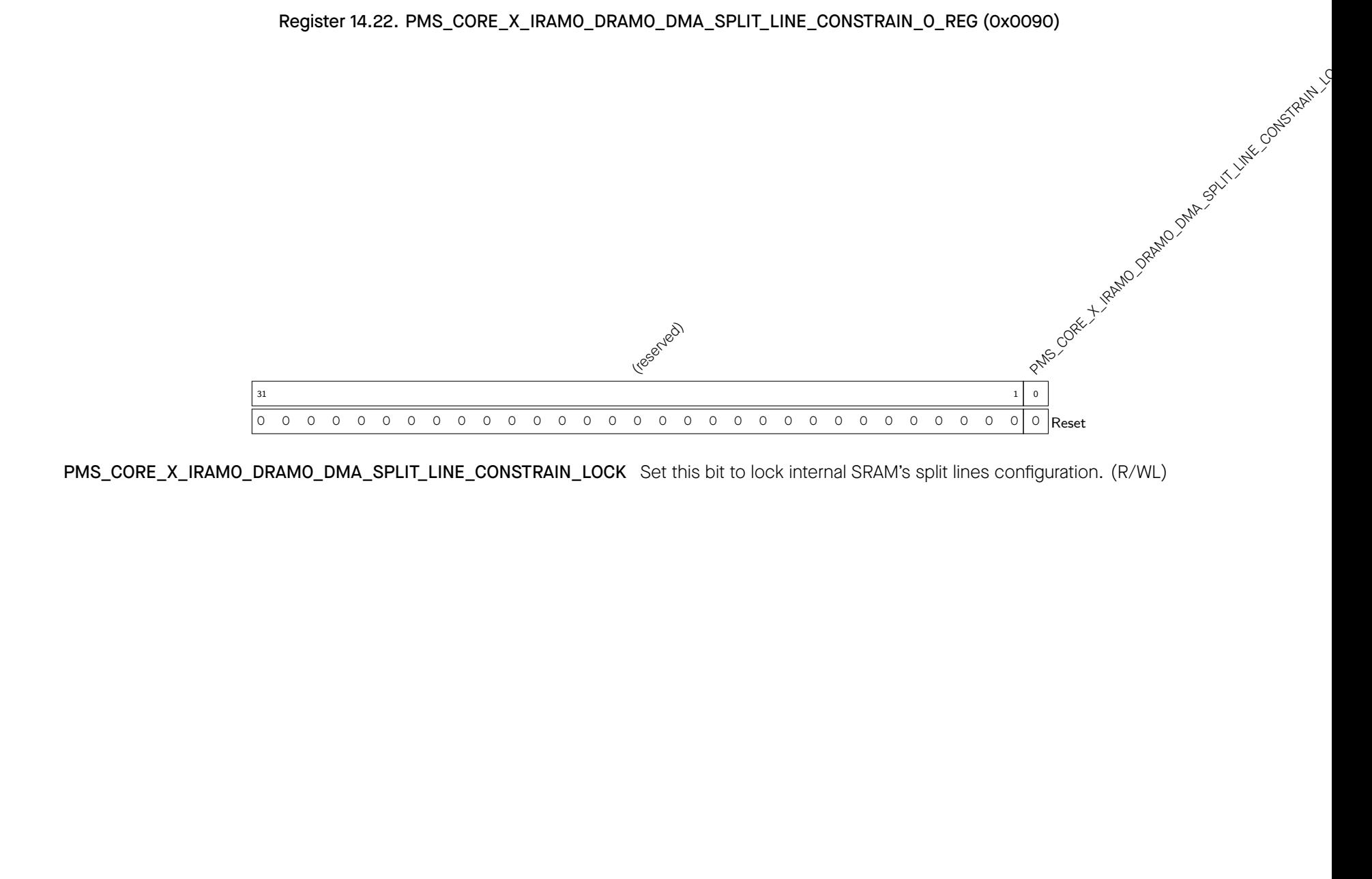

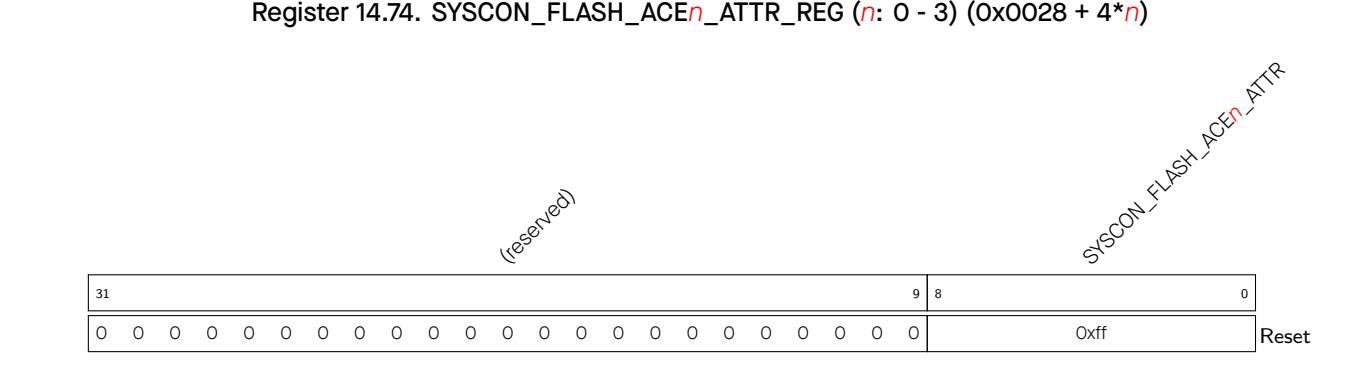

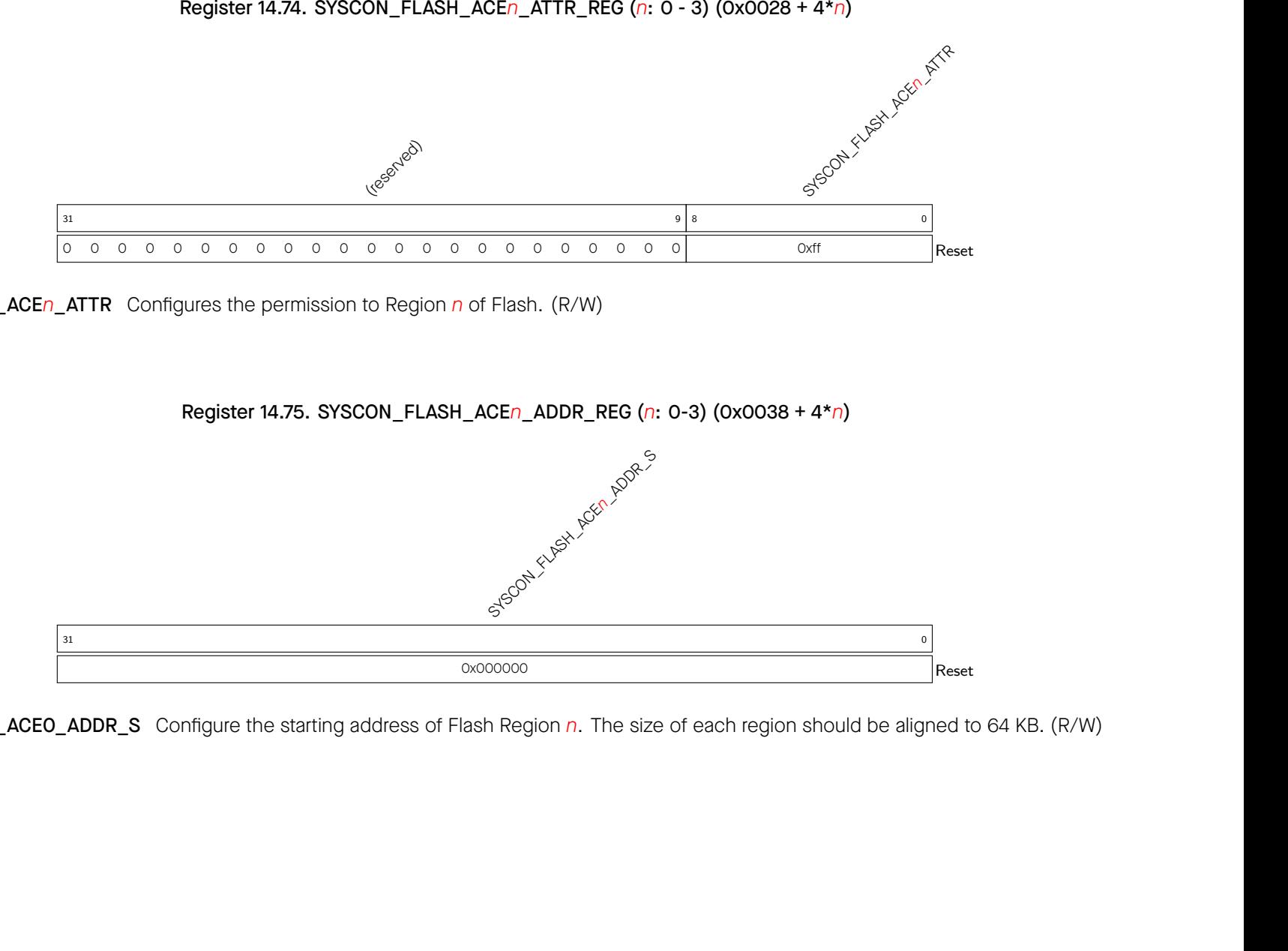

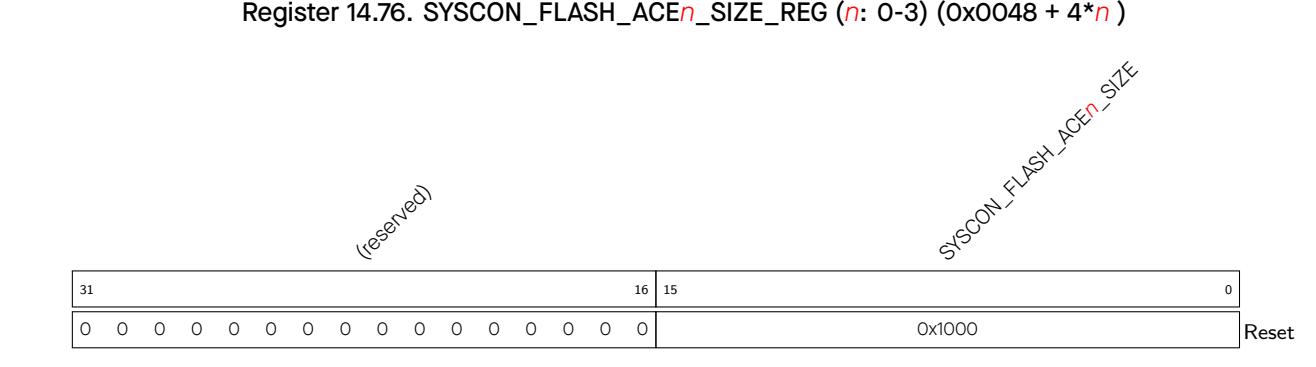

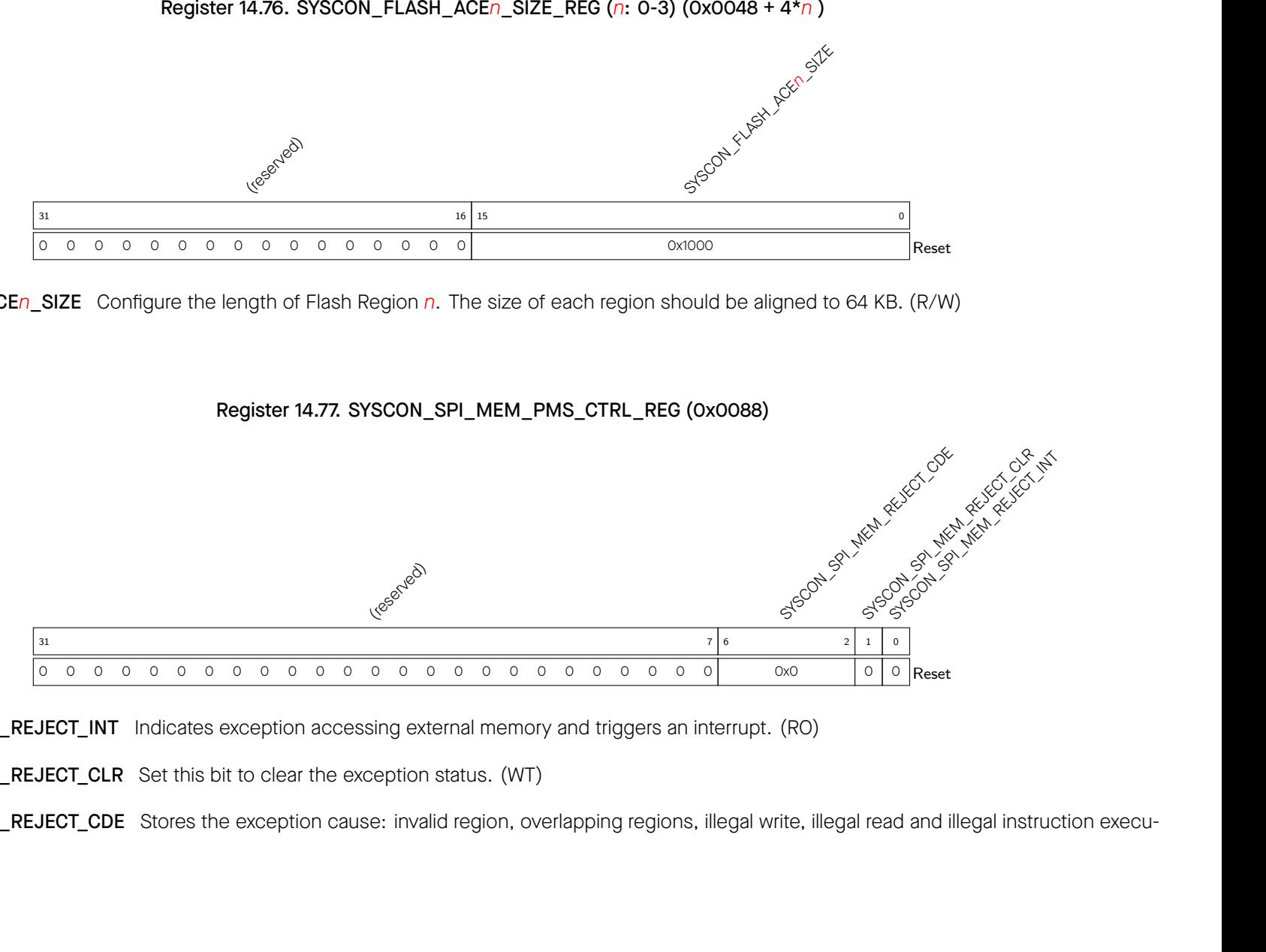

| Part III. System Component | |||

| 5 | IO MUX and GPIO Matrix (GPIO, IO MUX) | Published | |

| 6 | Reset and Clock | Published | |

| 7 | Chip Boot Control | Published | |

| 8 | Interrupt Matrix (INTERRUPT) | Published | |

| 9 | Low-power Management | Published | |

| 10 | System Timer (SYSTIMER) | Published | |

| 11 | Timer Group (TIMG) | Published | |

| 12 | Watchdog Timers (WDT) | Published | |

| 13 | XTAL32K Watchdog Timers (XTWDT) | Published | |

| 14 | Permission Control (PMS) | Published | |

| 15 | World Controller (WCL) | Published | |

|

16

System Registers (SYSREG) Published Published |

|||

| 17 |

Debug Assistant (ASSIST_DEBUG)

Part V. Cryptography/Security Component |

||

| 18 | SHA Accelerator (SHA) | Published | |

| 19 | AES Accelerator (AES) | Published | |

| 20 | RSA Accelerator (RSA) | Published | |

| 21 | HMAC Accelerator (HMAC) | Published | |

| 22 | Digital Signature (DS) | Published | |

| 23 | External Memory Encryption and Decryption (XTS_AES) | Published | |

| 24 | Clock Glitch Detection | Published | |

|

25

Random Number Generator (RNG) Published |

|||

| Part VII. Connectivity Interface | |||

| 26 | UART Controller (UART) | Published | |

| 27 | SPI Controller (SPI) | Published | |

| 28 | I2C Controller (I2C) | Published | |

| 29 | I2S Controller (I2S) | Published | |

| 30 | USB Serial/JTAG Controller (USB_SERIAL_JTAG) | Published | |

|

31

32 |

Two-wire Automotive Interface (TWAI)

LED PWM Controller (LEDC) |

Published

Published |

|

| 33 | Remote Control Peripheral (RMT) | Published | |

| Part VIII. Analog Signal Processing | |||

Check the link or the QR code to make sure that you use the latest version of this document: https://www.espressif.com/sites/default/files/documentation/esp32-c3_technical_reference_ manual_en.pdf

| Contents | ||||

|---|---|---|---|---|

| I | Microprocessor and Master | |||

| 1 | ESP-RISC-V CPU | |||

| 1.1 | Overview | |||

| 1.2 | Features | |||

|

1.3

1.4 |

Address Map

Configuration and Status Registers (CSRs) |

|||

|

1.4.1

Register Summary |

||||

| 1.4.2 | Register Description | |||

| 1.5 | Interrupt Controller | |||

| 1.5.1 | Features | |||

| 1.5.2 | Functional Description | |||

| 1.5.3 | Suggested Operation | |||

|

1.5.3.1

Latency Aspects |

||||

|

1.5.3.2

Configuration Procedure |

||||

| 1.5.4 | Register Summary | |||

| 1.5.5 | Register Description | |||

| 1.6 | Debug | |||

| 1.6.1 | Overview | |||

| 1.6.2 | Features | |||

| 1.6.3 | Functional Description | |||

|

1.6.4

1.6.5 |

Register Summary

Register Description |

|||

| 1.7 | Hardware Trigger | |||

| 1.7.1 | Features | |||

| 1.7.2 | Functional Description | |||

| 1.7.3 | Trigger Execution Flow | |||

| 1.7.4 | Register Summary | |||

| 1.7.5 | Register Description | |||

| 1.8 | Memory Protection | |||

| 1.8.1 | Overview | |||

| 1.8.2 | Features | |||

| 1.8.3 | Functional Description | |||

|

1.8.4

1.8.5 |

Register Summary

Register Description |

|||

| 2 | GDMA Controller (GDMA) | |||

| 2.1 | Overview | |||

| 2.2 | Features | |||

|

2.3

2.4 |

Architecture

Functional Description |

|||

| 2.4.2 | Peripheral-to-Memory and Memory-to-Peripheral Data Transfer | 63 | ||

|---|---|---|---|---|

| 2.4.3 | Memory-to-Memory Data Transfer | 63 | ||

| 2.4.4 | Enabling GDMA | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 2.4.5 | Linked List Reading Process | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 2.4.6 | EOF | 65 | ||

| 2.4.7 | Accessing Internal RAM | 65 | ||

| 2.4.8 | Arbitration | 66 | ||

| 2.5 | GDMA Interrupts | 66 | ||

| 2.6 | Programming Procedures | 67 | ||

| 2.6.1 | Programming Procedure for GDMA Clock and Reset | 67 | ||

| 2.6.2 | Programming Procedures for GDMA's Transmit Channel | 67 | ||

| 2.6.3 | Programming Procedures for GDMA's Receive Channel | 67 | ||

| 2.6.4 | Programming Procedures for Memory-to-Memory Transfer | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 2.7 | Register Summary | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 2.8 | Registers | 73 | ||

| Ш | Memory Organization | 90 | ||

| 3 | System and Memory | 91 | ||

| 3.1 | Overview | 91 | ||

| 3.2 | Features | 91 | ||

| 3.3 | Functional Description | 92 | ||

| 3.3.1 | Address Mapping | 92 | ||

| 3.3.2 | Internal Memory | 93 | ||

| 3.3.3 | External Memory | 94 | ||

|

3.3.3.1

External Memory Address Mapping |

95 | |||

|

3.3.3.2

Cache |

95 | |||

|

3.3.3.3

Cache Operations |

96 | |||

| 3.3.4 | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | 96 | ||

| 3.3.5 | Modules/Peripherals | 97 | ||

|

3.3.5.1

Module/Peripheral Address Mapping |

98 | |||

| 4 | eFuse Controller (EFUSE) | 100 | ||

| 4.1 | Overview | 100 | ||

| 4.2 | Features | 100 | ||

| 4.3 | Functional Description | 100 | ||

| 4.3.1 | Structure | 100 | ||

|

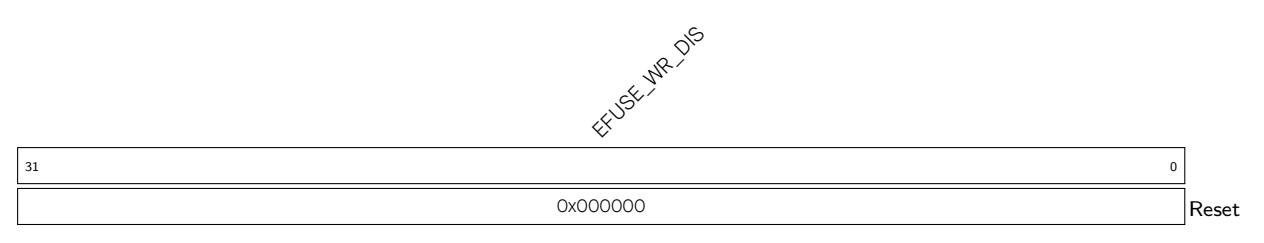

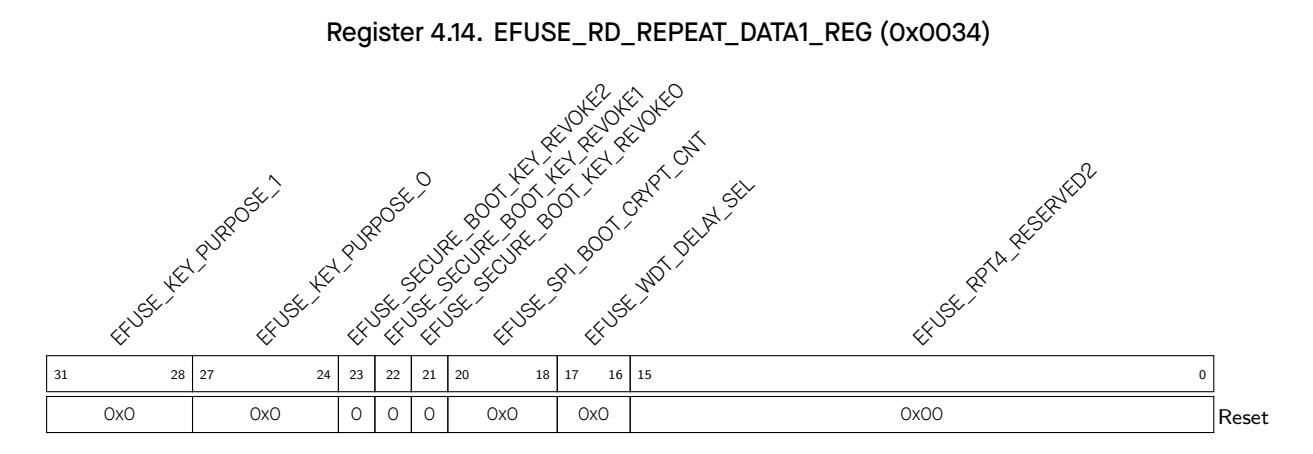

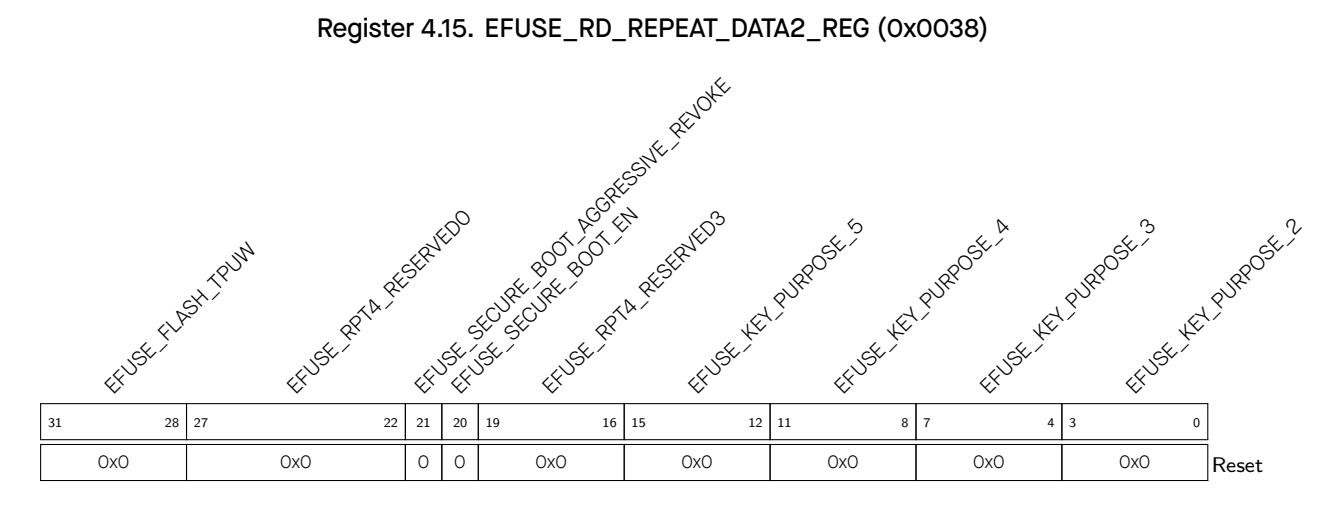

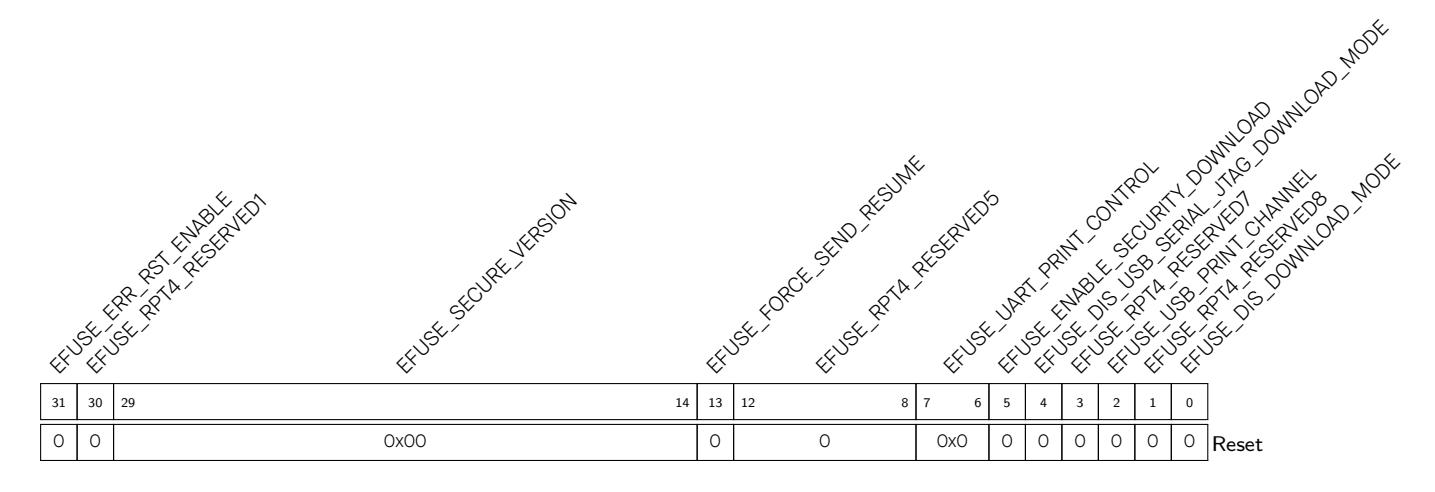

4.3.1.1

EFUSE_WR_DIS |

106 | |||

|

4.3.1.2

EFUSE_RD_DIS |

106 | |||

|

4.3.1.3

Data Storage |

106 | |||

| 4.3.2 | Programming of Parameters | 107 | ||

|

4.3.3

User Read of Parameters |

109 | |||

| 4.3.4 | eFuse VDDQ Timing | 111 | ||

|

4.3.5

The Use of Parameters by Hardware Modules |

111 | |||

| 4.3.6 | 111 | |||

| 4.4 | Register Summary | |||

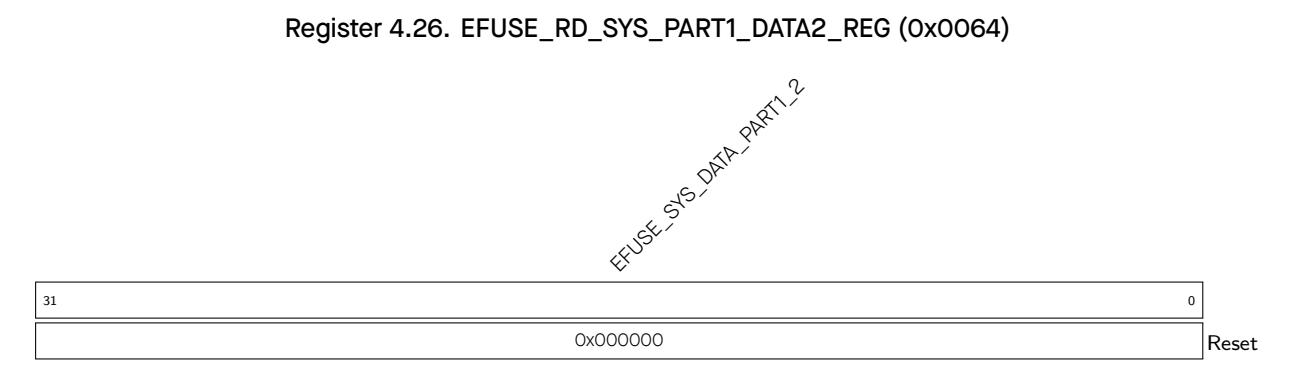

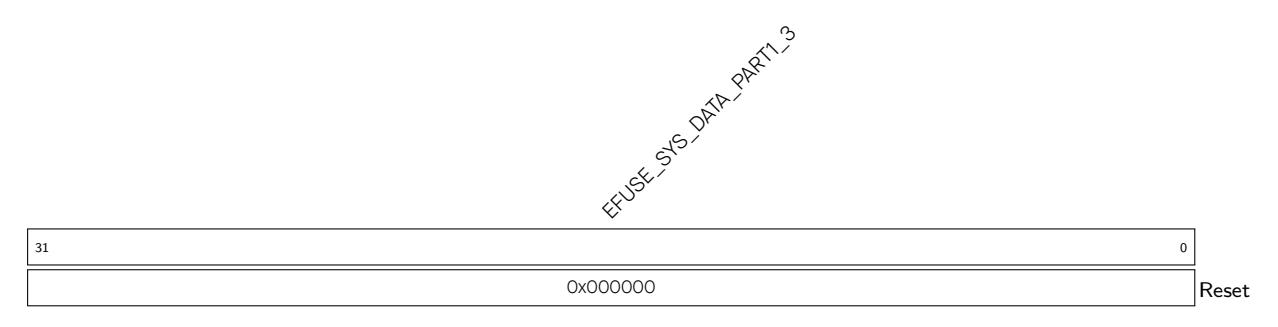

| 4.5 | Registers | 116 |

|---|---|---|

| Ш | System Component | 158 |

| 5 | IO MUX and GPIO Matrix (GPIO, IO MUX) | 159 |

| 5.1 | Overview | 159 |

| 5.2 | Features | 159 |

| 5.3 | Architectural Overview | 159 |

| 5.4 | Peripheral Input via GPIO Matrix | 161 |

|

Overview

5.4.1 |

161 | |

|

Signal Synchronization

5.4.2 |

162 | |

|

Functional Description

5.4.3 |

162 | |

|

Simple GPIO Input

5.4.4 |

163 | |

| 5.5 | Peripheral Output via GPIO Matrix | 163 |

|

5.5.1

Overview |

163 | |

|

5.5.2

Functional Description |

164 | |

|

5.5.3

Simple GPIO Output |

165 | |

|

Sigma Delta Modulated Output (SDM)

5.5.4 |

165 | |

|

5.5.4.1

Functional Description |

165 | |

|

SDM Configuration

5.5.4.2 |

166 | |

| 5.6 | Direct Input and Output via IO MUX | 166 |

|

5.6.1

Overview |

166 | |

|

Functional Description

5.6.2 |

166 | |

| 5.7 | Analog Functions of GPIO Pins | 166 |

| 5.8 | Pin Functions in Light-sleep | 167 |

| 5.9 | Pin Hold Feature | 167 |

| 5.10 | Power Supplies and Management of GPIO Pins | 167 |

|

Power Supplies of GPIO Pins

5.10.1 |

167 | |

|

Power Supply Management

5.10.2 |

168 | |

| 5.11 | Peripheral Signal List | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |

| 5.12 | IO MUX Functions List | 174 |

| 5.13 | Analog Functions List | 175 |

| 5.14 | Register Summary | 176 |

|

GPIO Matrix Register Summary

5.14.1 |

176 | |

|

IO MUX Register Summary

5.14.2 |

178 | |

|

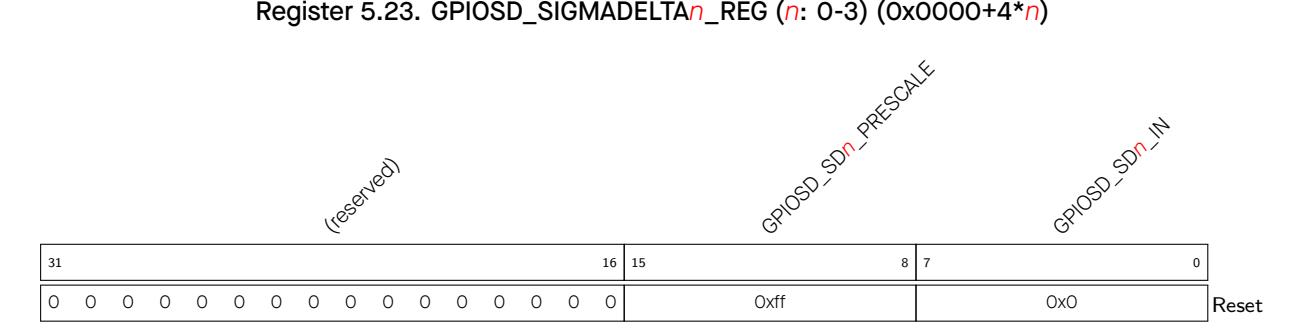

SDM Register Summary

5.14.3 |

178 | |

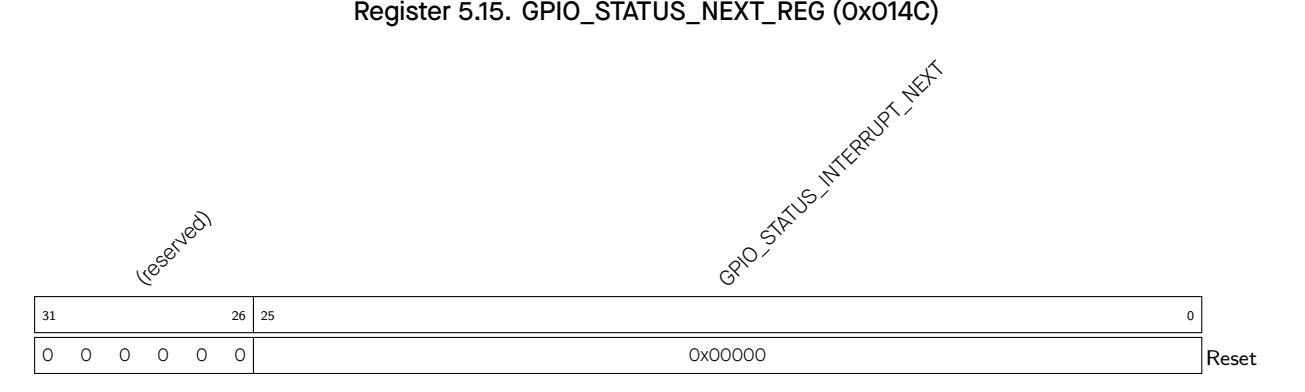

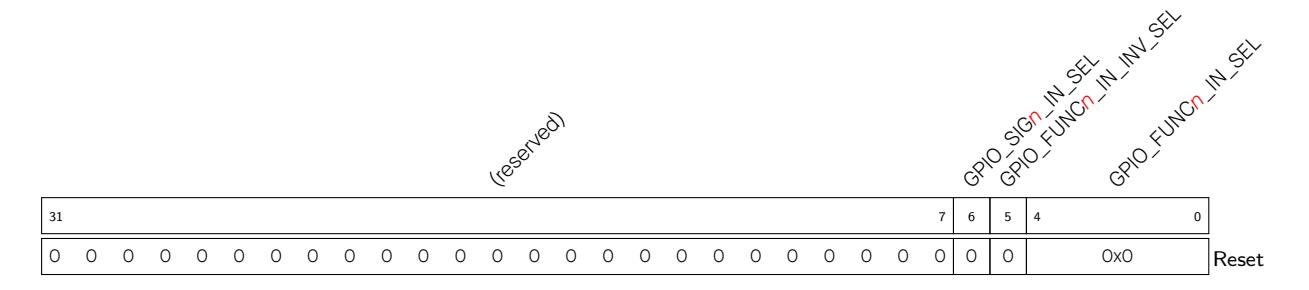

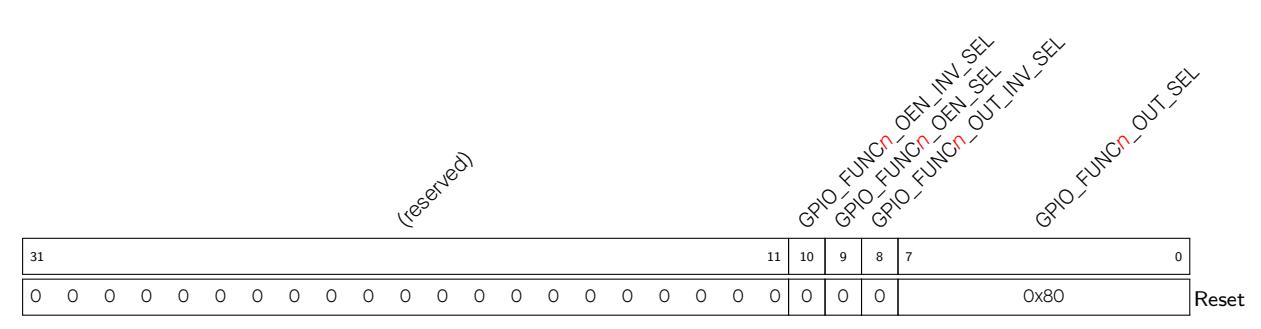

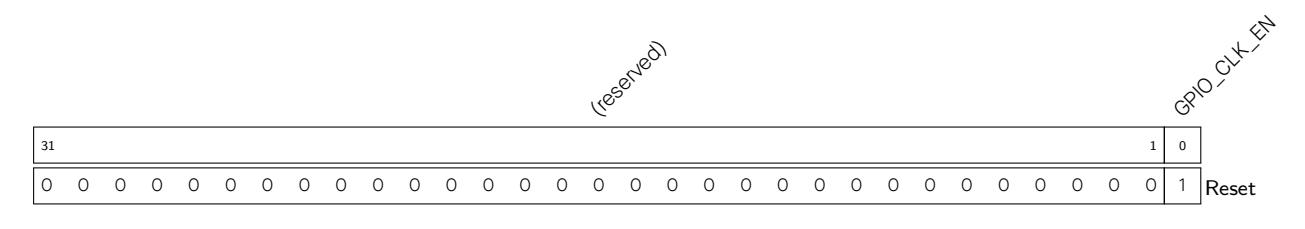

| 5.15 | Registers | 179 |

|

5.15.1

GPIO Matrix Registers |

179 | |

|

IO MUX Registers

5.15.2 |

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | |

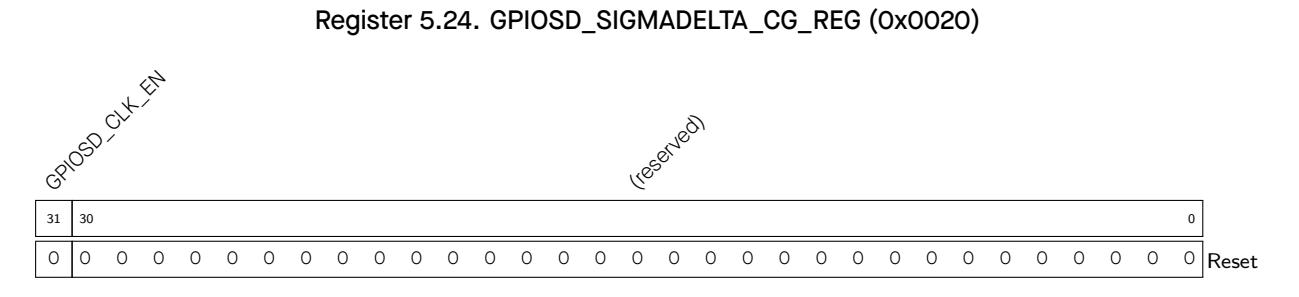

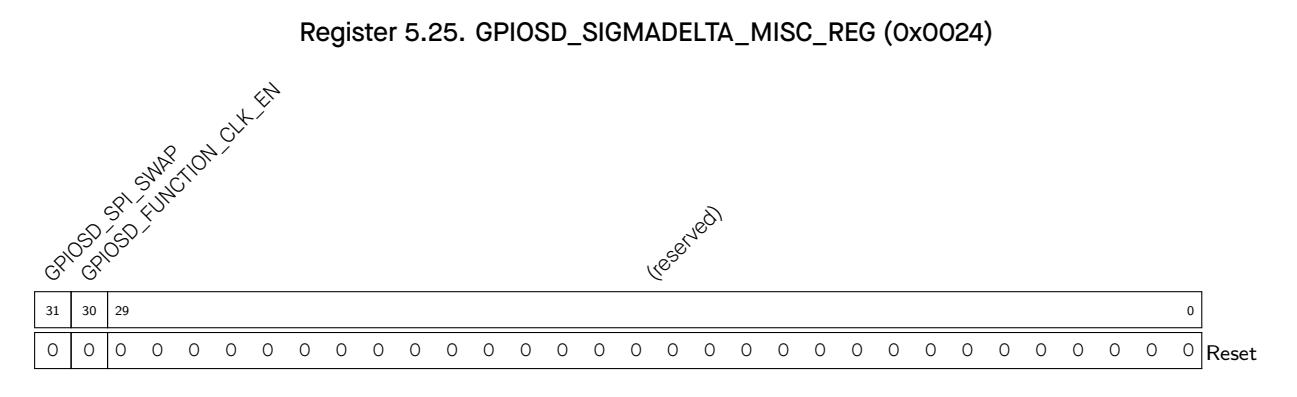

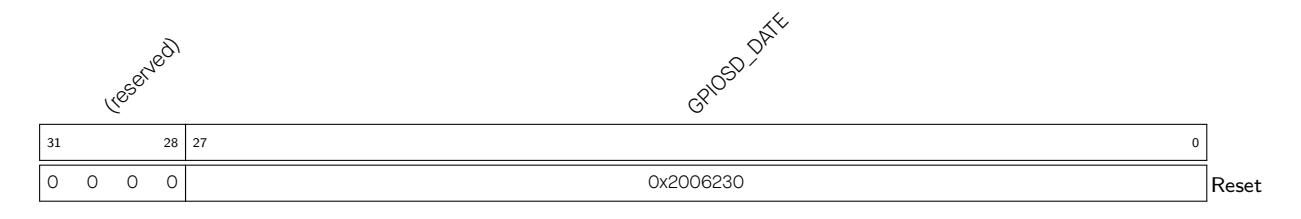

| 5.15.3 SDM Output Registers | 188 | |

| 6 | Reset and Clock | 191 |

| 6.1 | Reset | 191 |

|

6.1.1

Overview |

191 | |

|

6.1.2

Architectural Overview |

191 | |

|

6.1.3

Features |

191 |

| 6.1.4 | Functional Description | 192 | ||||

|---|---|---|---|---|---|---|

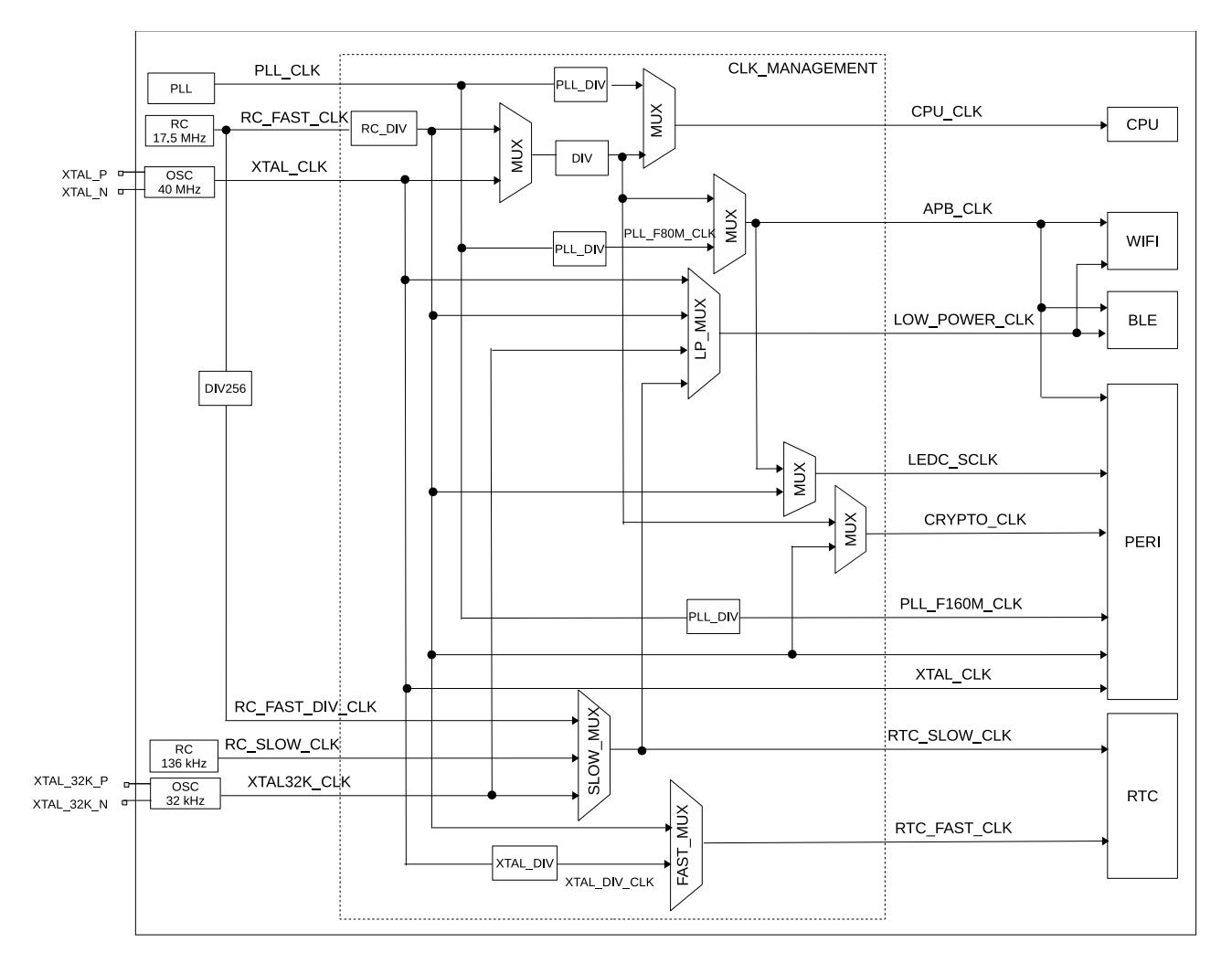

| 6.2 | Clock | 193 | ||||

| 6.2.1 | Overview | 193 | ||||

| 6.2.2 | Architectural Overview | 194 | ||||

| 6.2.3 | Features | 194 | ||||

| 6.2.4 | Functional Description | 194 | ||||

| 6.2.4.1 | CPU Clock | 195 | ||||

| 6.2.4.2 | Peripheral Clock | 195 | ||||

| 6.2.4.3 | Wi-Fi and Bluetooth LE Clock | 197 | ||||

| 6.2.4.4 | RTC Clock | 197 | ||||

| 7 | Chip Boot Control | 198 | ||||

| 7.1 | Overview | 198 | ||||

| 7.2 | Boot Mode Control | 199 | ||||

| 7.3 | ROM Messages Printing Control | 200 | ||||

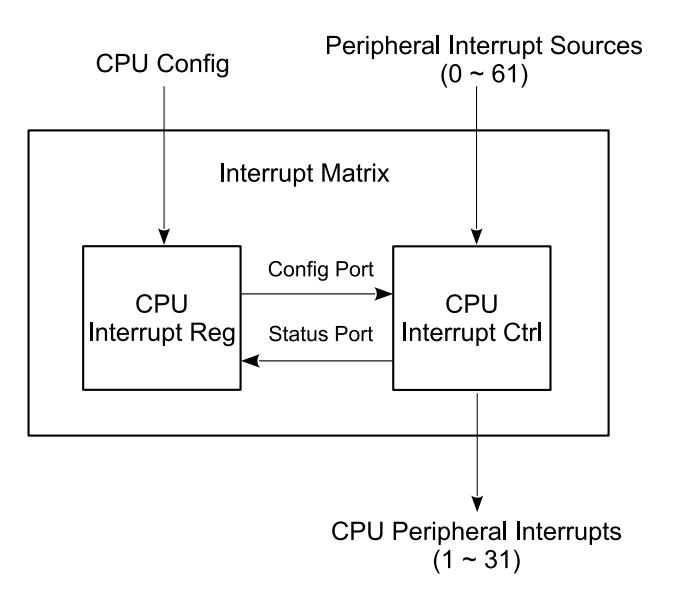

| 8 | Interrupt Matrix (INTERRUPT) | 202 | ||||

| 8.1 | Overview | 202 | ||||

| 8.2 | Features |

202

203 |

||||

| 8.3 | Functional Description | |||||

|

8.3.1

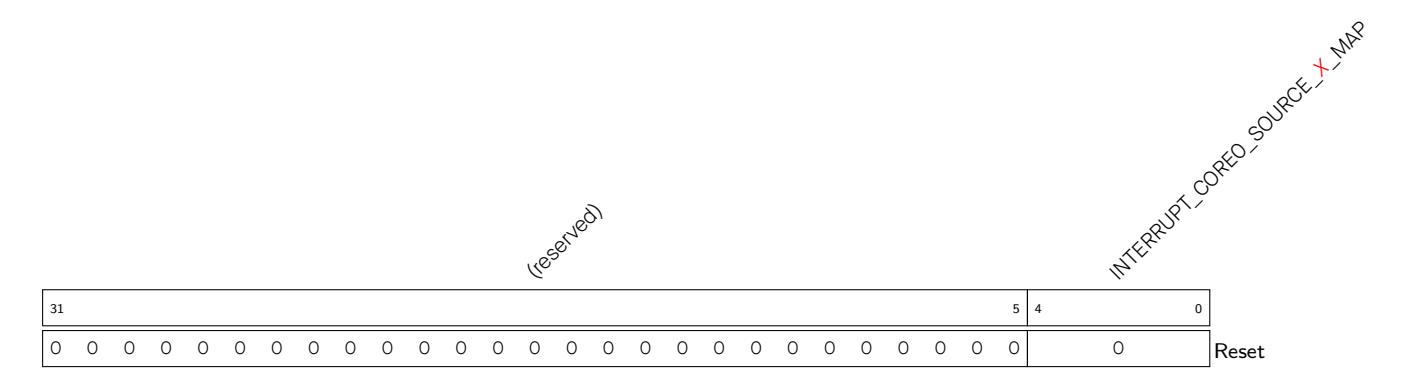

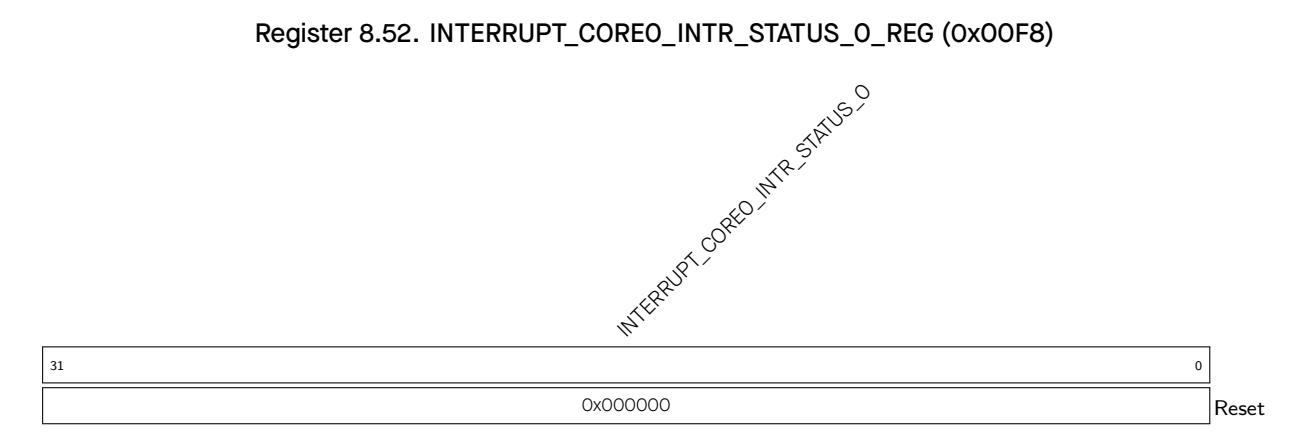

Peripheral Interrupt Sources |

||||||

| 8.3.2 | CPU Interrupts | 207 | ||||

| 8.3.3 | Allocate Peripheral Interrupt Source to CPU Interrupt | 207 | ||||

| 8.3.3.1 | Allocate one peripheral interrupt source (Source_X) to CPU | 207 | ||||

|

8.3.3.2

8.3.3.3 |

Allocate multiple peripheral interrupt sources (Source_Xn) to CPU

Disable CPU peripheral interrupt source (Source_X) |

207 | ||||

| 8.3.4 | Query Current Interrupt Status of Peripheral Interrupt Source |

207

207 |

||||

| 209 | ||||||

|

8.4

8.5 |

Registers | Register Summary | 213 | |||

| 9 | Low-power Management | 219 | ||||

| 9.1 | Introduction | 219 | ||||

| 9.2 | Features | 219 | ||||

| 9.3 | Functional Description | 219 | ||||

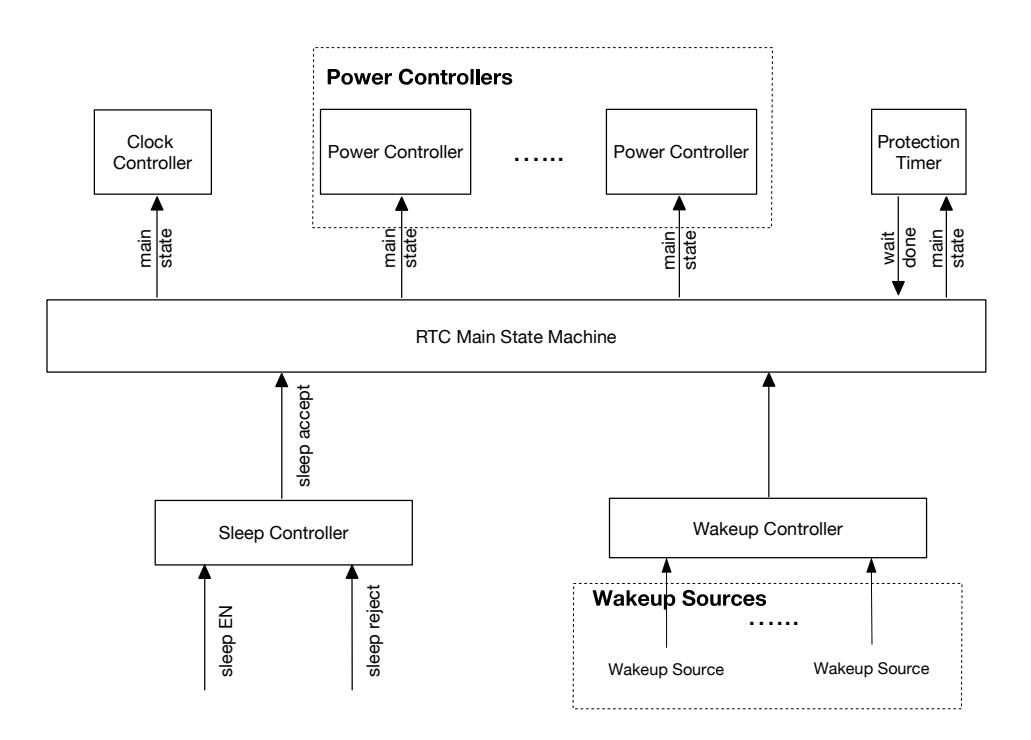

| 9.3.1 | Power Management Unit (PMU) | 221 | ||||

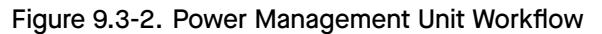

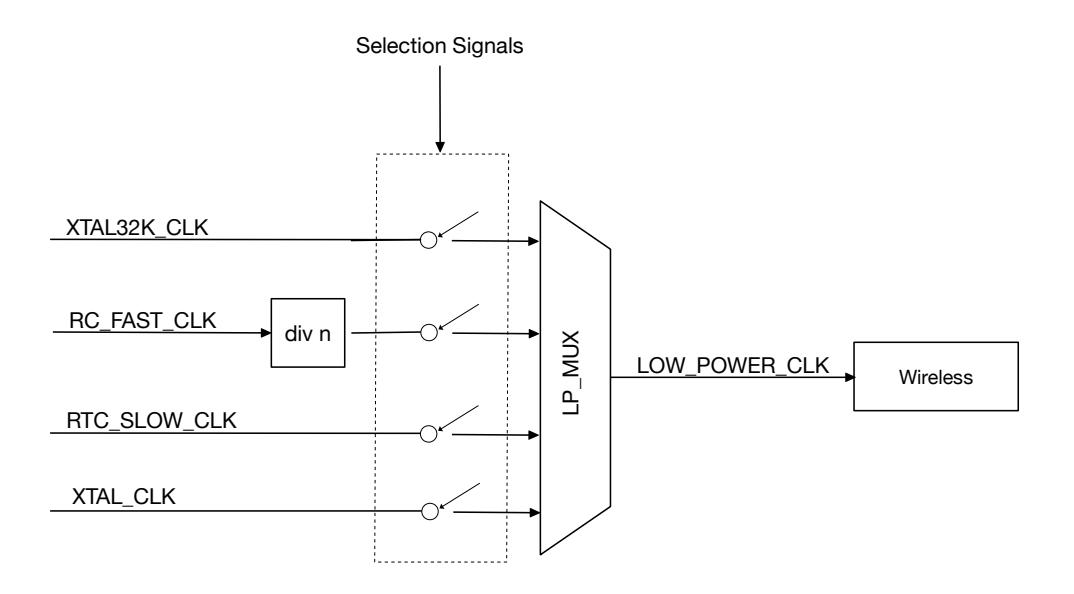

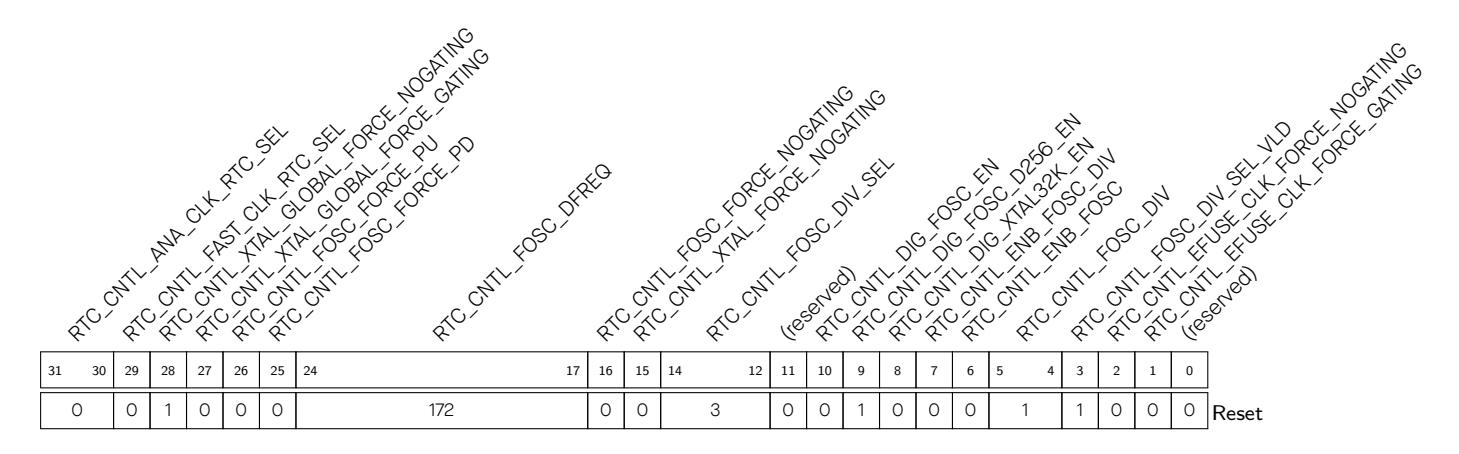

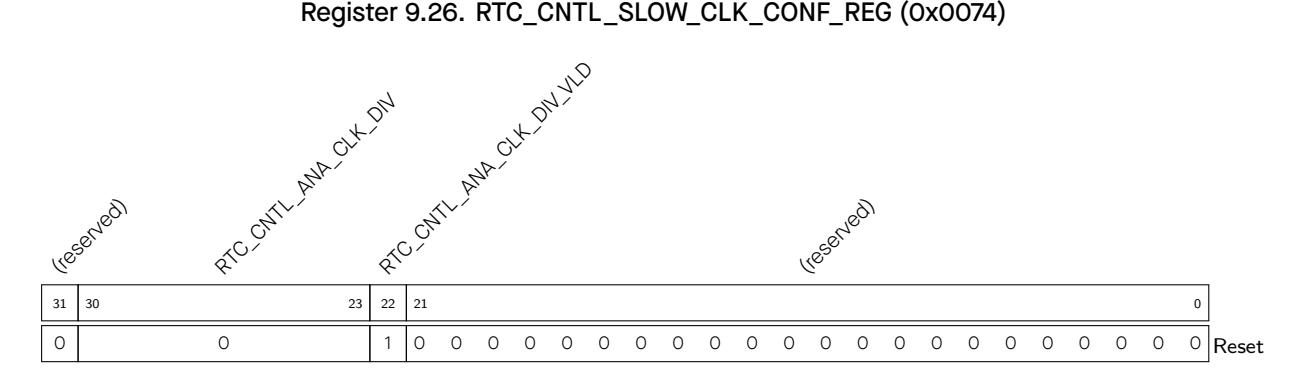

| 9.3.2 | Low-Power Clocks | |||||

| 9.3.3 | Timers | 223 | ||||

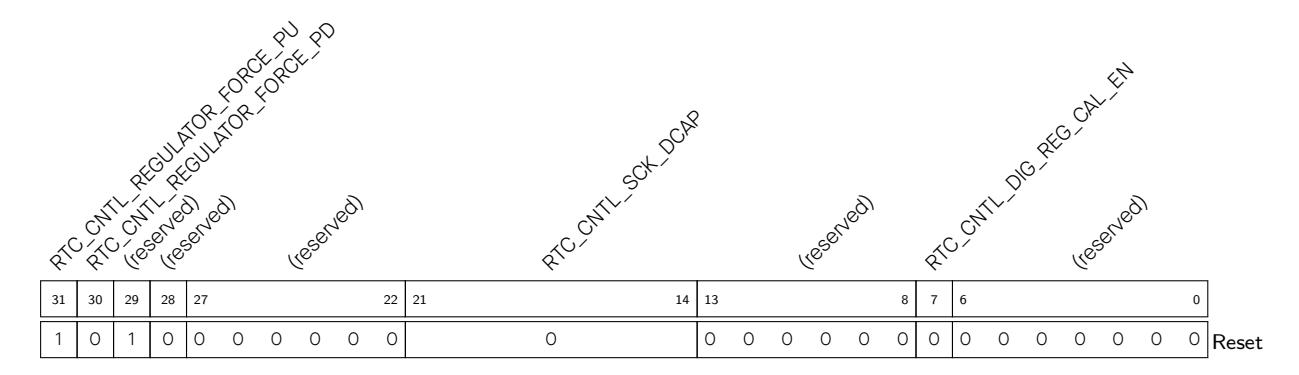

| 9.3.4 | Voltage Regulators | 224 | ||||

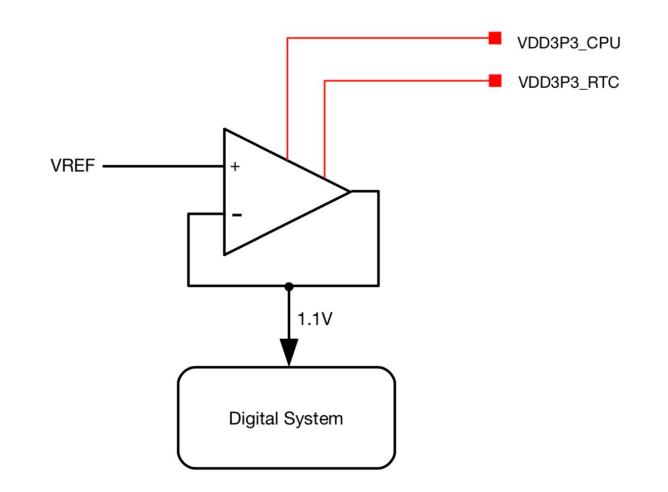

| 9.3.4.1 | Digital System Voltage Regulator | 224 | ||||

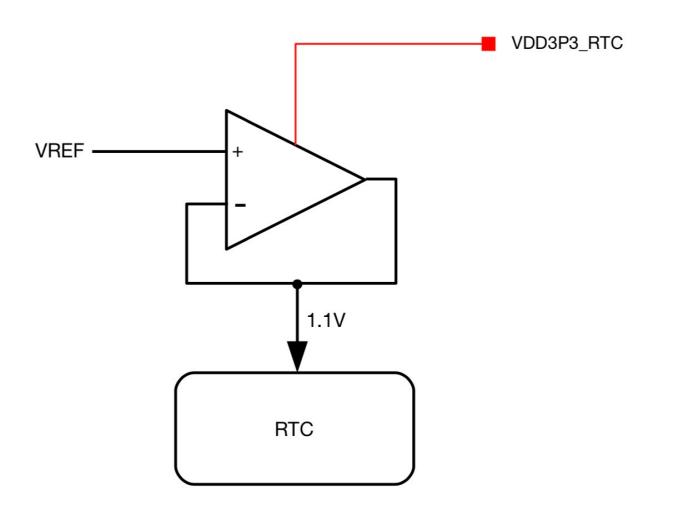

| 9.3.4.2 | Low-power Voltage Regulator | 225 | ||||

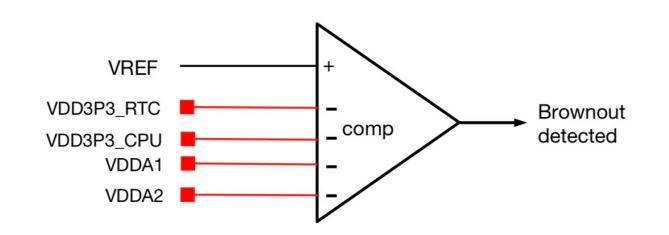

| 9.3.4.3 | Brownout Detector | 225 | ||||

| 9.4 | Power Modes Management | |||||

| 9.4.1 | Power Domain | |||||

| 9.4.2 | Pre-defined Power Modes | 227 | ||||

| 9.4.3 | Wakeup Source | 227 | ||||

|

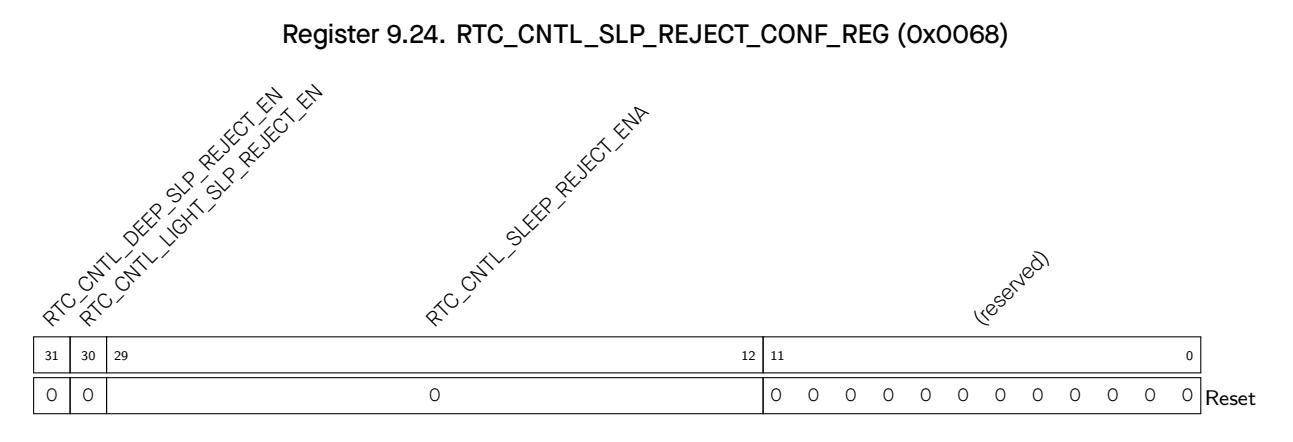

9.4.4

Reject Sleep |

||||||

| 9.5 | Retention DMA | 228 |

|---|---|---|

| 9.6 | RTC Boot | 229 |

| 9.7 | Register Summary | 231 |

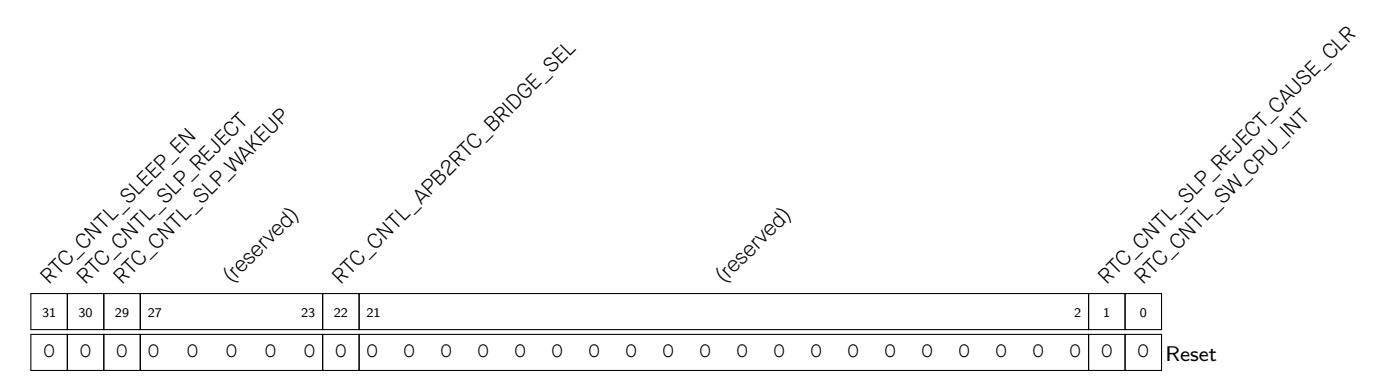

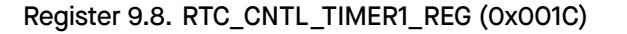

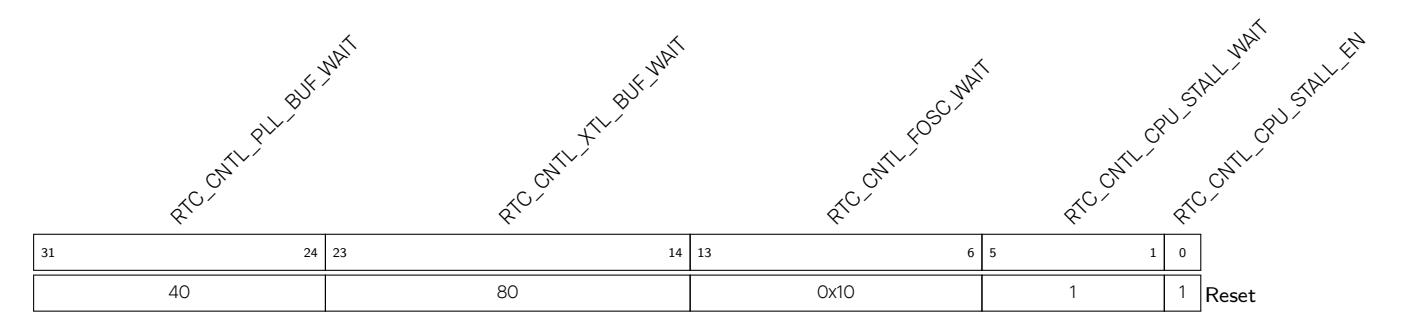

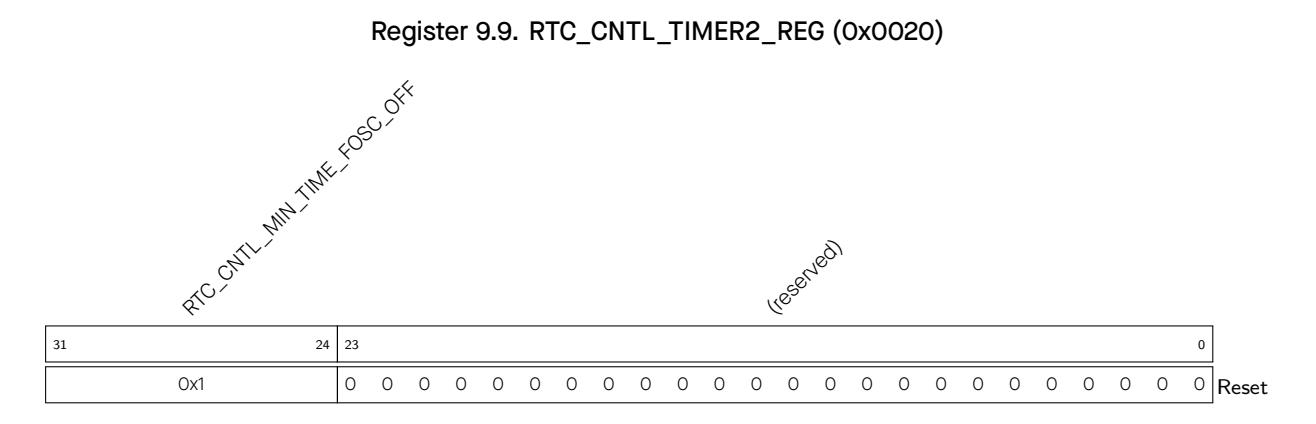

| 9.8 | Registers | 233 |

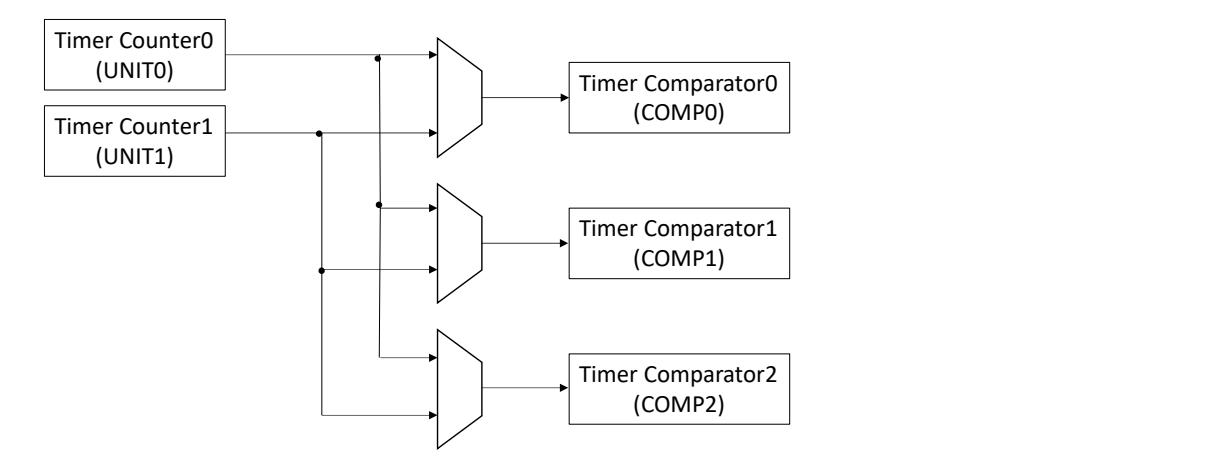

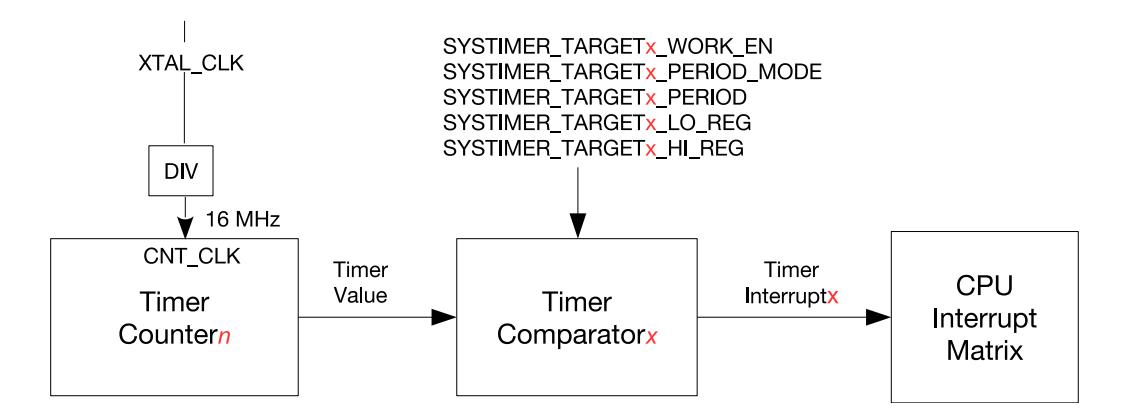

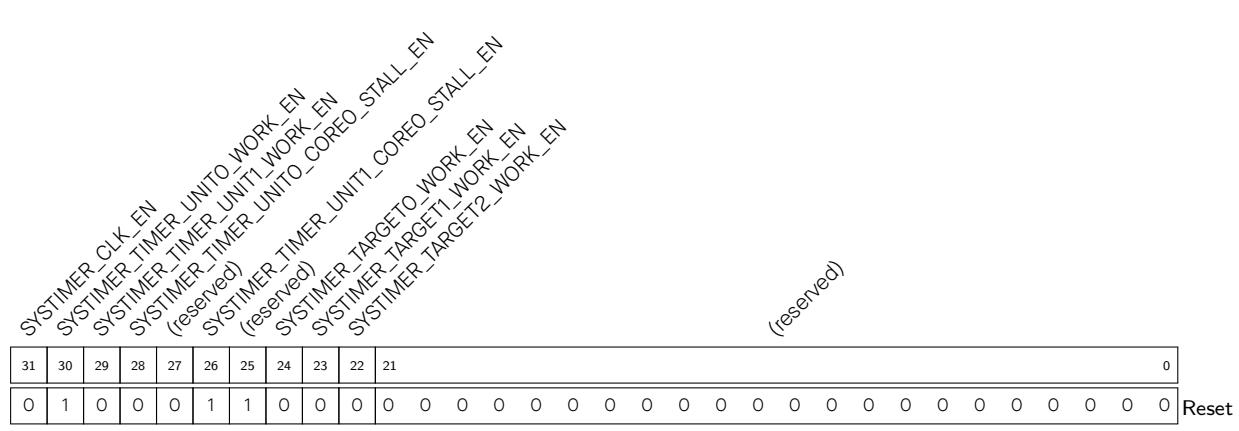

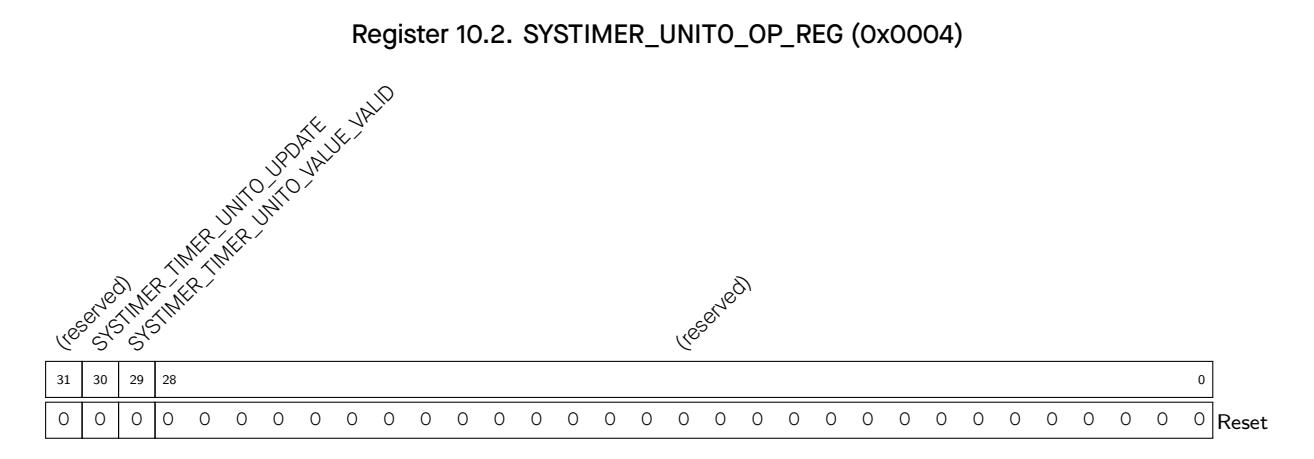

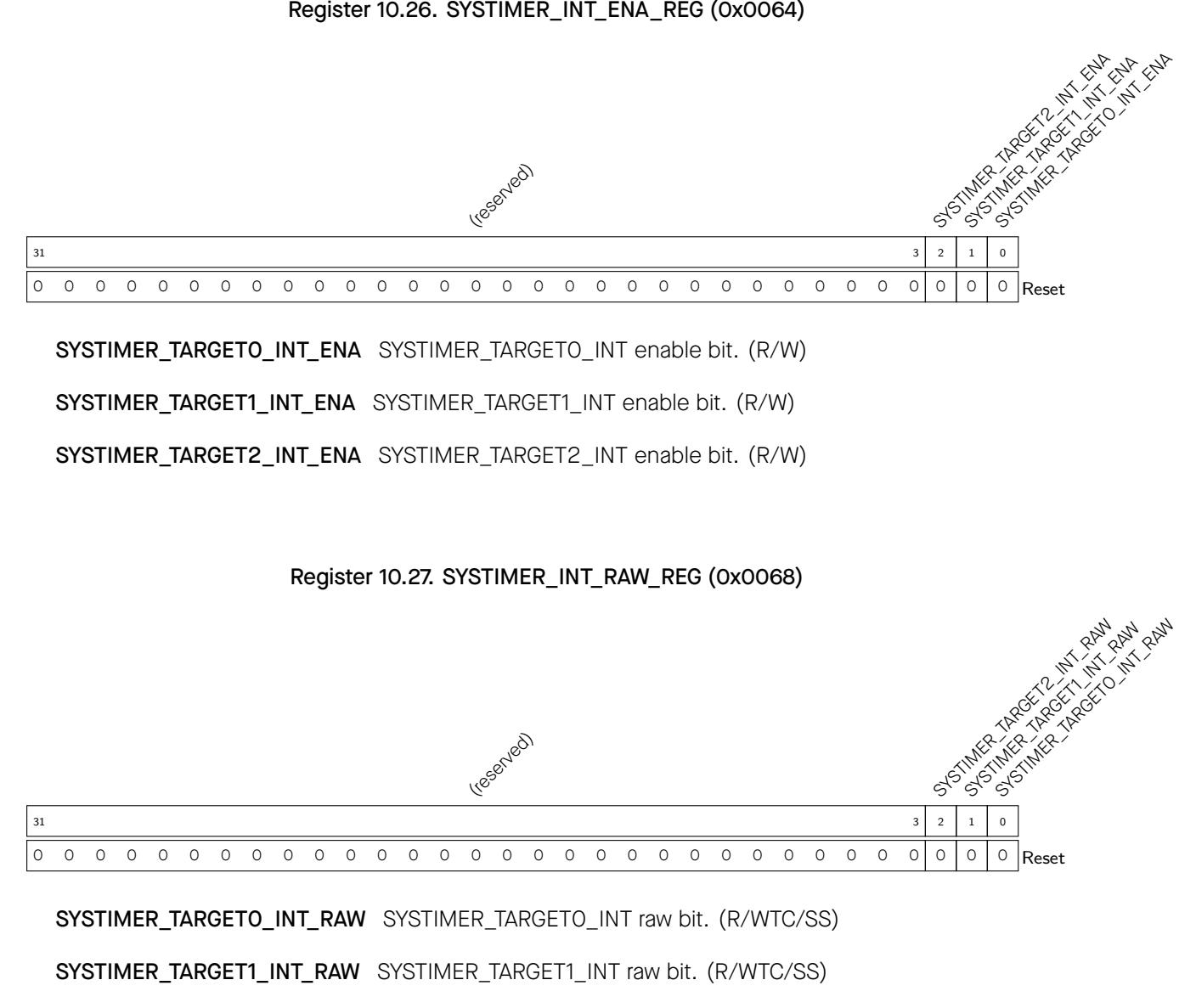

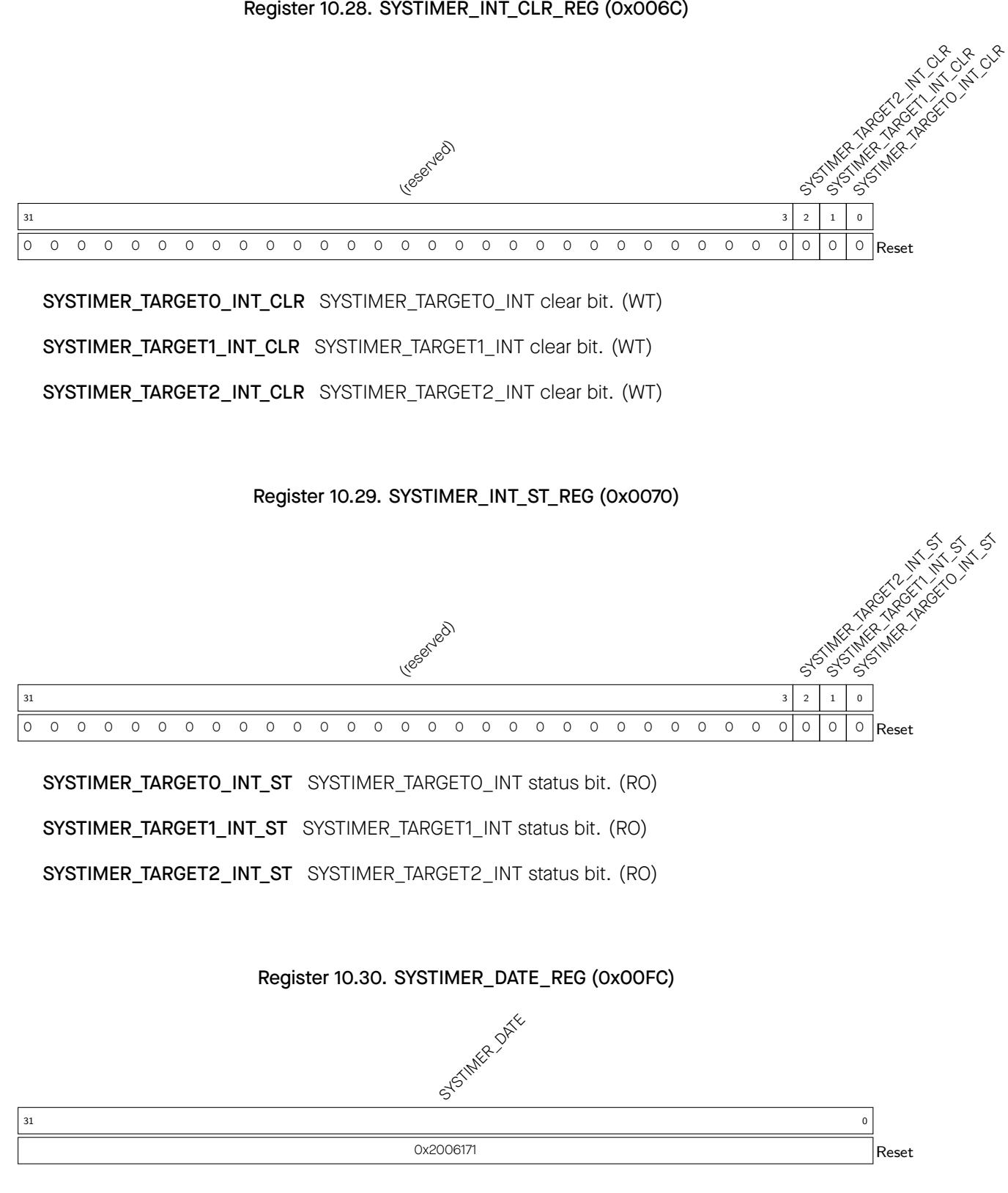

| 10 | System Timer (SYSTIMER) | 270 |

| 10.1 | Overview | 270 |

| 10.2 | Features | 270 |

| 10.3 | Clock Source Selection | 271 |

| 10.4 | Functional Description | 271 |

|

Counter

10.4.1 |

271 | |

| 10.4.2 Comparator and Alarm | 272 | |

| 10.4.3 Synchronization Operation | 273 | |

|

10.4.4

Interrupt |

274 | |

| 10.5 | Programming Procedure | 274 |

|

10.5.1

Read Current Count Value |

274 | |

| 10.5.2 Configure One-Time Alarm in Target Mode | 274 | |

|

Configure Periodic Alarms in Period Mode

10.5.3 |

274 | |

| 10.5.4 Update After Light-sleep | 275 | |

| 10.6 | Register Summary | 275 |

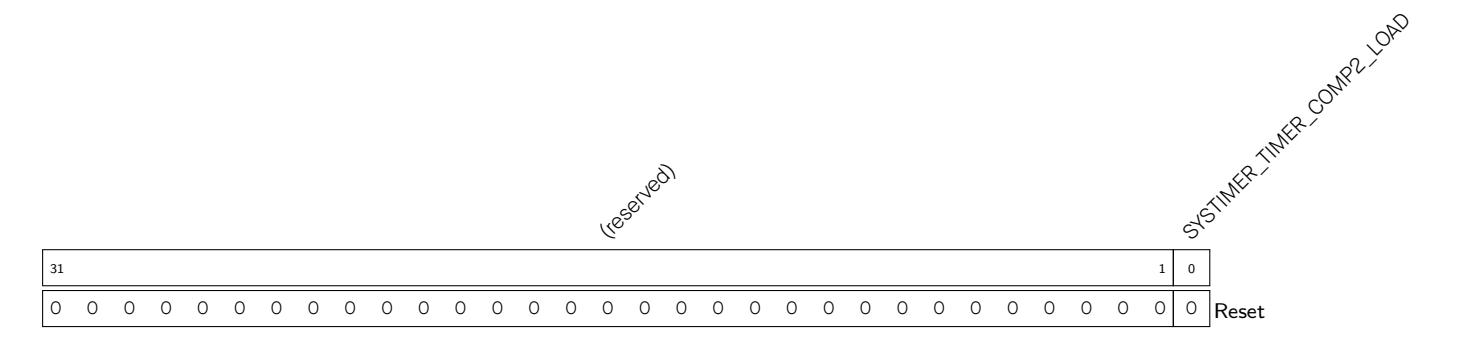

| 10.7 | Registers | 277 |

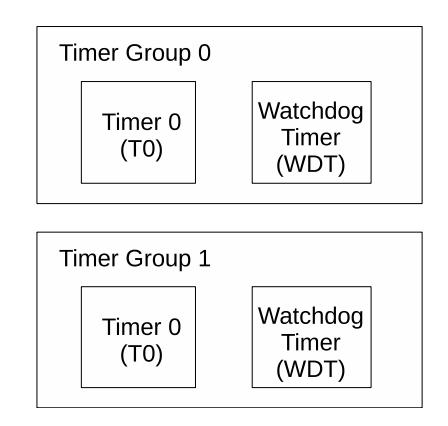

| 11 | Timer Group (TIMG) | 288 |

| 11.1 | Overview | 288 |

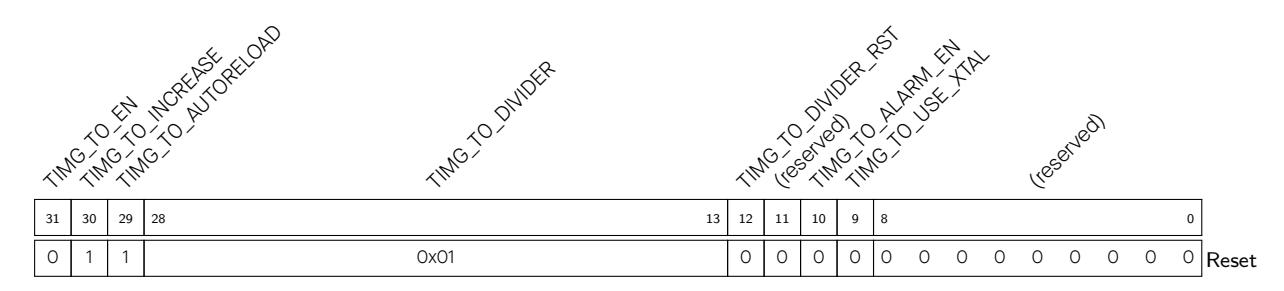

| 11.2 | Functional Description | 289 |

|

11.2.1

16-bit Prescaler and Clock Selection |

289 | |

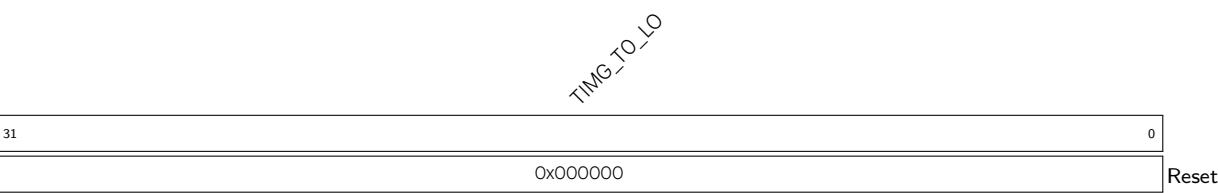

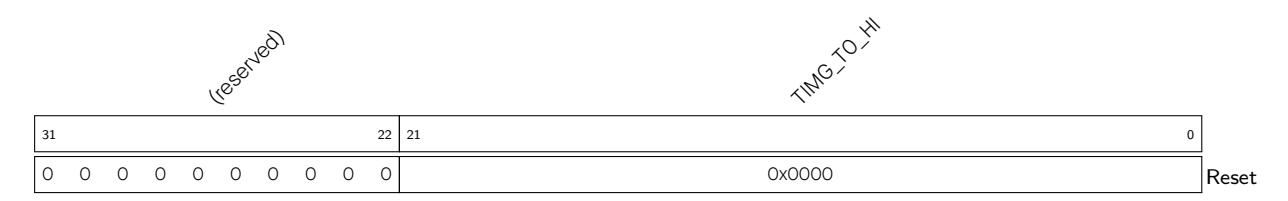

|

54-bit Time-base Counter

11.2.2 |

289 | |

|

11.2.3

Alarm Generation |

290 | |

|

11.2.4

Timer Reload |

291 | |

|

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

11.2.5 |

291 | |

|

11.2.6

Interrupts |

291 | |

| 11.3 | Configuration and Usage | 292 |

|

11.3.1

Timer as a Simple Clock |

292 | |

|

11.3.2

Timer as One-shot Alarm |

292 | |

|

Timer as Periodic Alarm

11.3.3 |

293 | |

|

11.3.4

RTC_SLOW_CLK Frequency Calculation |

293 | |

| 11.4 | Register Summary | 294 |

| 11.5 | Registers | 295 |

| 12 | Watchdog Timers (WDT) | 305 |

| 12.1 | Overview | 305 |

| 12.2 | Digital Watchdog Timers | 306 |

|

12.2.1

Features |

306 | |

| 12.2.2 Functional Description | 307 | |

|

Clock Source and 32-Bit Counter

12.2.2.1 |

307 | |

| 12.2.2.2 Stages and Timeout Actions | 308 | |

| Contents | GoBack | |

|

12.2.2.3

Write Protection |

308 | |

|

12.2.2.4

Flash Boot Protection |

309 | |

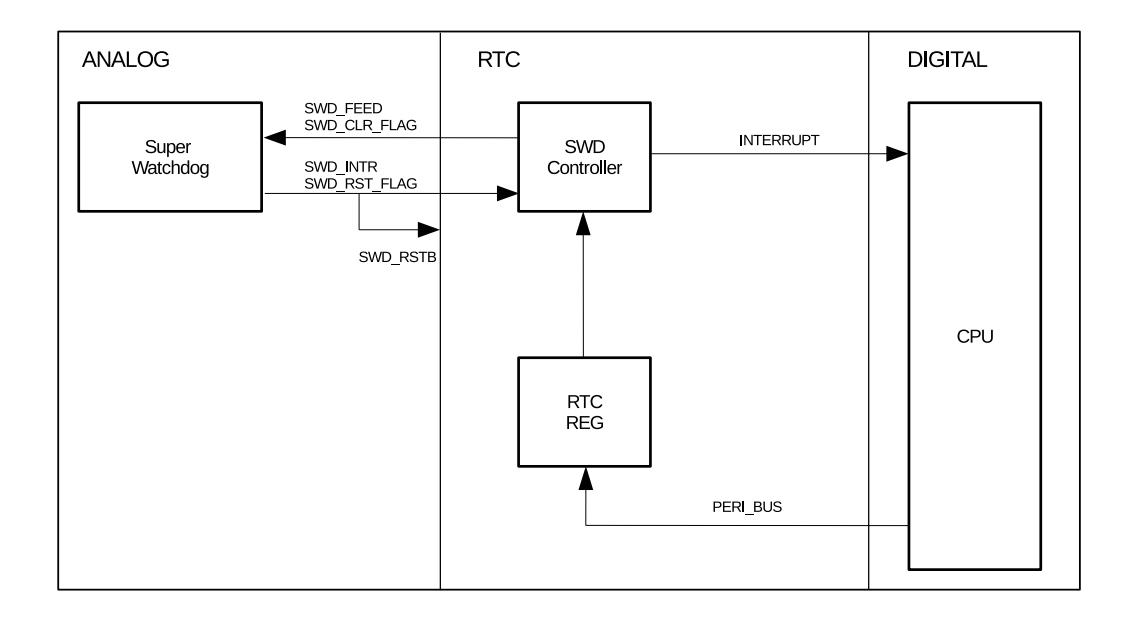

| 12.3 | Super Watchdog | 309 |

|

12.3.1

Features |

309 | |

|

12.3.2

Super Watchdog Controller |

309 | |

|

12.3.2.1

Structure 12.3.2.2 Workflow |

310

310 |

|

| 12.4 | Interrupts | 310 |

| 12.5 | Registers | |

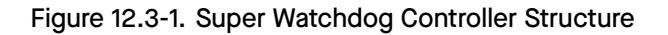

| 13 | XTAL32K Watchdog Timers (XTWDT) | 312 |

| 13.1 | Overview | 312 |

| 13.2 | Features | 312 |

|

13.2.1

Interrupt and Wake-Up |

312 | |

|

13.2.2

BACKUP32K_CLK |

313 | |

| 13.3 | Functional Description | 313 |

|

13.3.1

Workflow 13.3.2 BACKUP32K_CLK Working Principle |

313

313 |

|

|

13.3.3

Configuring the Divisor Component of BACKUP32K_CLK |

313 | |

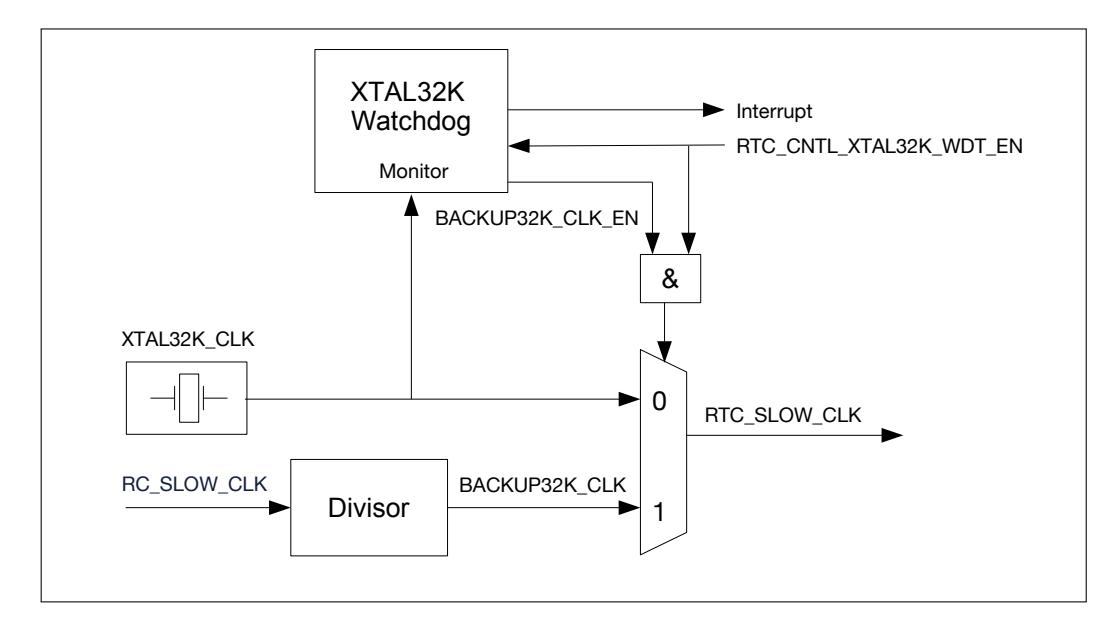

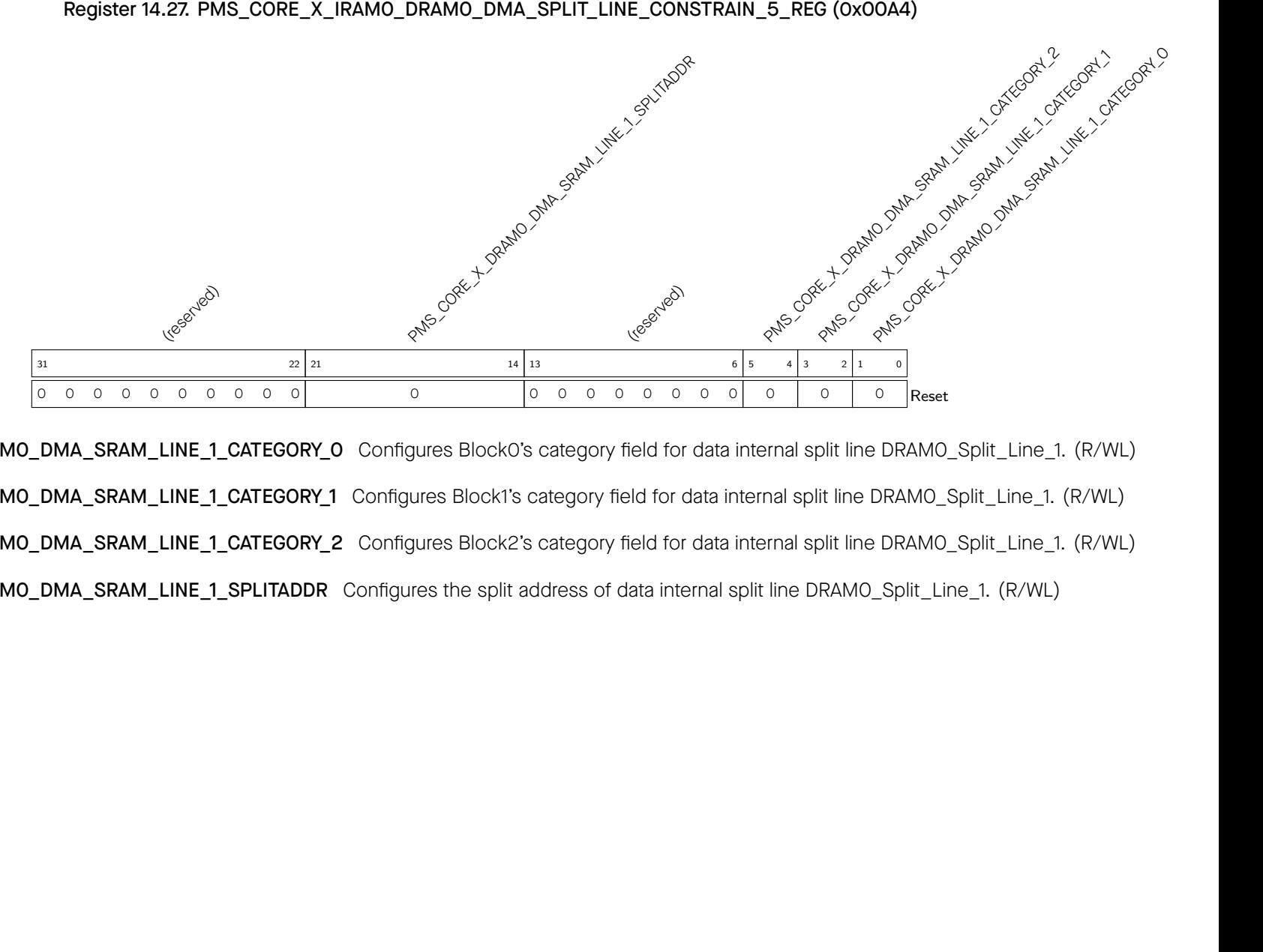

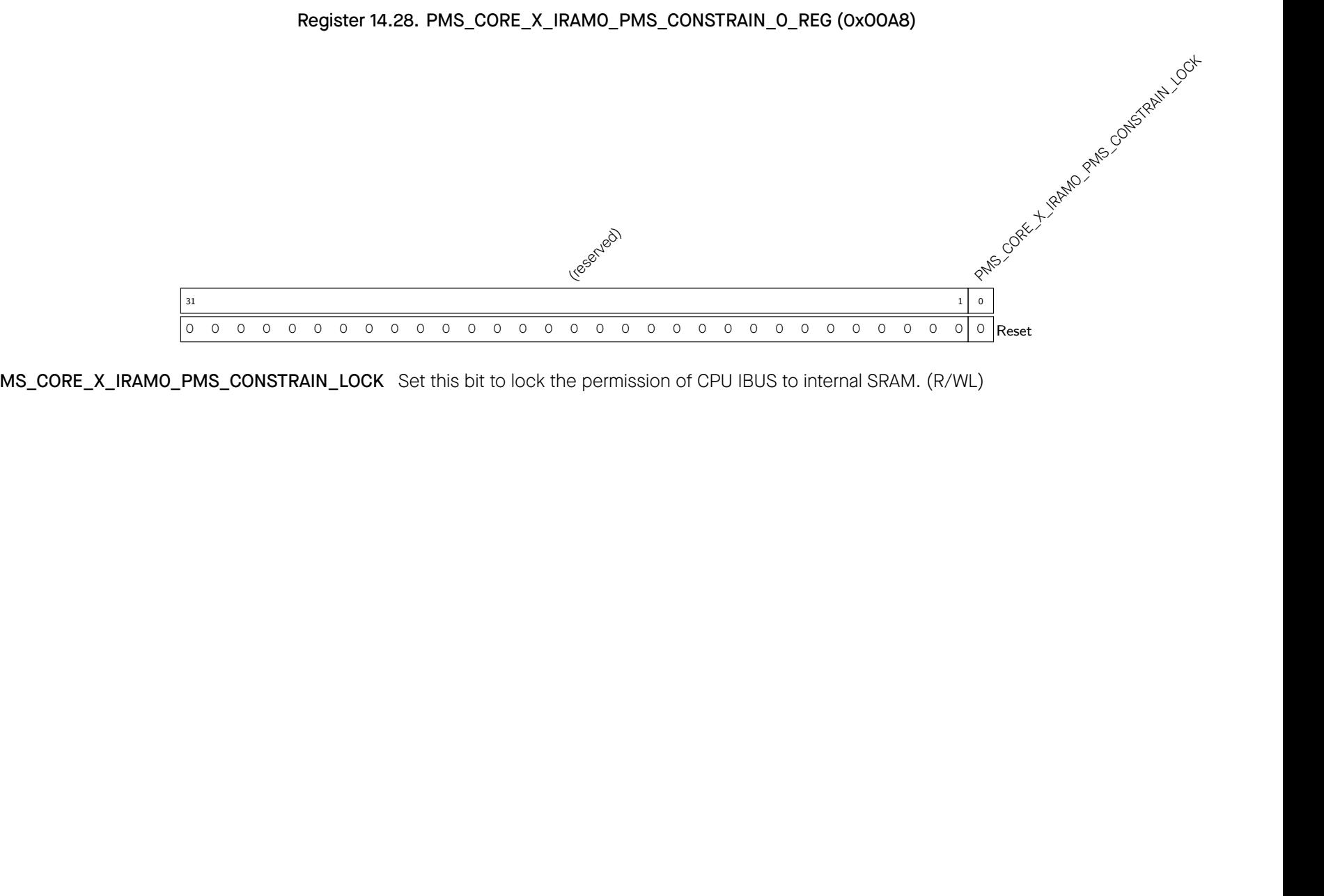

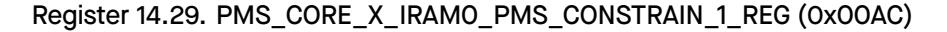

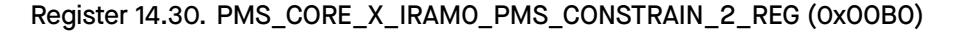

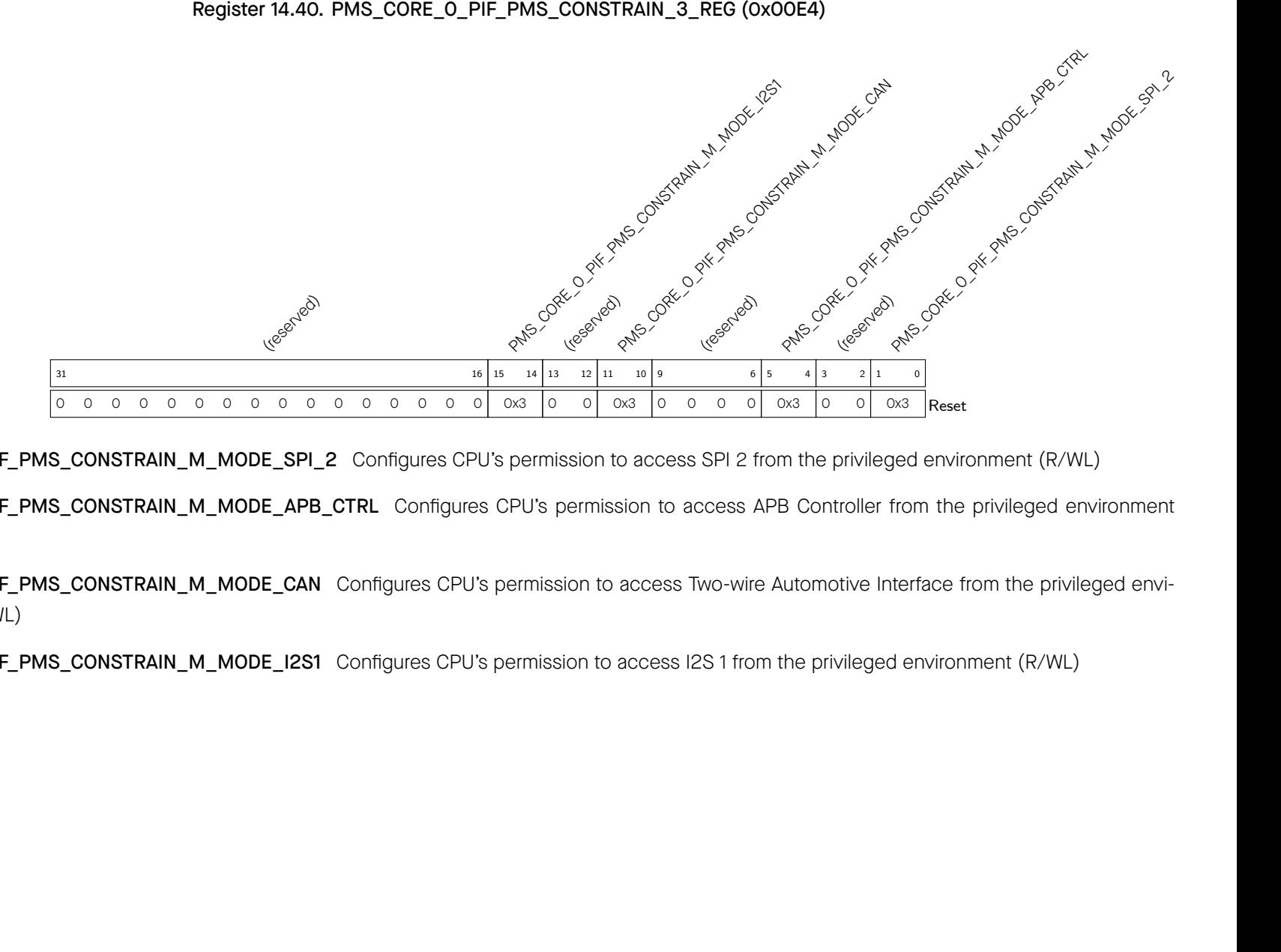

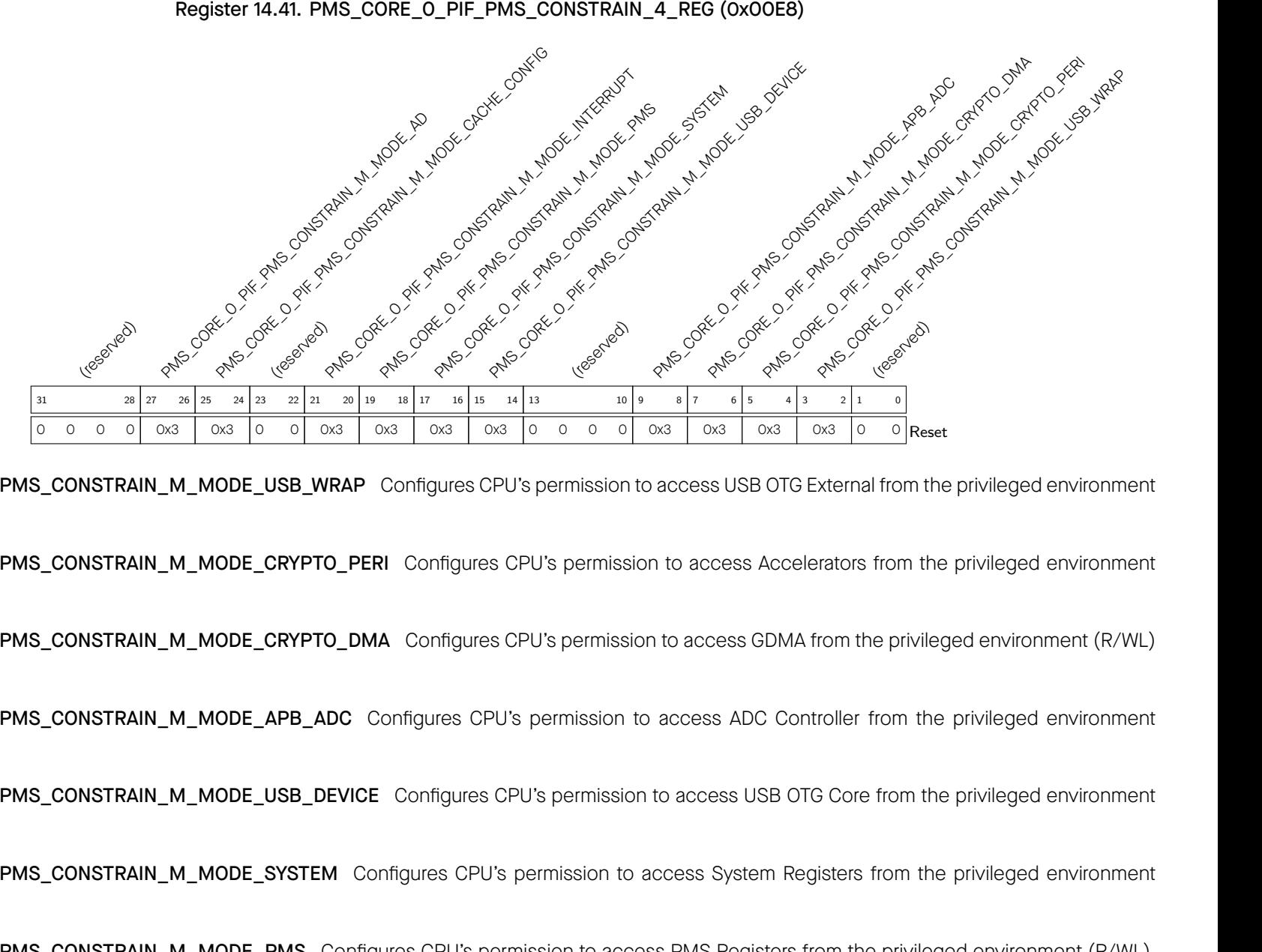

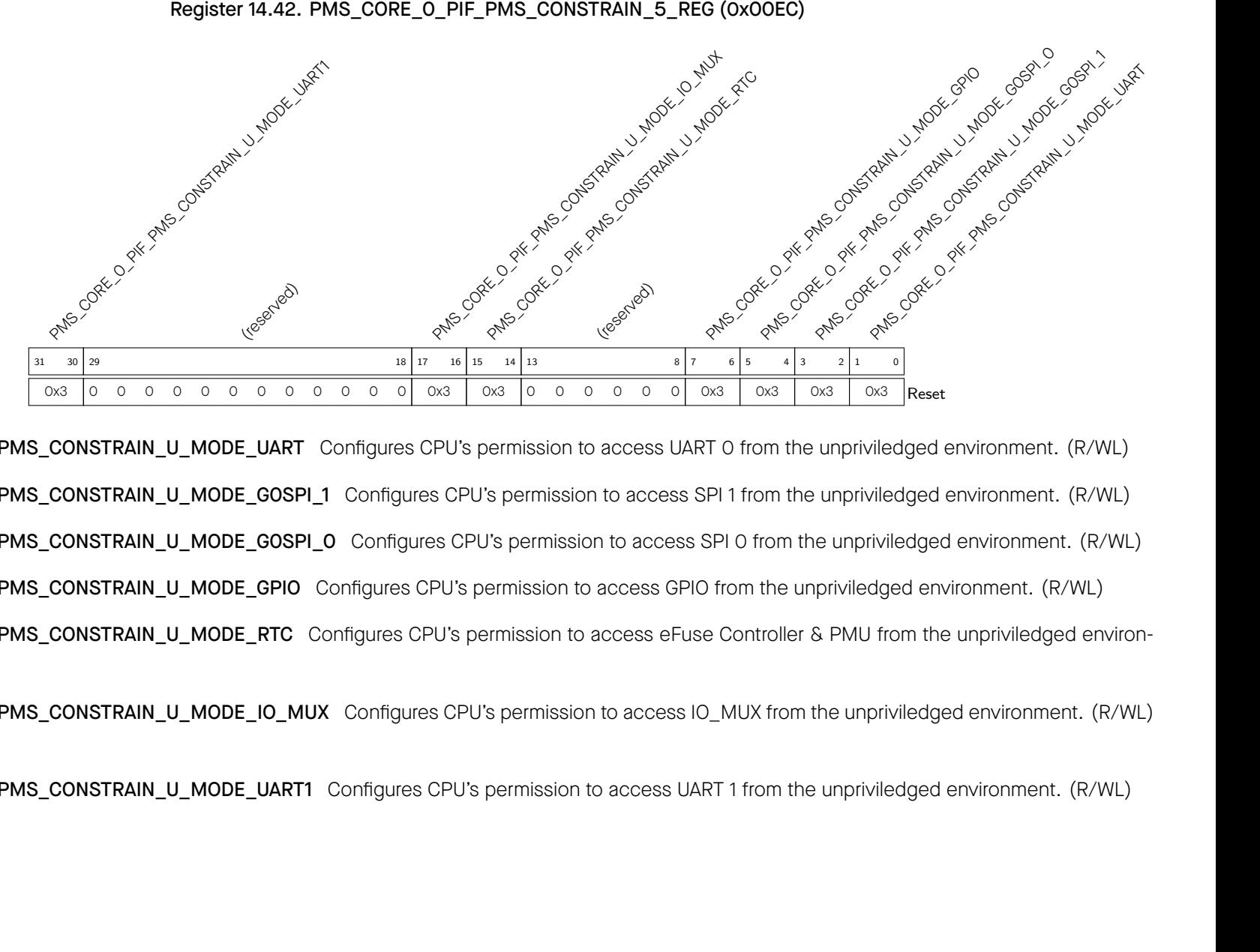

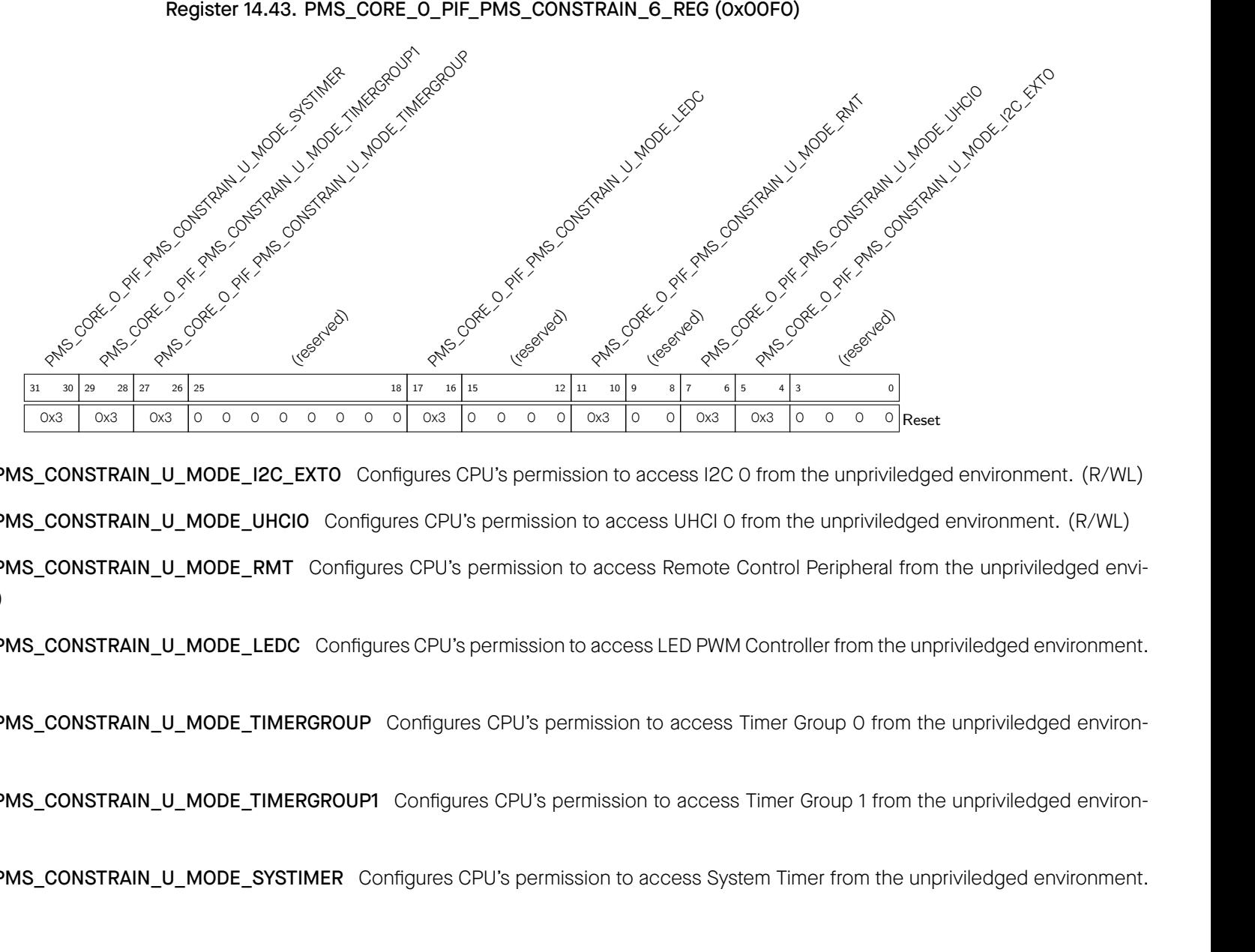

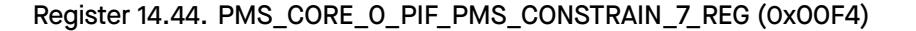

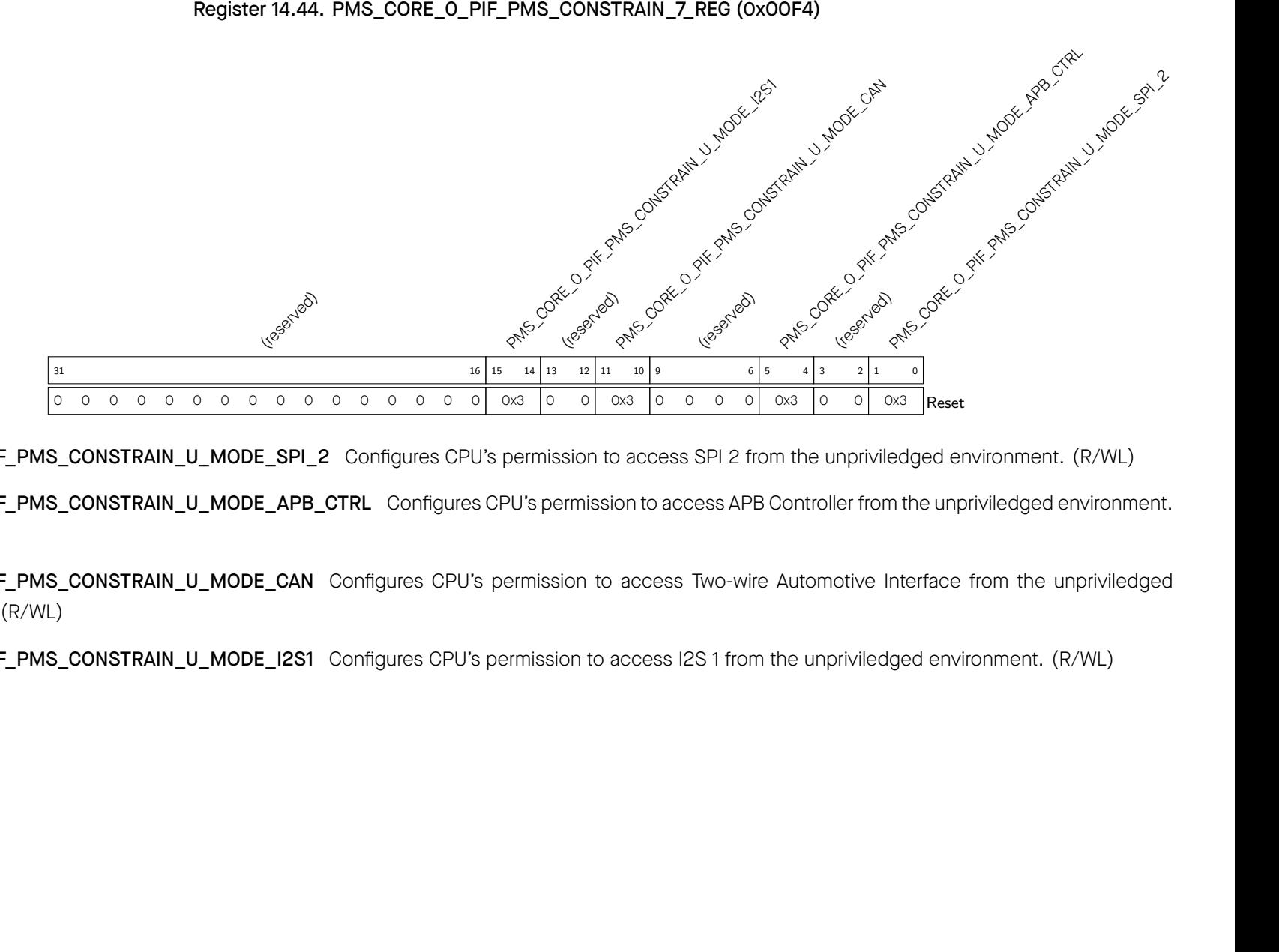

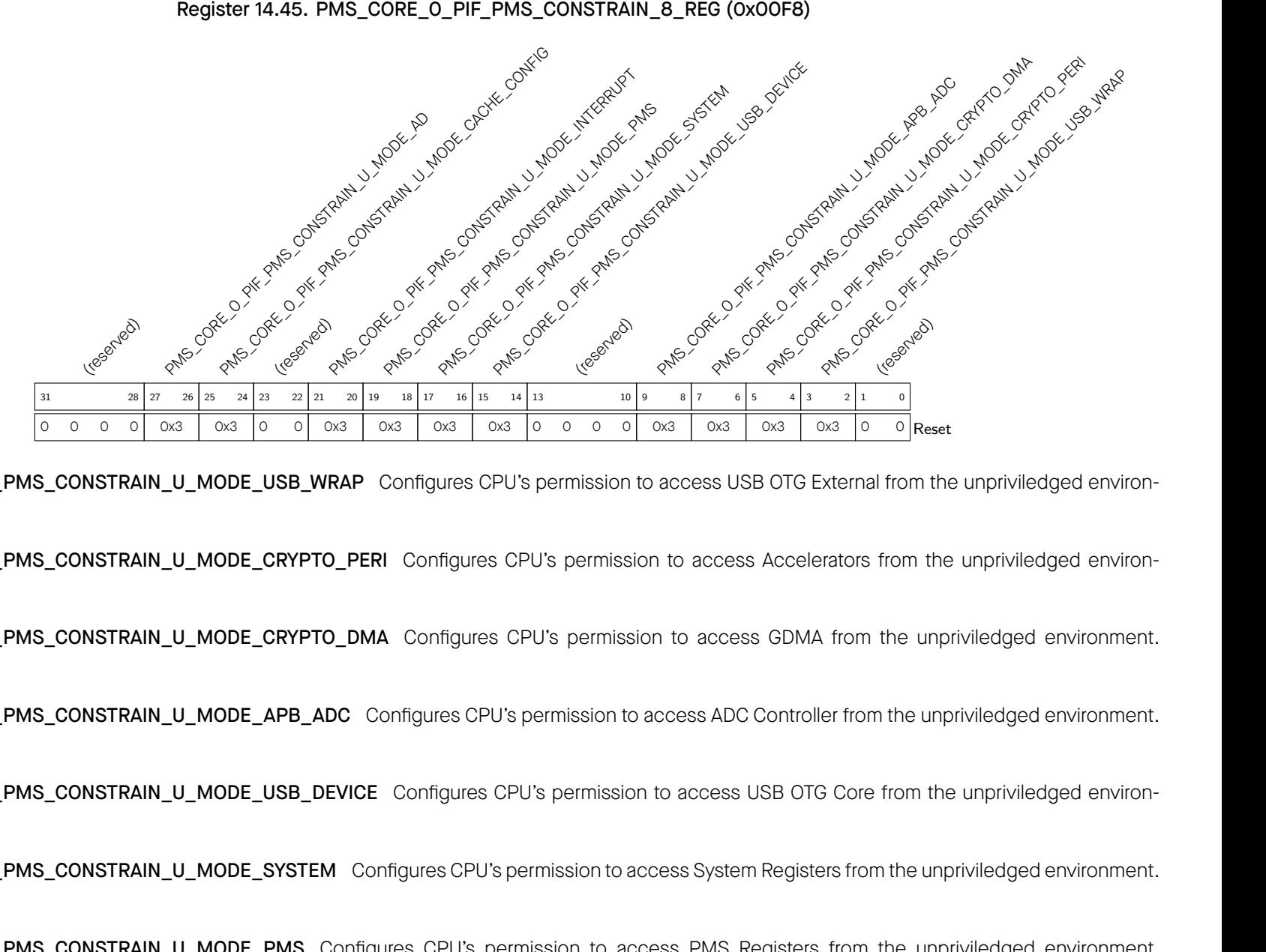

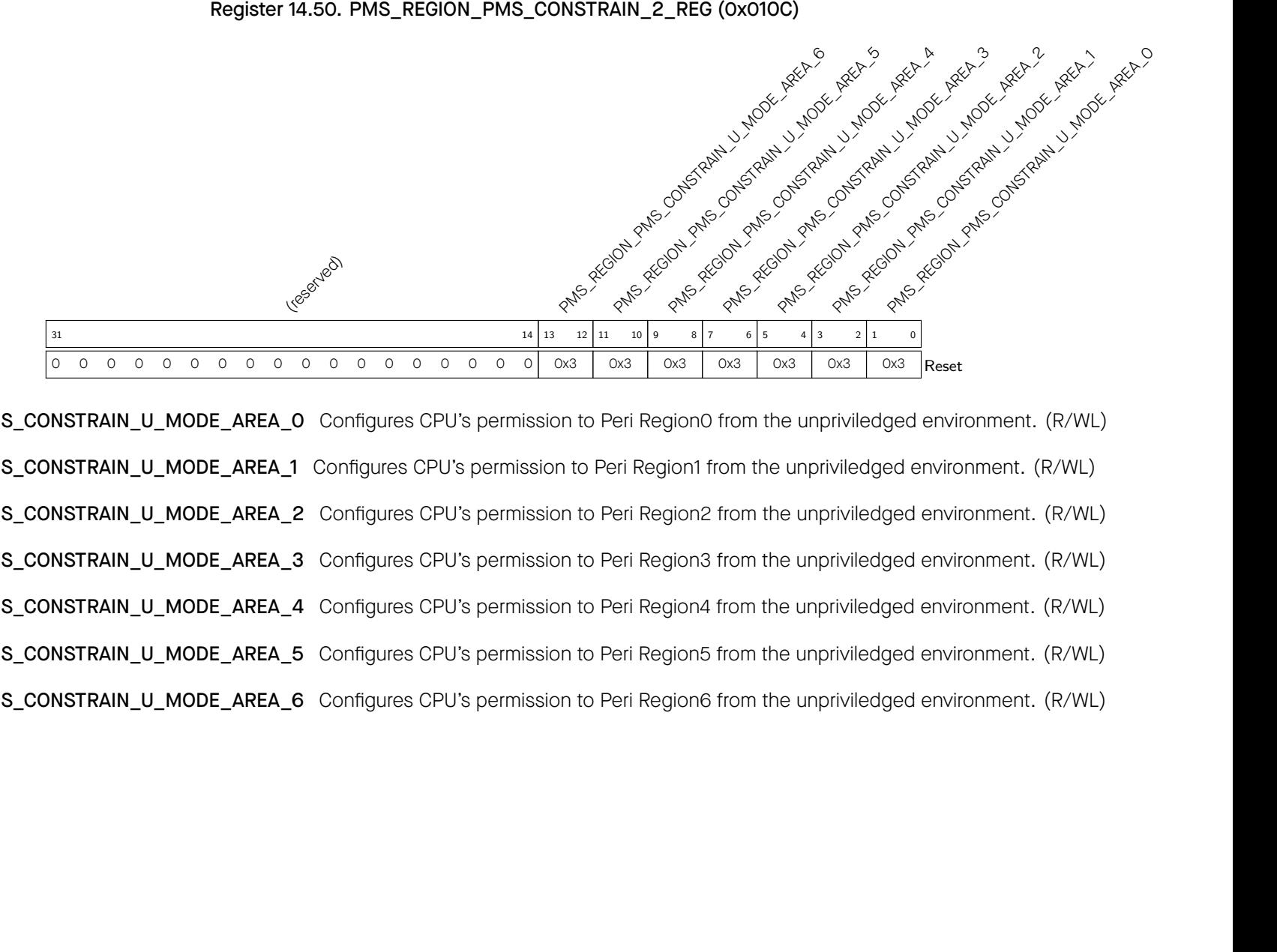

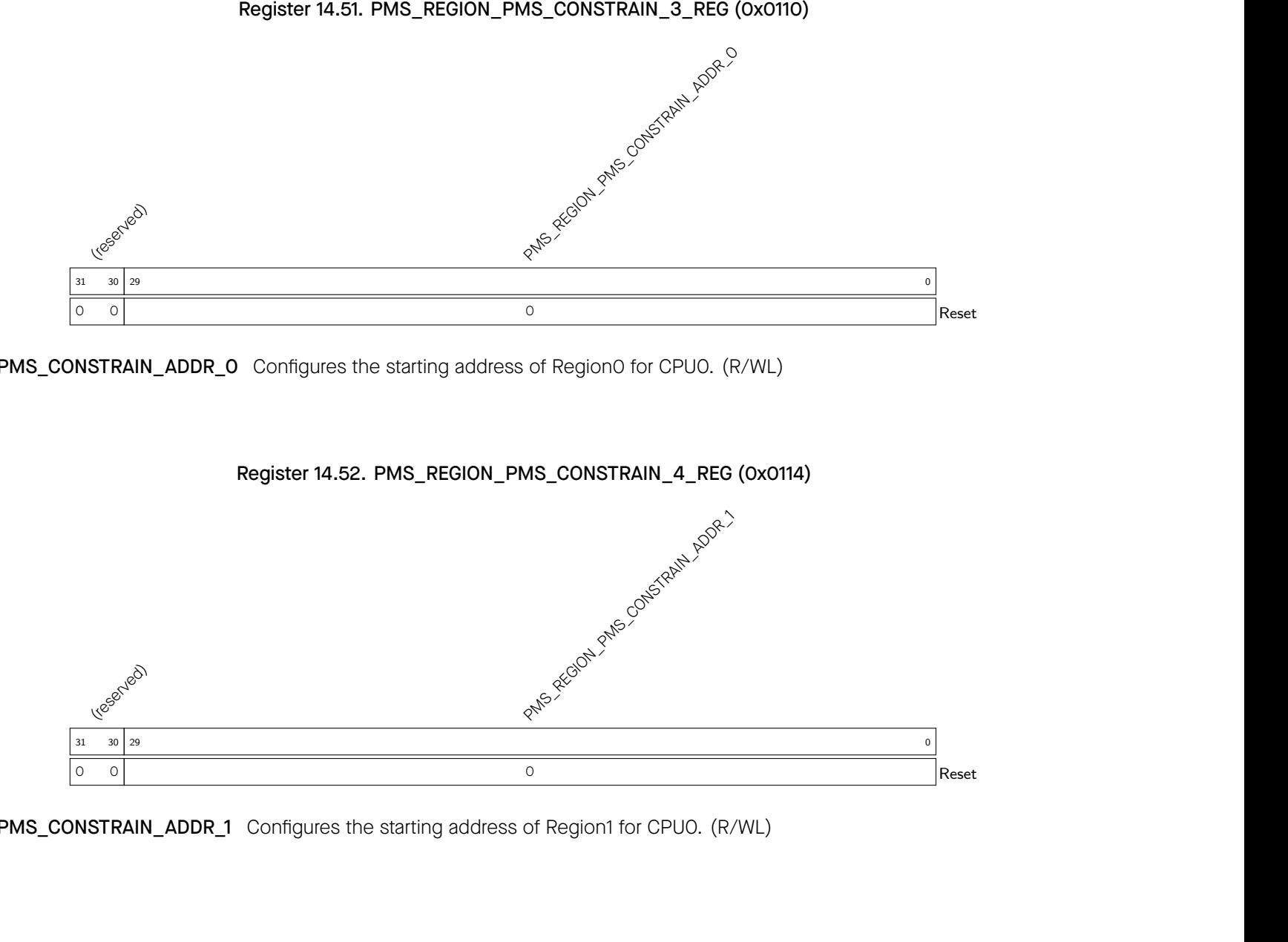

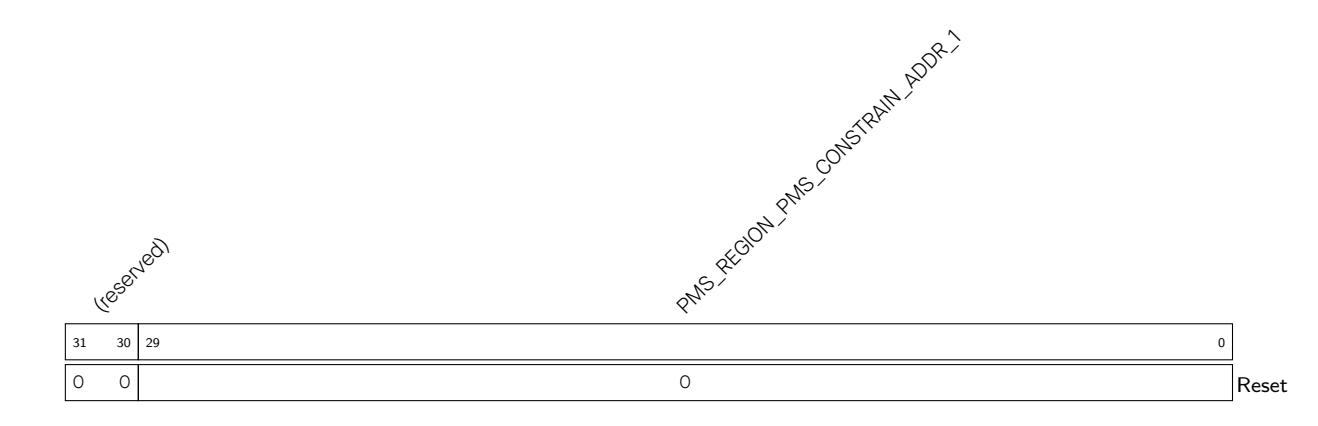

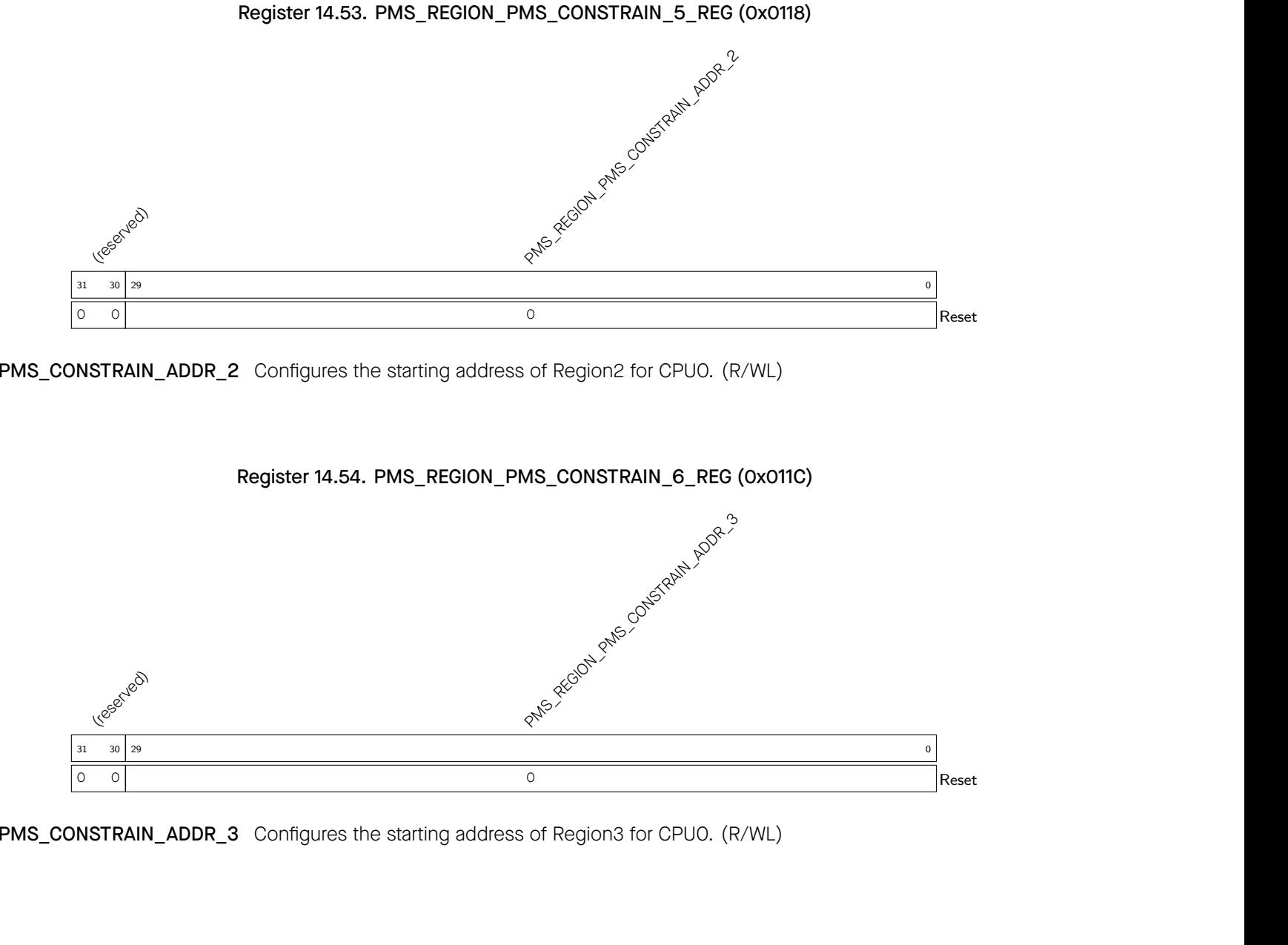

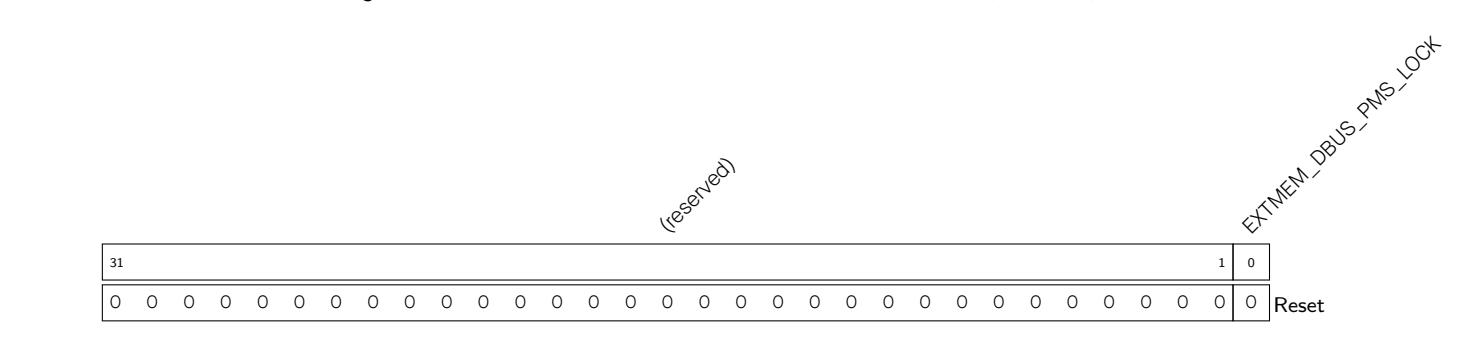

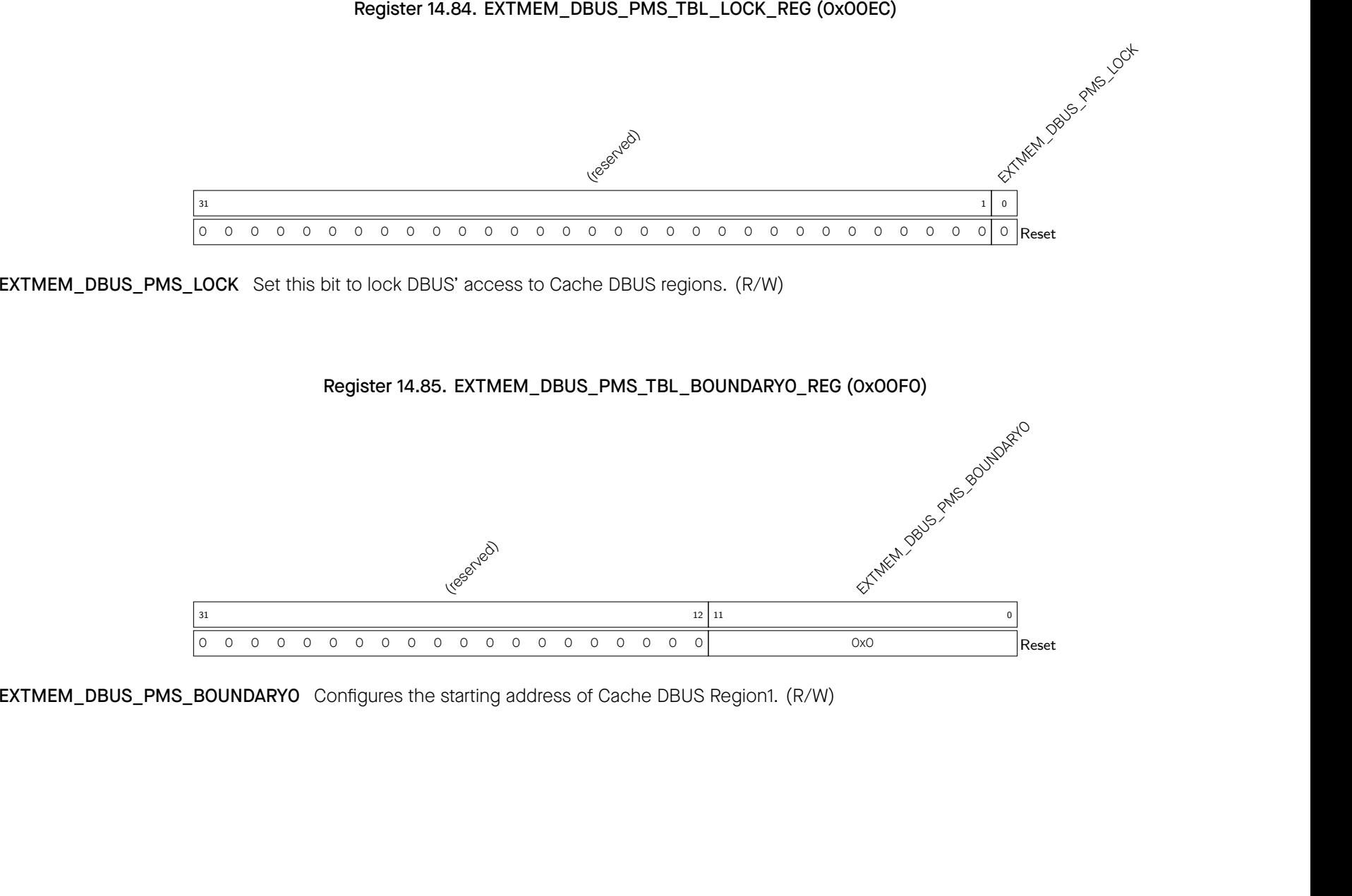

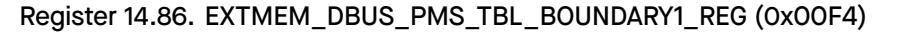

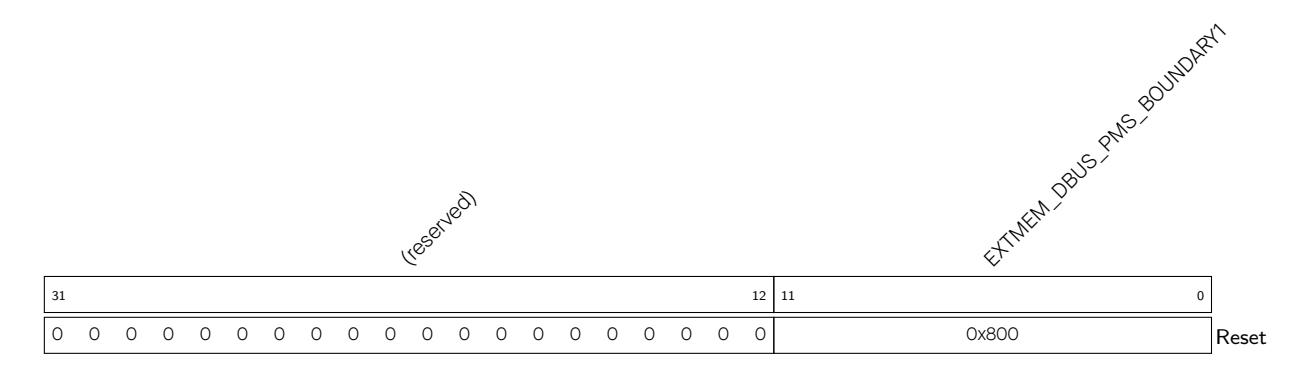

| 14 | Permission Control (PMS) | 315 |

| 14.1 | Overview | 315 |

| 14.2 | Features | 316 |

| 14.3 | Privileged Environment and Unprivileged Environment | 316 |

| 14.4 |

Internal Memory

14.4.1 ROM |

317

317 |

|

14.4.2

SRAM |

318 | |

|

14.4.2.1

Internal SRAM0 Access Configuration |

318 | |

|

14.4.2.2

Internal SRAM1 Access Configuration |

319 | |

|

14.4.3

RTC FAST Memory |

322 | |

| 14.5 | Peripherals | 323 |

|

14.5.1

Access Configuration |

323 | |

|

14.5.2

Split Peripheral Regions into Split Regions |

324 | |

| 14.6 | External Memory | 325 |

|

14.6.1

SPI and Cache's Access to External Flash |

325 | |

|

14.6.1.1

Address |

326 | |

|

14.6.1.2

Access Configuration |

326 | |

|

14.6.2

CPU's Access to Cache |

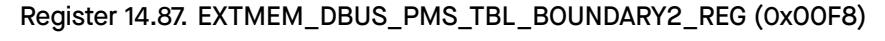

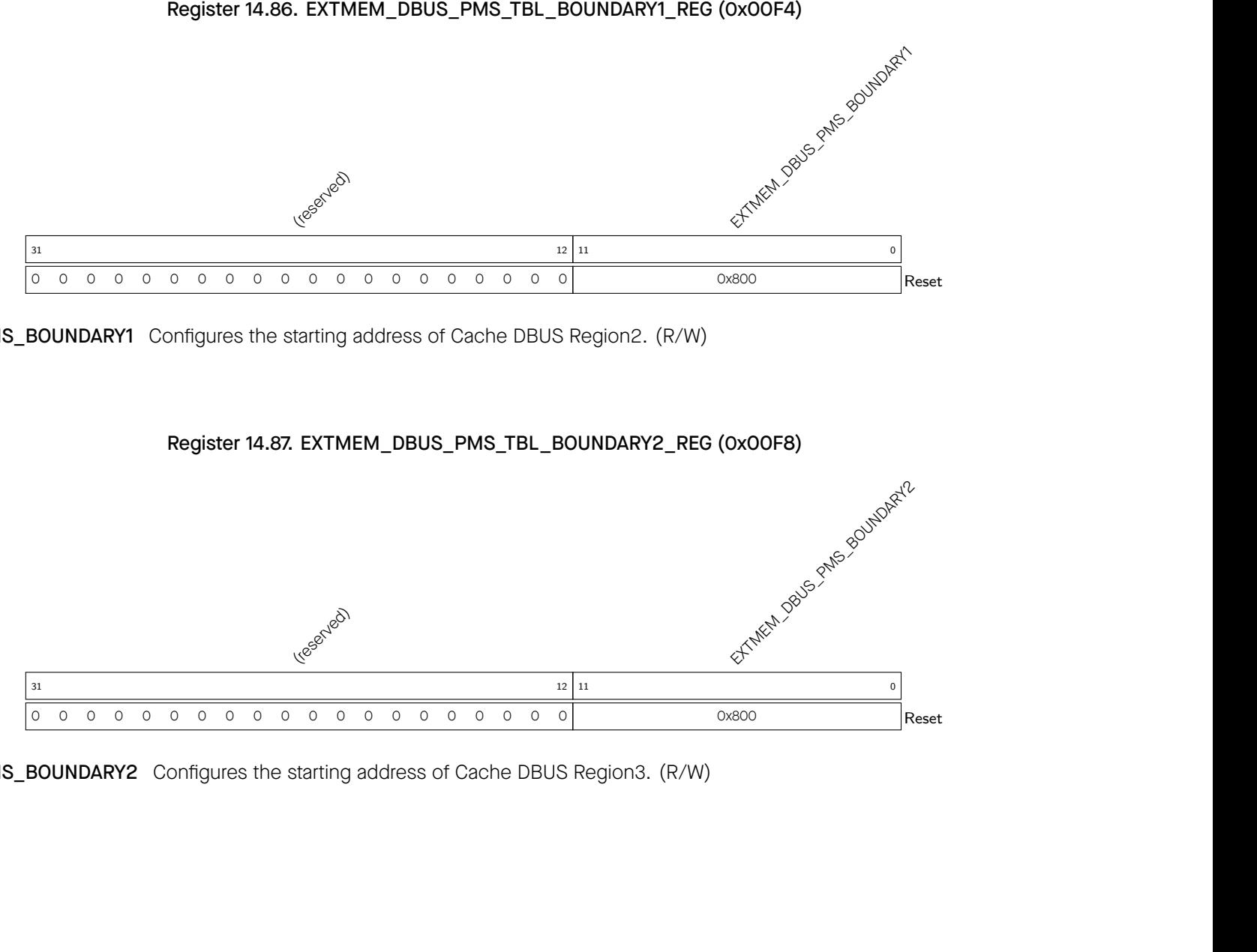

327 | |

|

14.6.2.1

Split Regions |

327 | |

|

14.6.3

Access Configuration |

327 | |

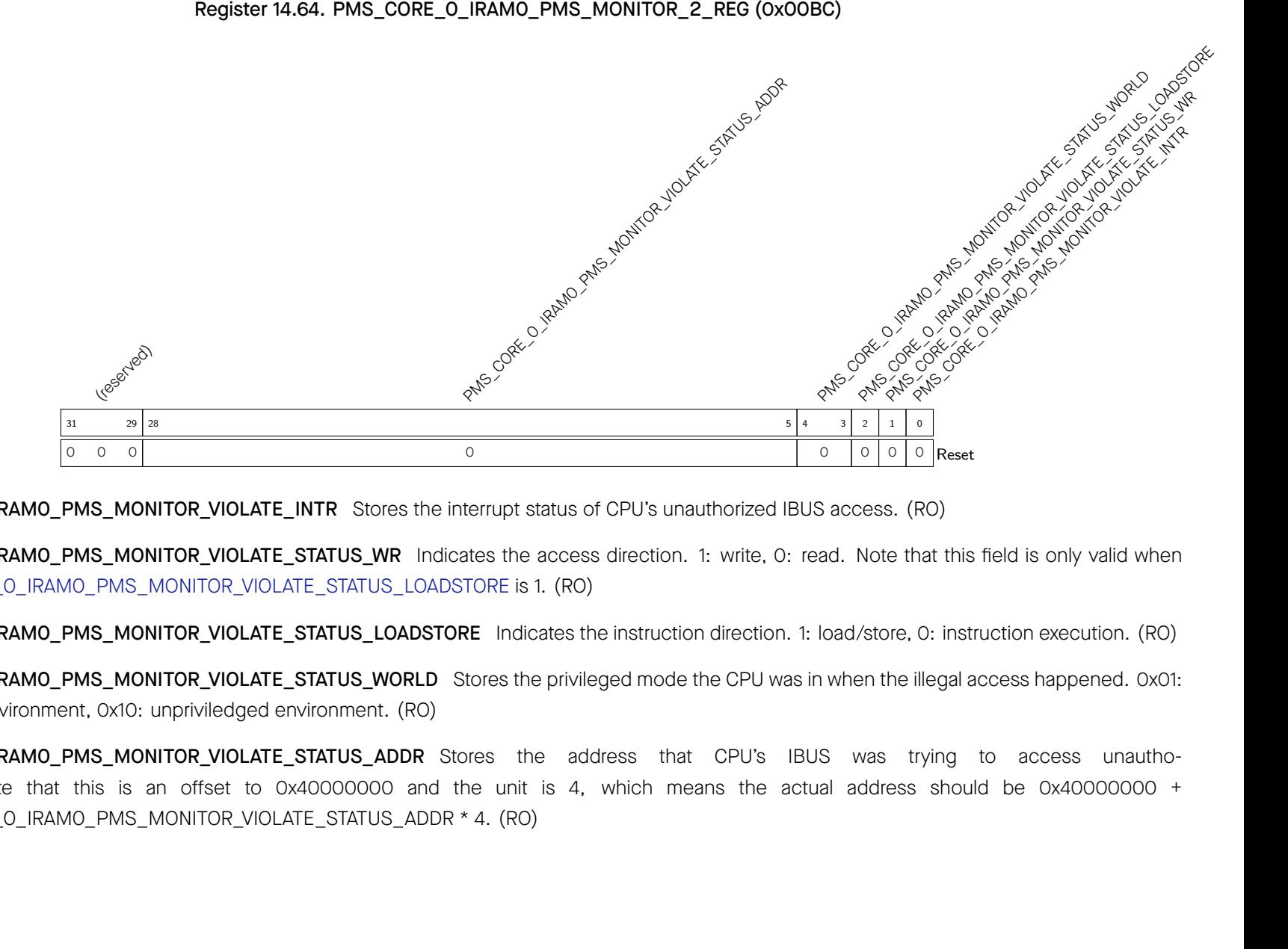

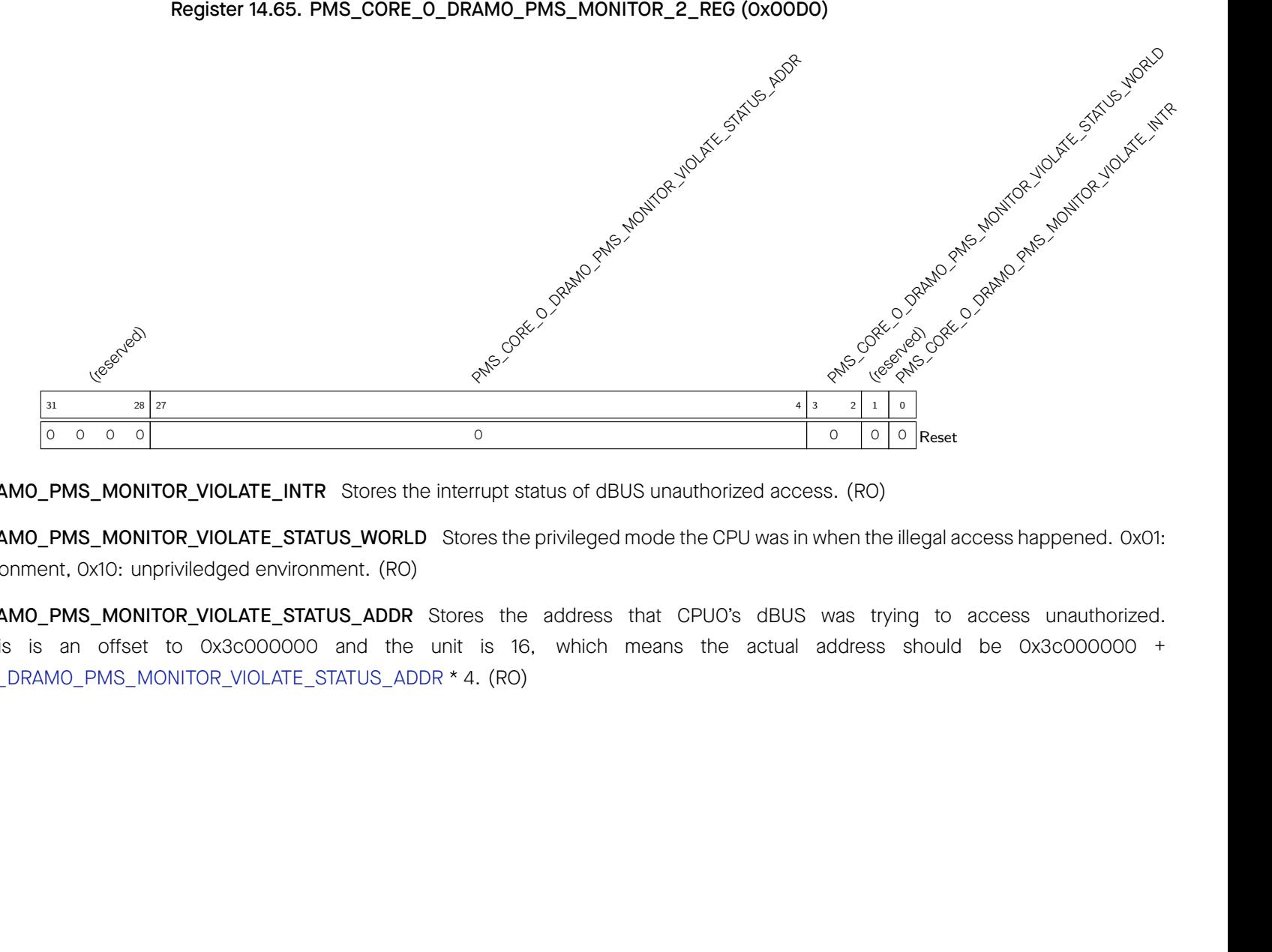

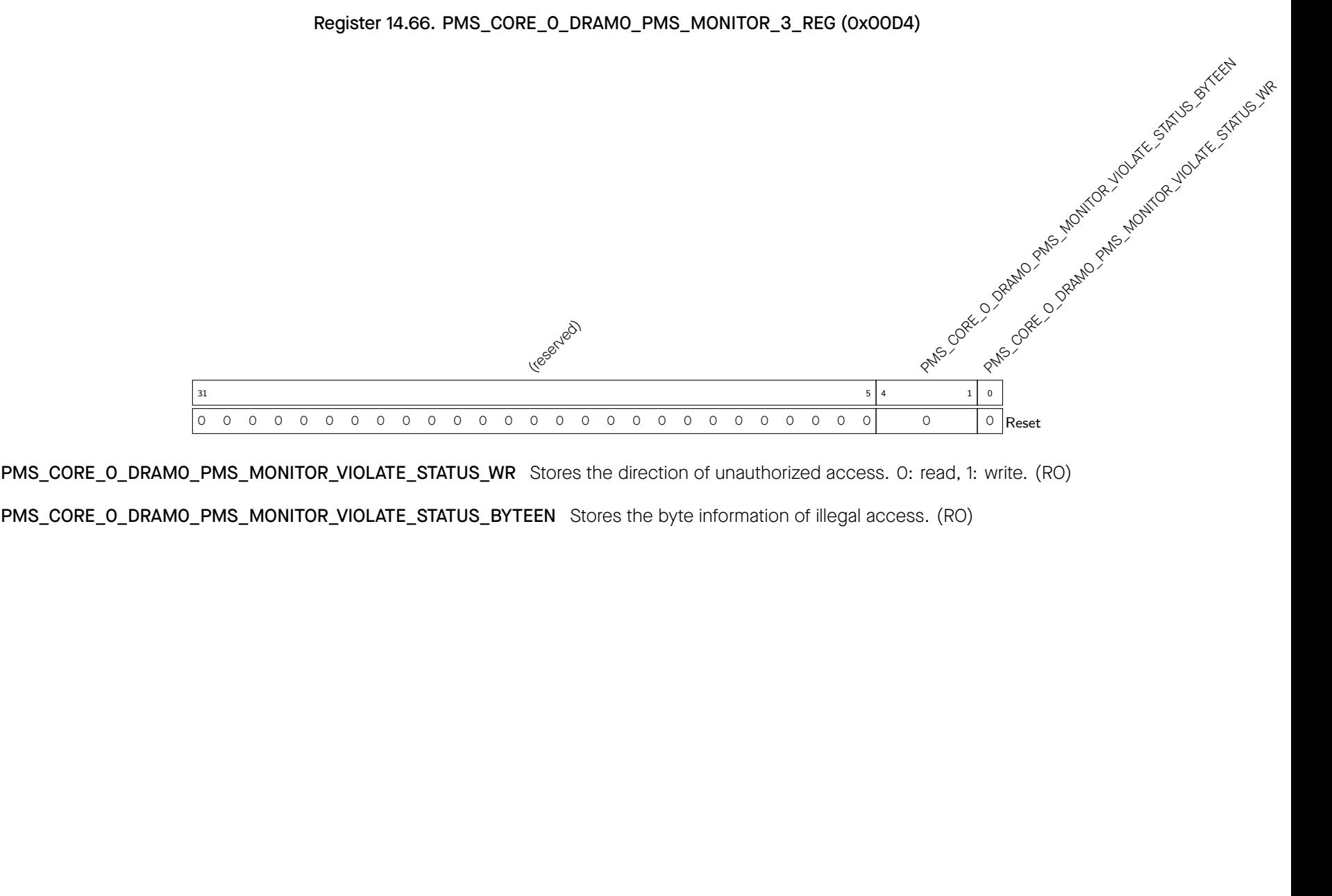

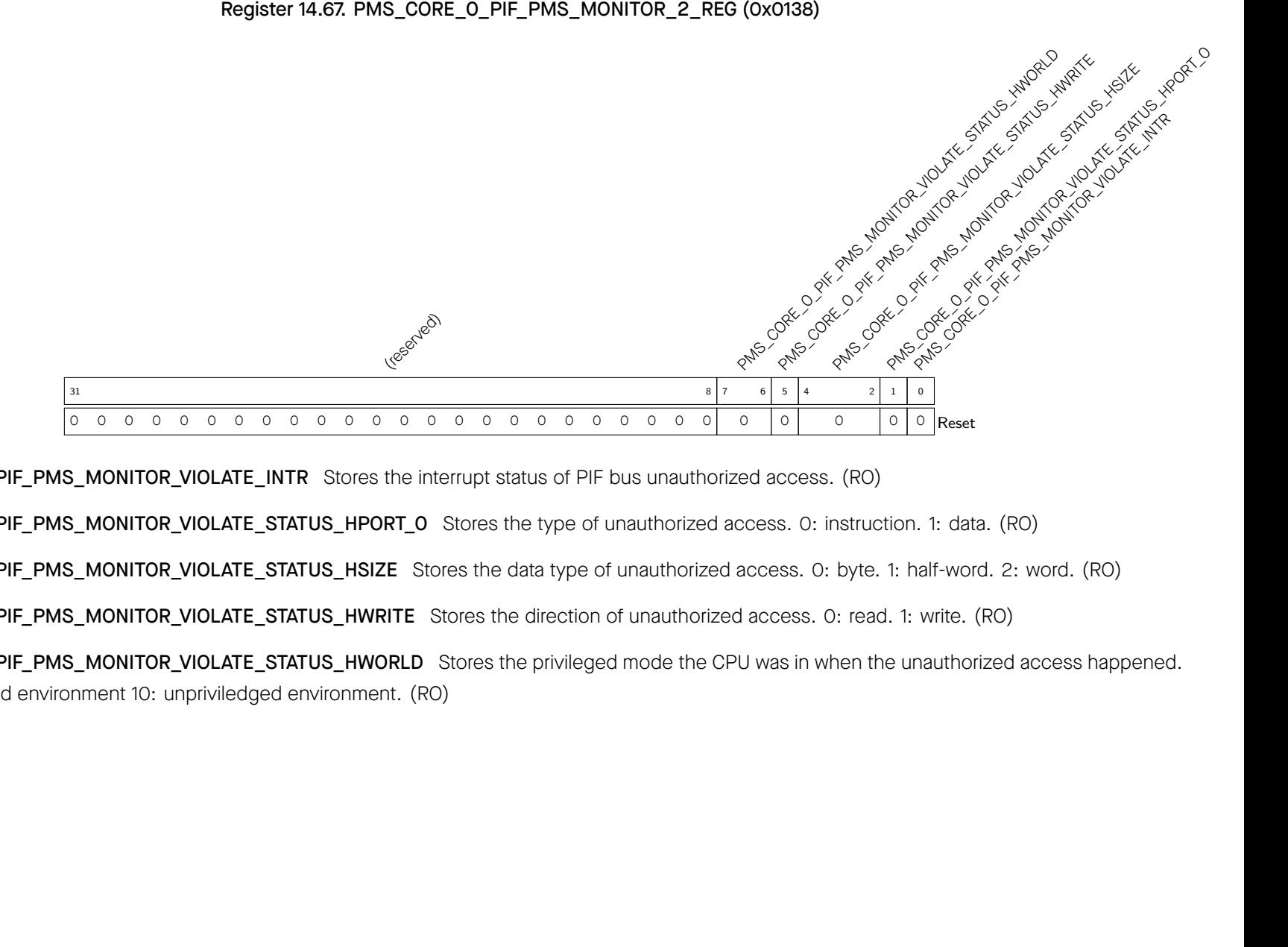

| 14.7 |

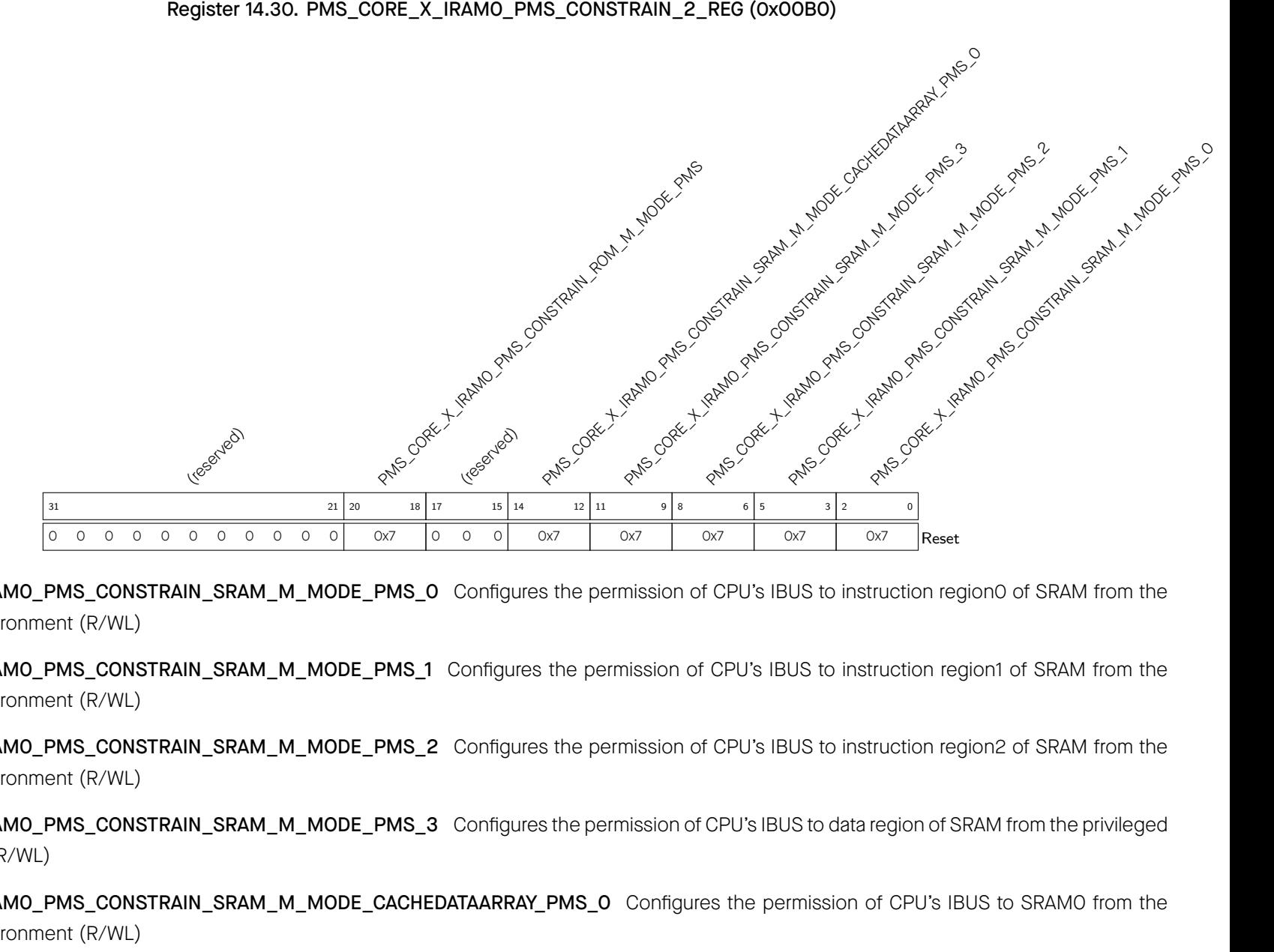

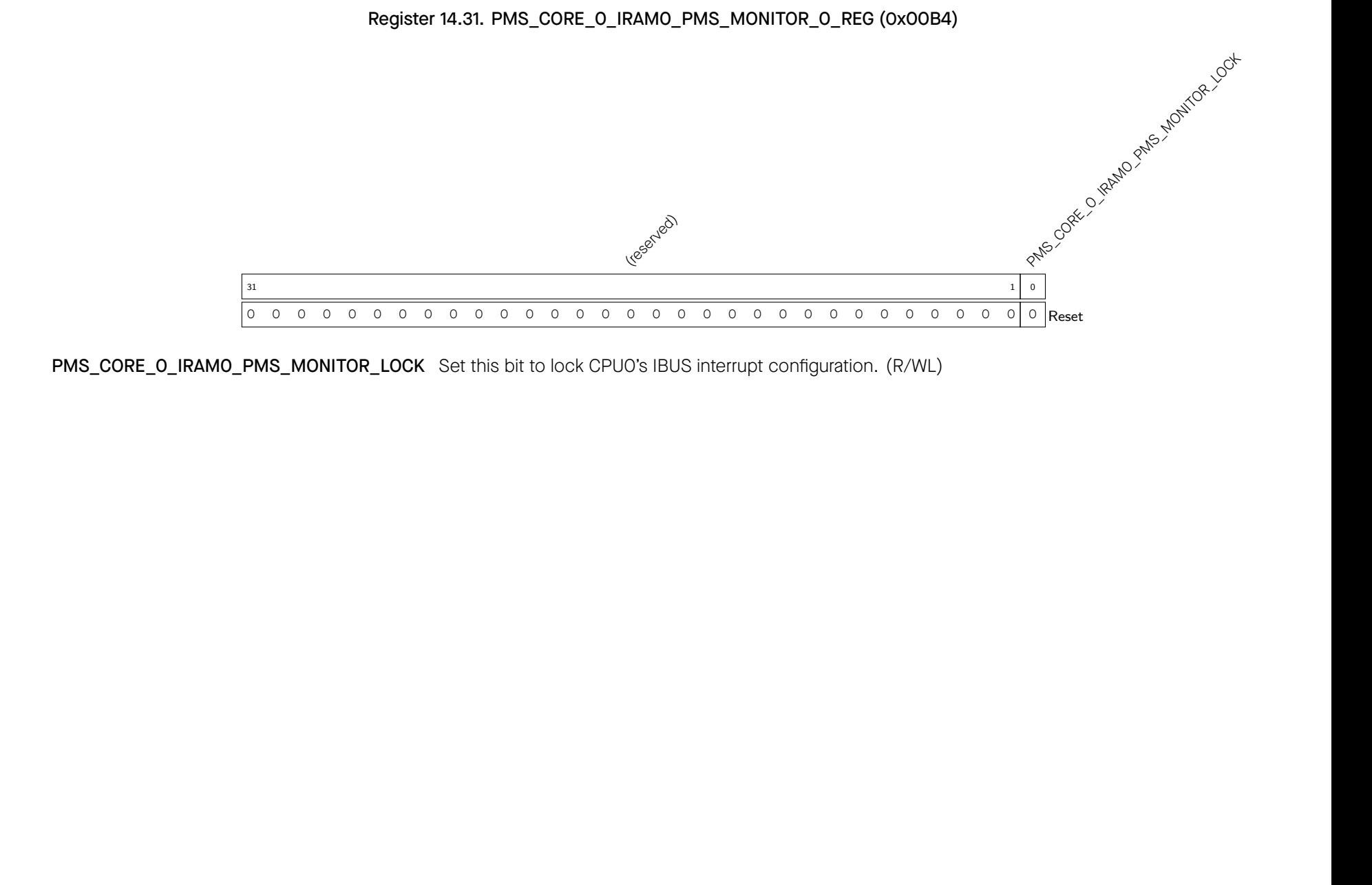

Unauthorized Access and Interrupts

14.7.1 Interrupt upon Unauthorized IBUS Access |

328

329 |

|

14.7.2

Interrupt upon Unauthorized DBUS Access |

329 | |

|

14.7.3

Interrupt upon Unauthorized Access to External Memory |

330 | |

|

14.7.4

Interrupt upon Unauthorized Access to Internal Memory via GDMA |

330 | |

| Contents | GoBack | |

|

14.7.6

Interrupt upon Unauthorized PIF Access Alignment |

331 | |

| 14.8 | Register Locks | 332 |

| 14.9 | Register Summary | 335 |

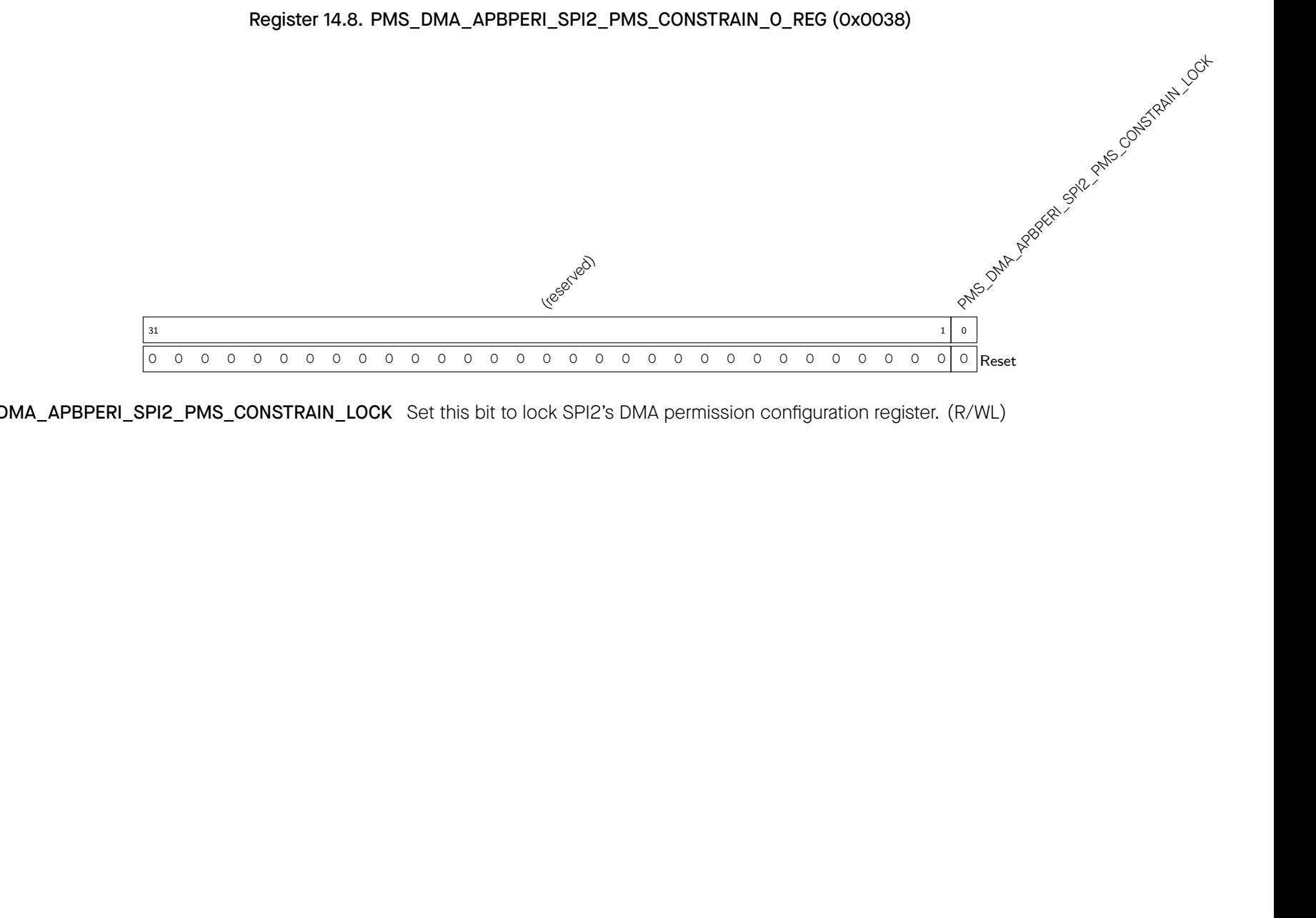

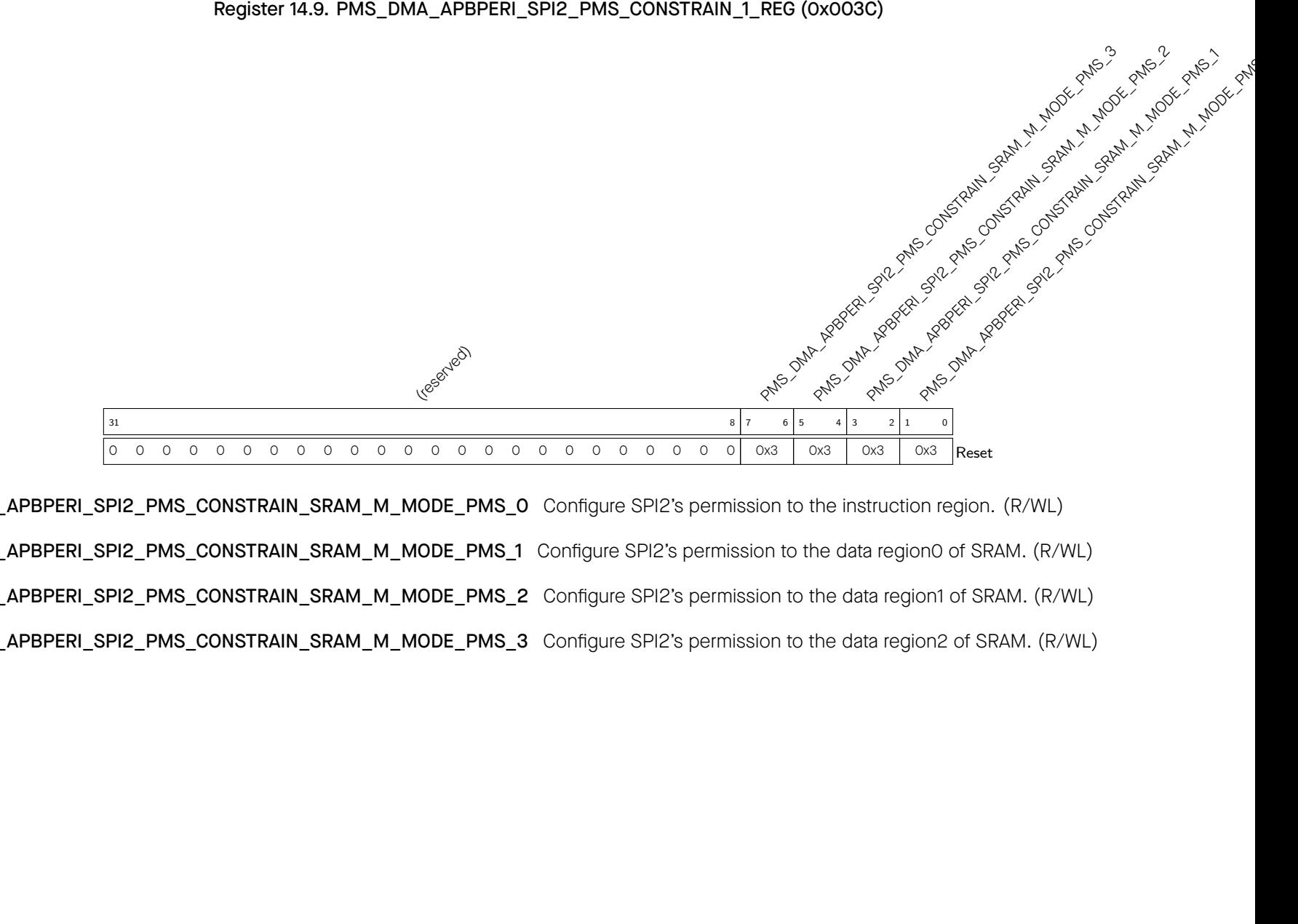

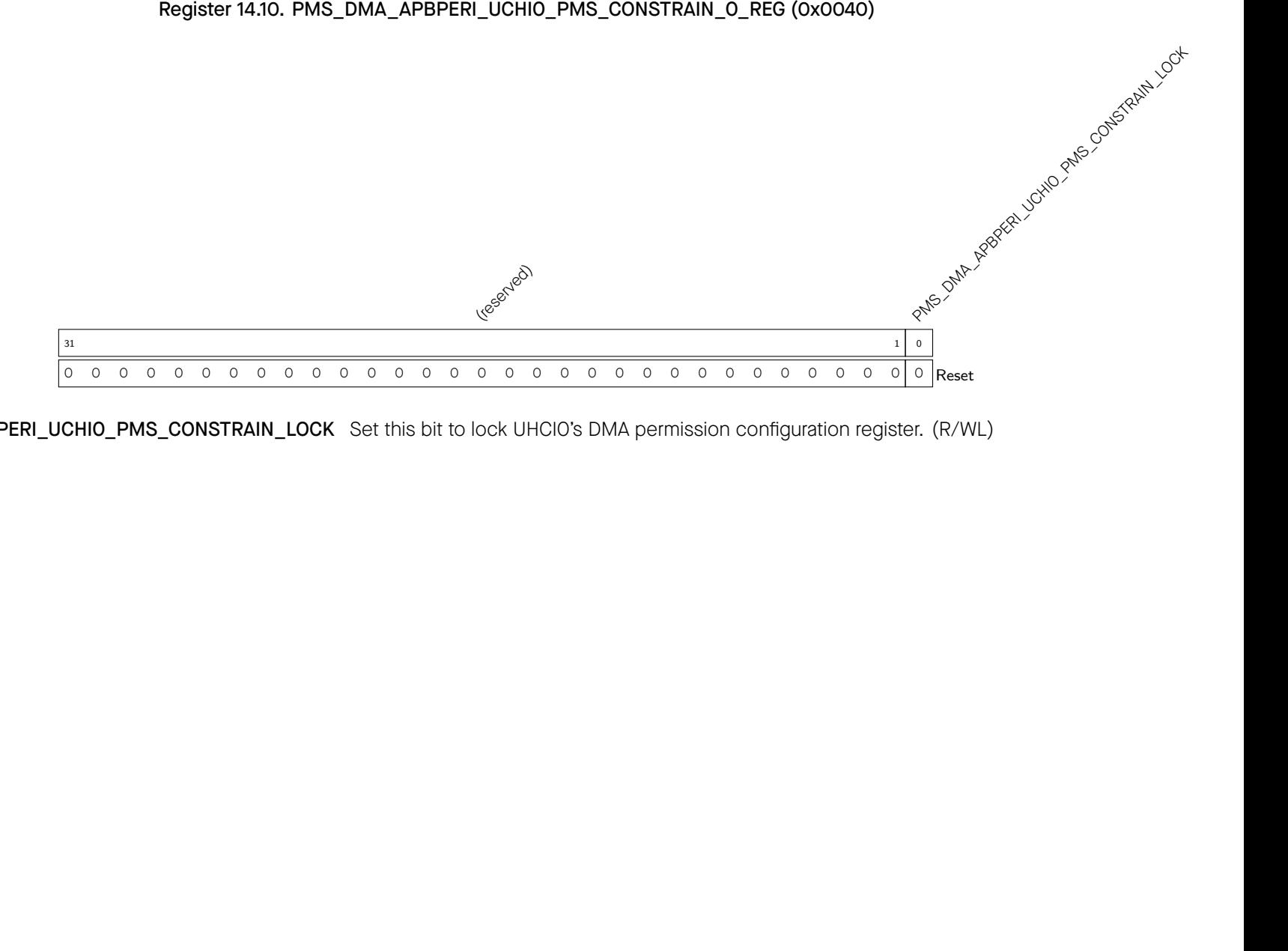

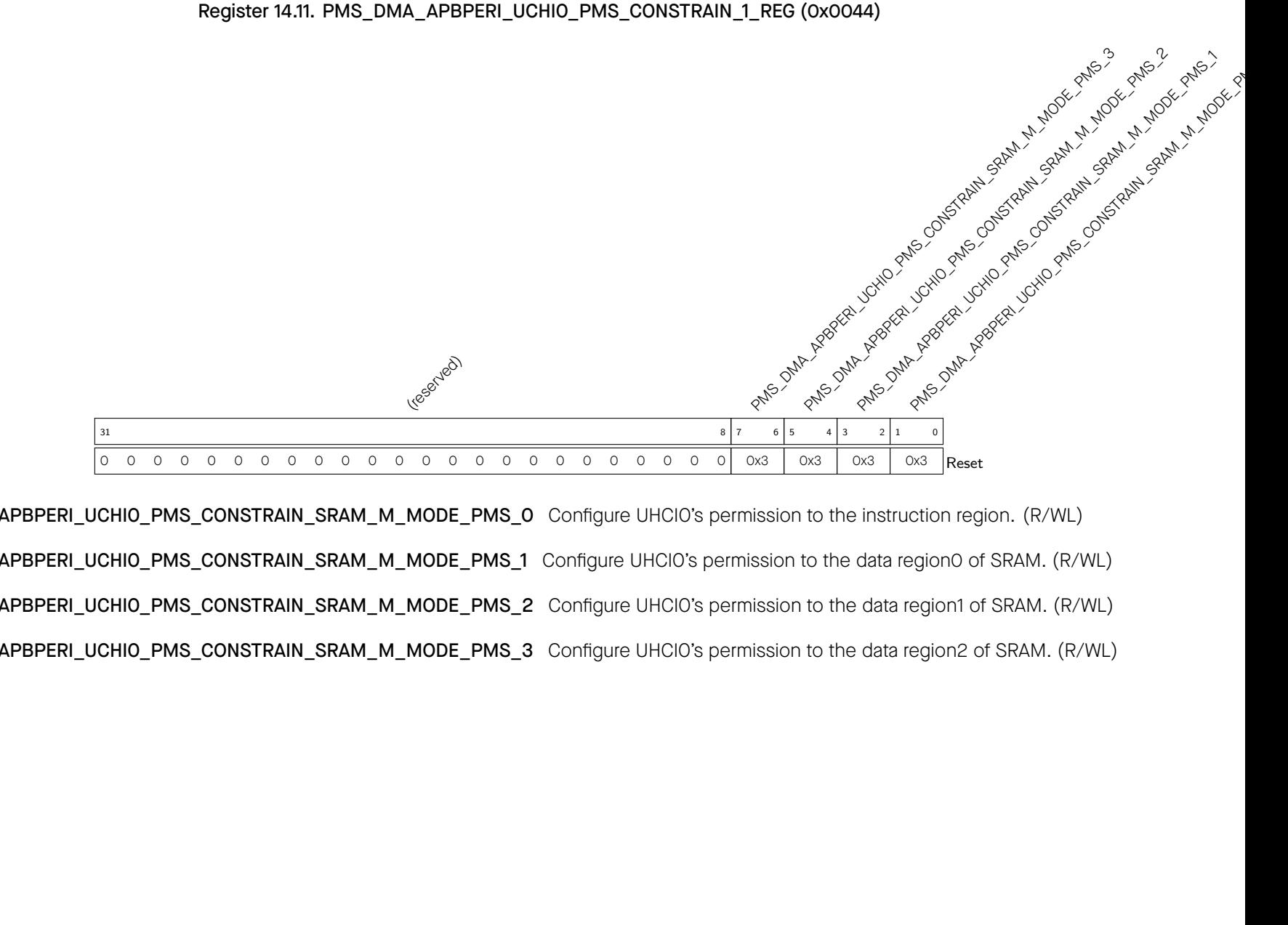

| 14.10 | Registers | 338 |

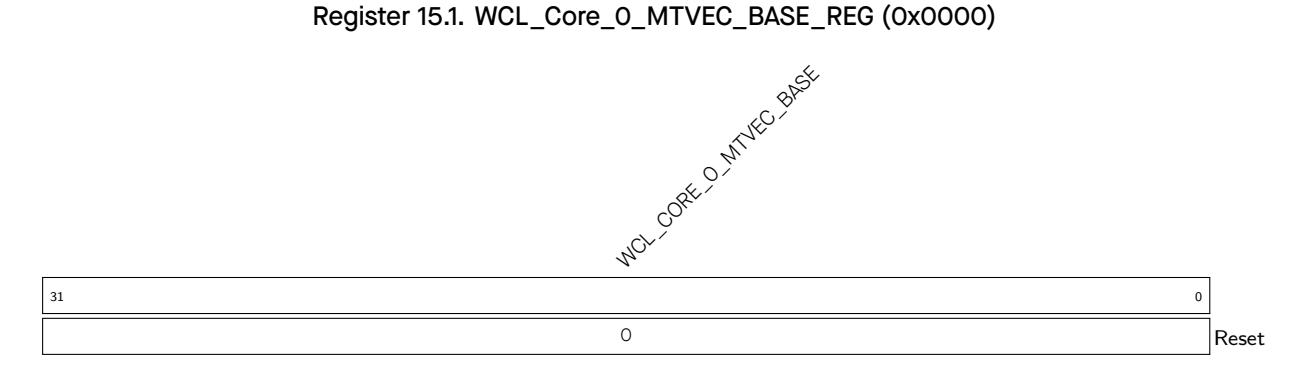

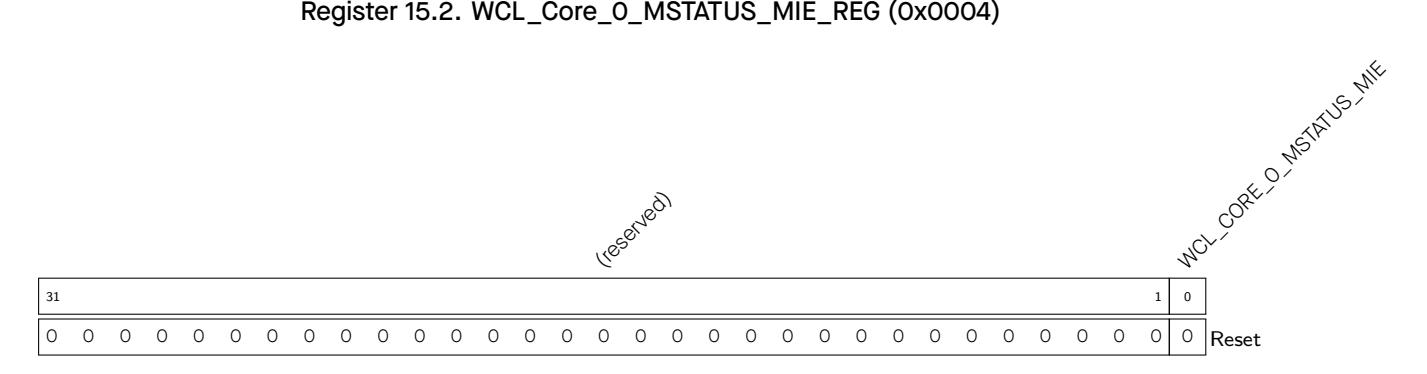

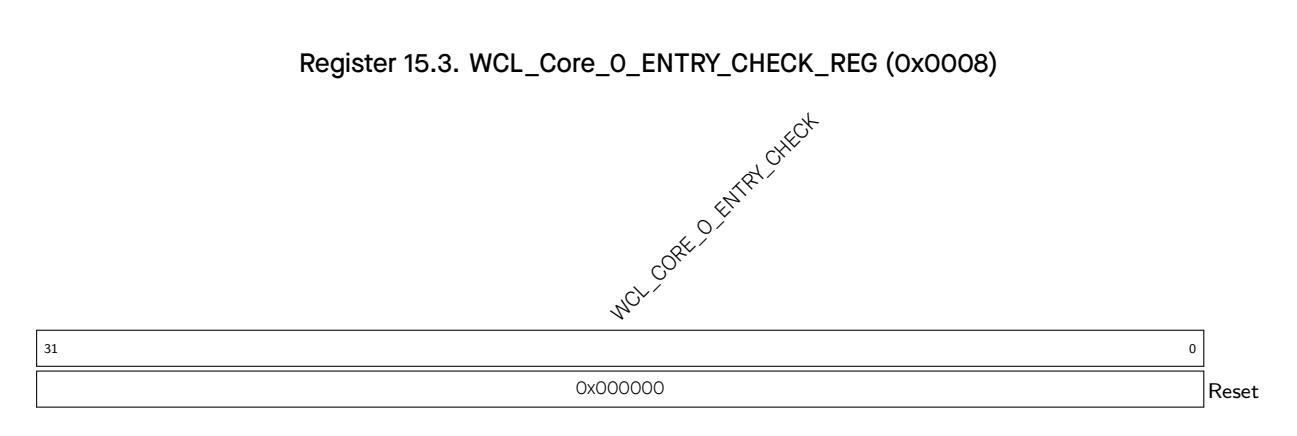

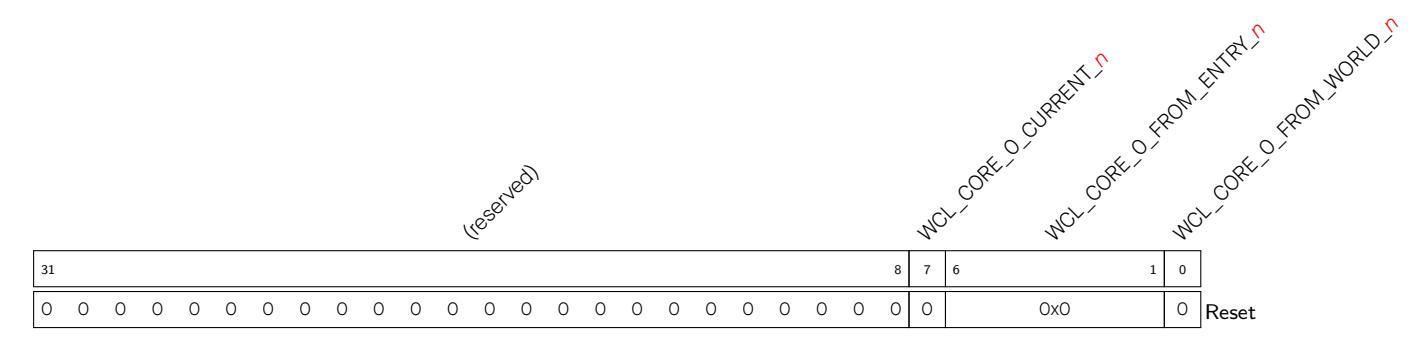

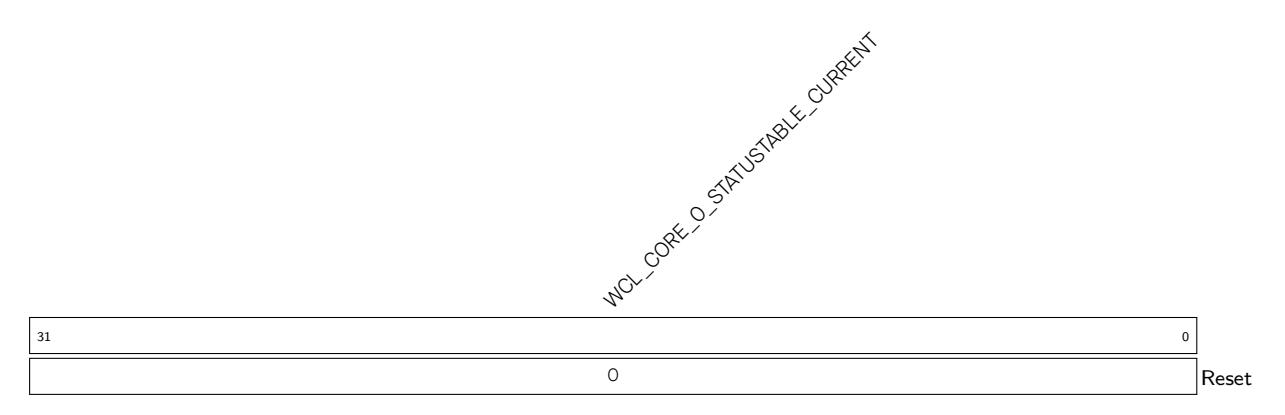

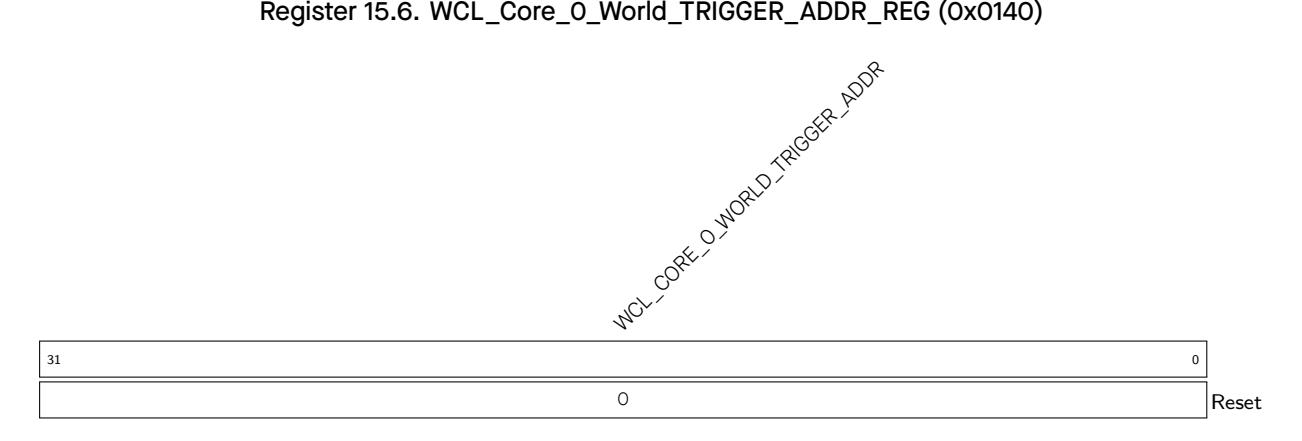

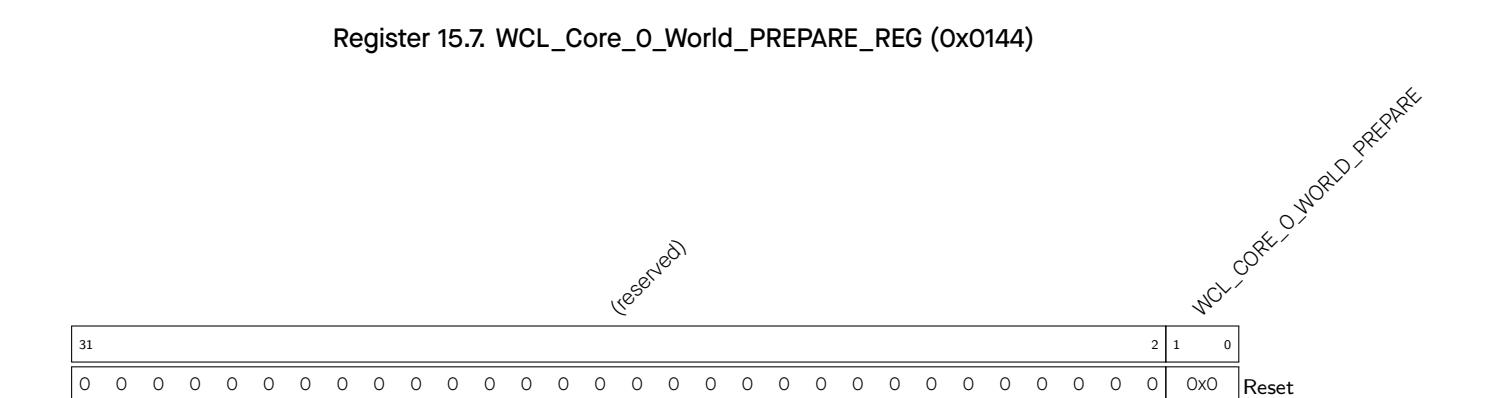

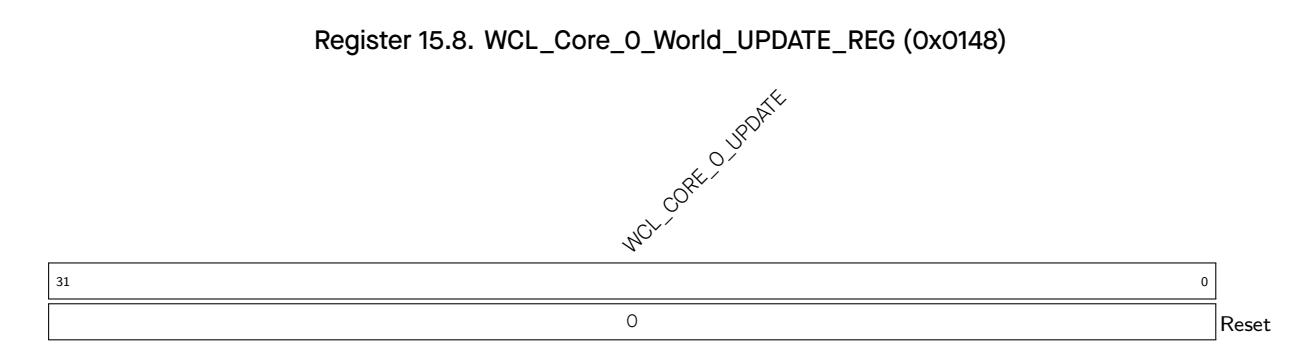

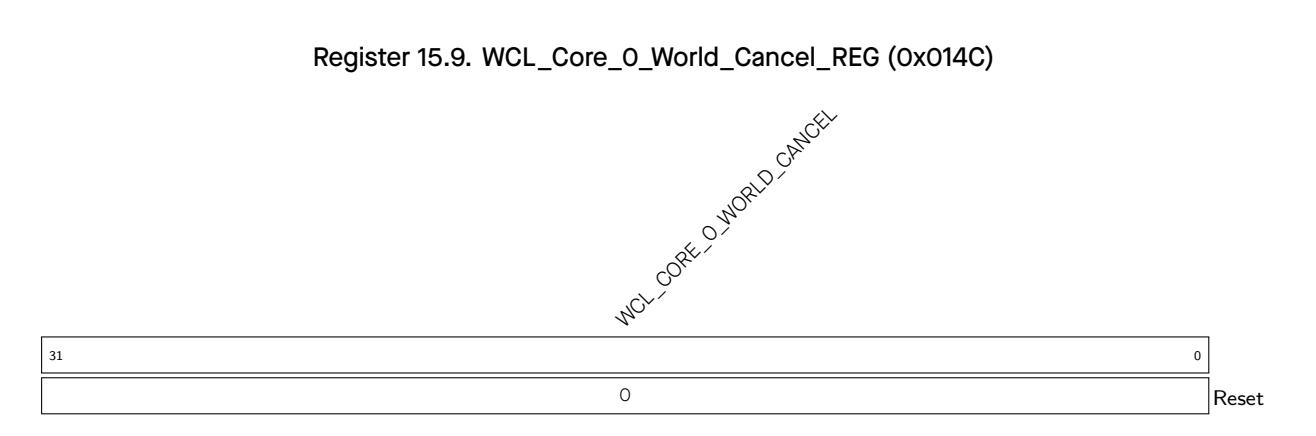

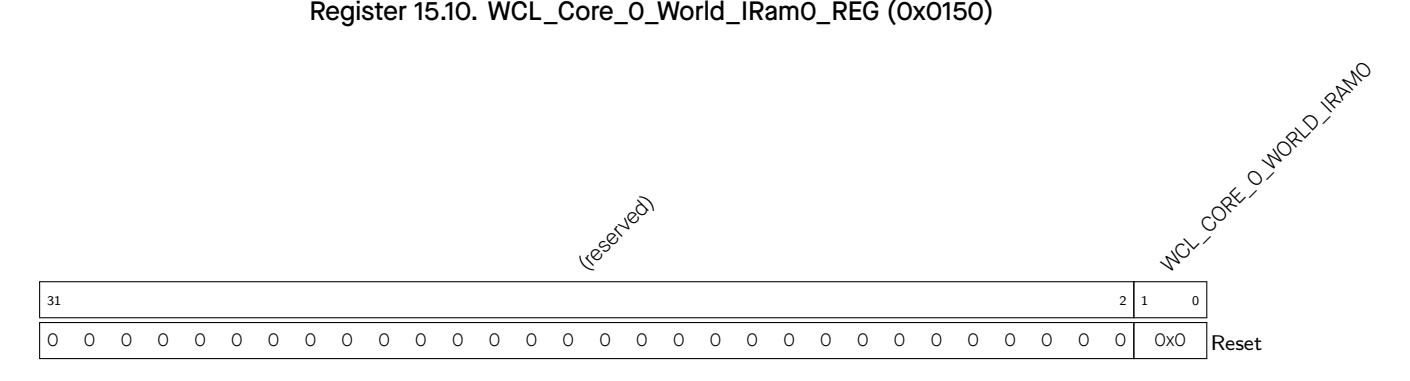

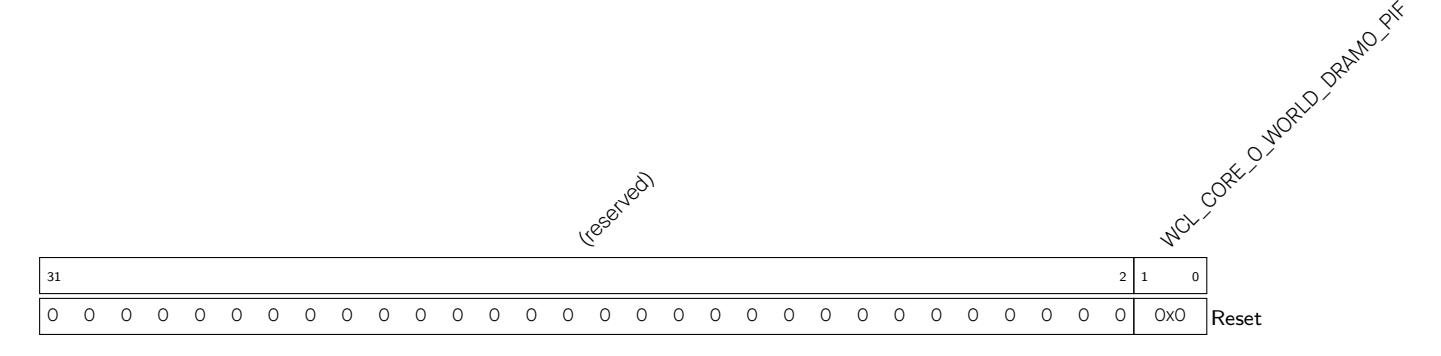

| 15 | World Controller (WCL) | 413 |

| 15.1 | Introduction | 413 |

| 15.2 | Features | 413 |

| 15.3 | Functional Description | 413 |

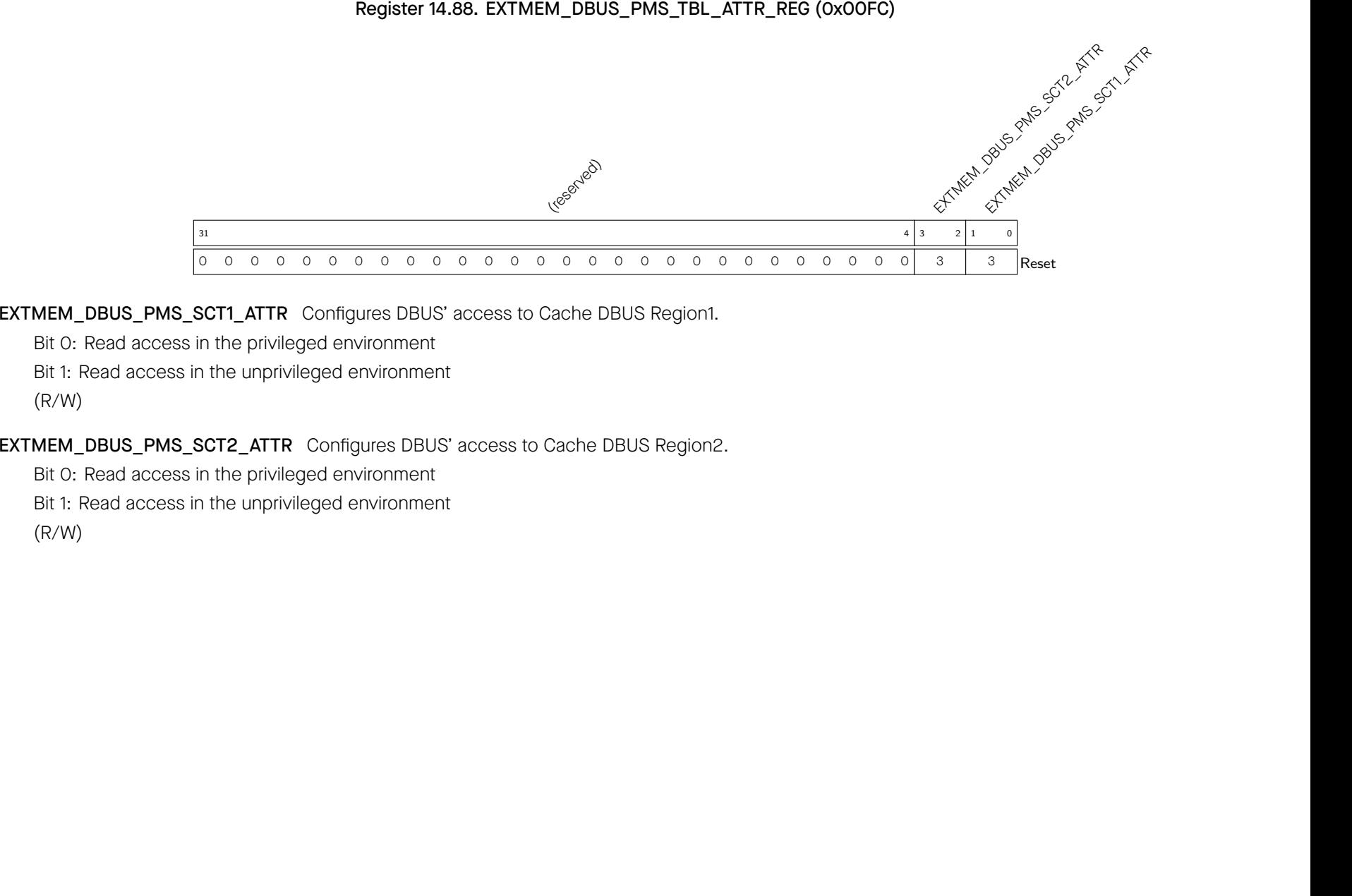

| 15.4 | CPU's World Switch | 415 |

|

15.4.1

From Secure World to Non-secure World 15.4.2 From Non-secure World to Secure World |

415

416 |

|

| 15.5 | World Switch Log | 417 |

|

15.5.1

Structure of World Switch Log Register |

417 | |

|

15.5.2

How World Switch Log Registers are Updated |

418 | |

|

15.5.3

How to Read World Switch Log Registers |

420 | |

|

15.5.4

Nested Interrupts |

420 | |

|

15.5.4.1

Programming Procedure |

420 | |

| 15.6 | Register Summary | 422 |

| 15.7 | Registers | 423 |

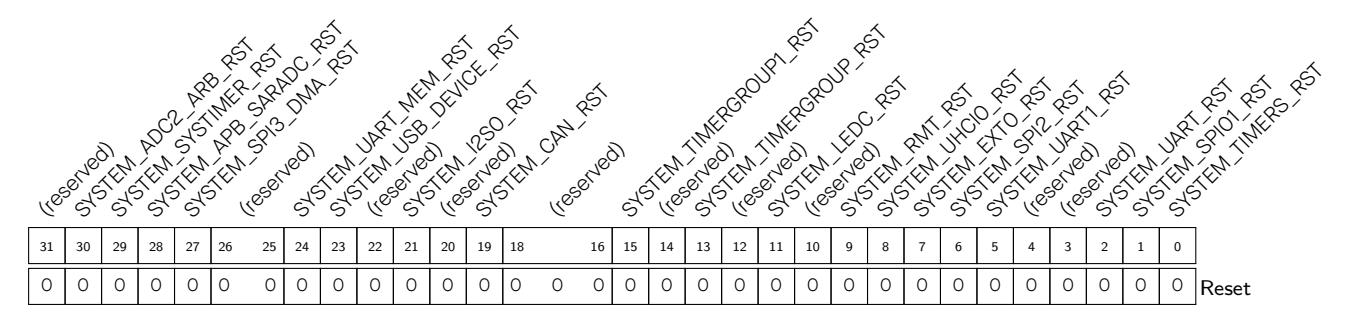

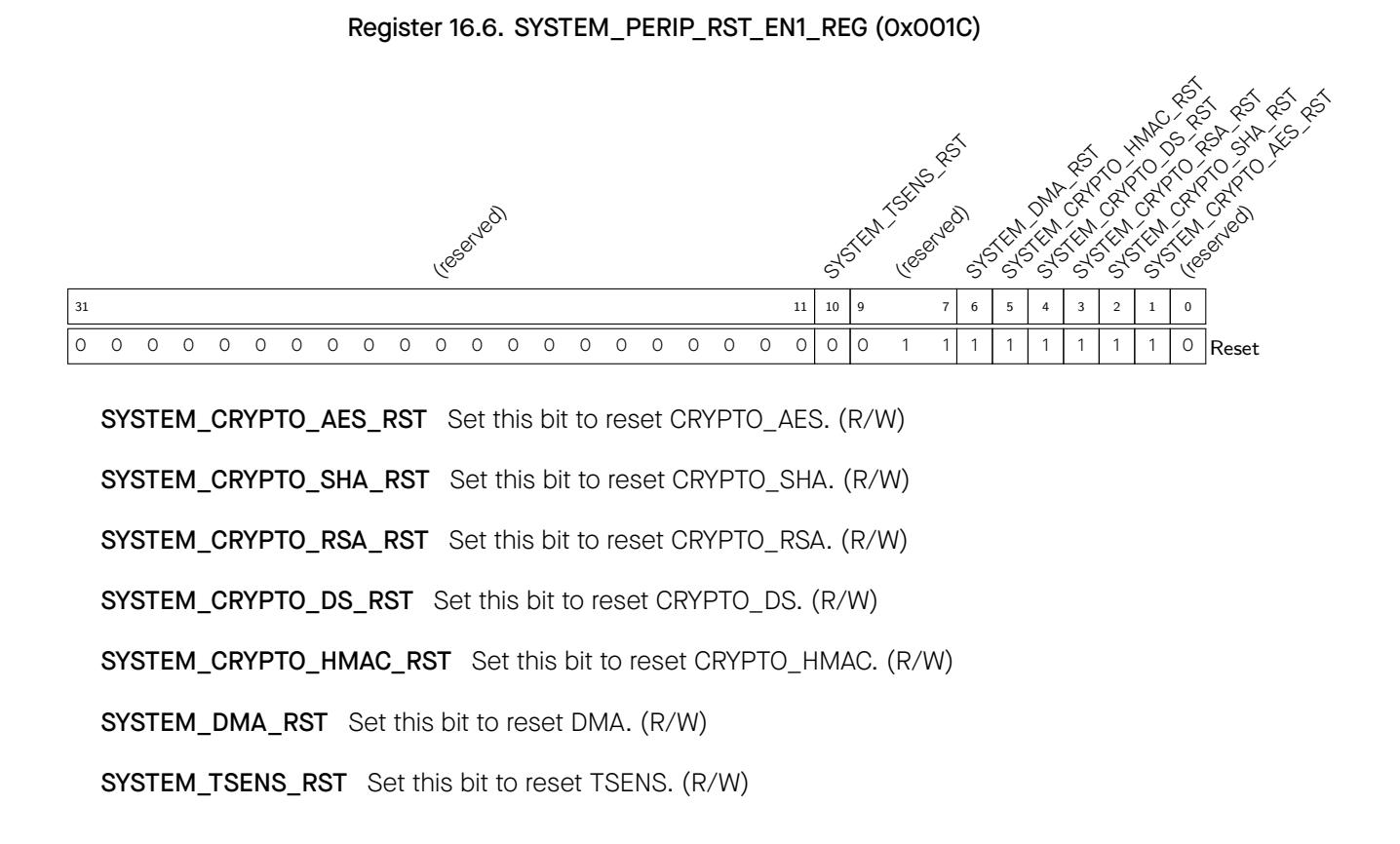

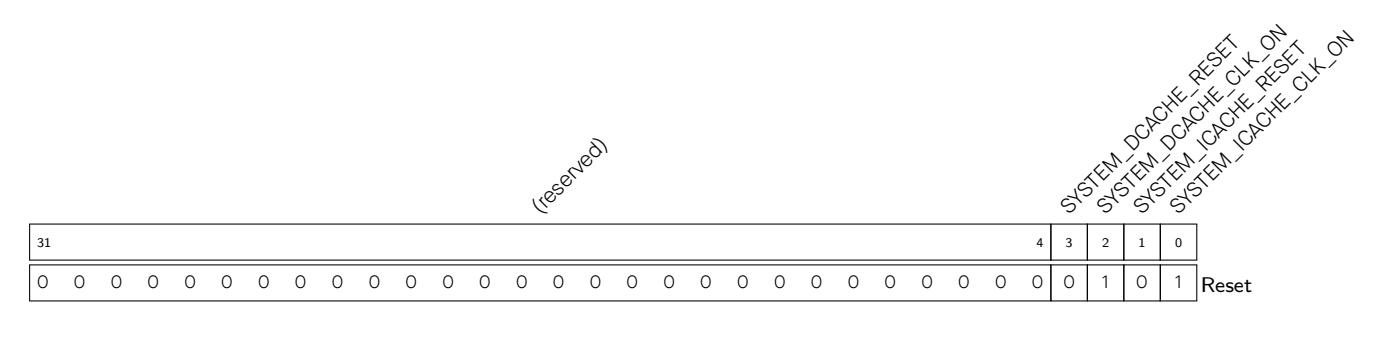

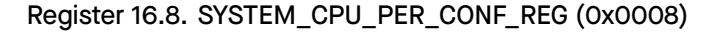

| 16 | System Registers (SYSREG) | 427 |

| 16.1 | Overview | 427 |

| 16.2 | Features | 427 |

| 16.3 | Function Description | 427 |

|

16.3.1

System and Memory Registers 16.3.1.1 Internal Memory |

427

427 |

|

|

16.3.1.2

External Memory |

428 | |

|

16.3.1.3

RSA Memory |

428 | |

|

16.3.2

Clock Registers |

429 | |

|

16.3.3

Interrupt Signal Registers |

429 | |

|

16.3.4

Low-power Management Registers |

429 | |

|

16.3.5

Peripheral Clock Gating and Reset Registers |

429 | |

| 16.4 | Register Summary | 432 |

| 16.5 | Registers | 434 |

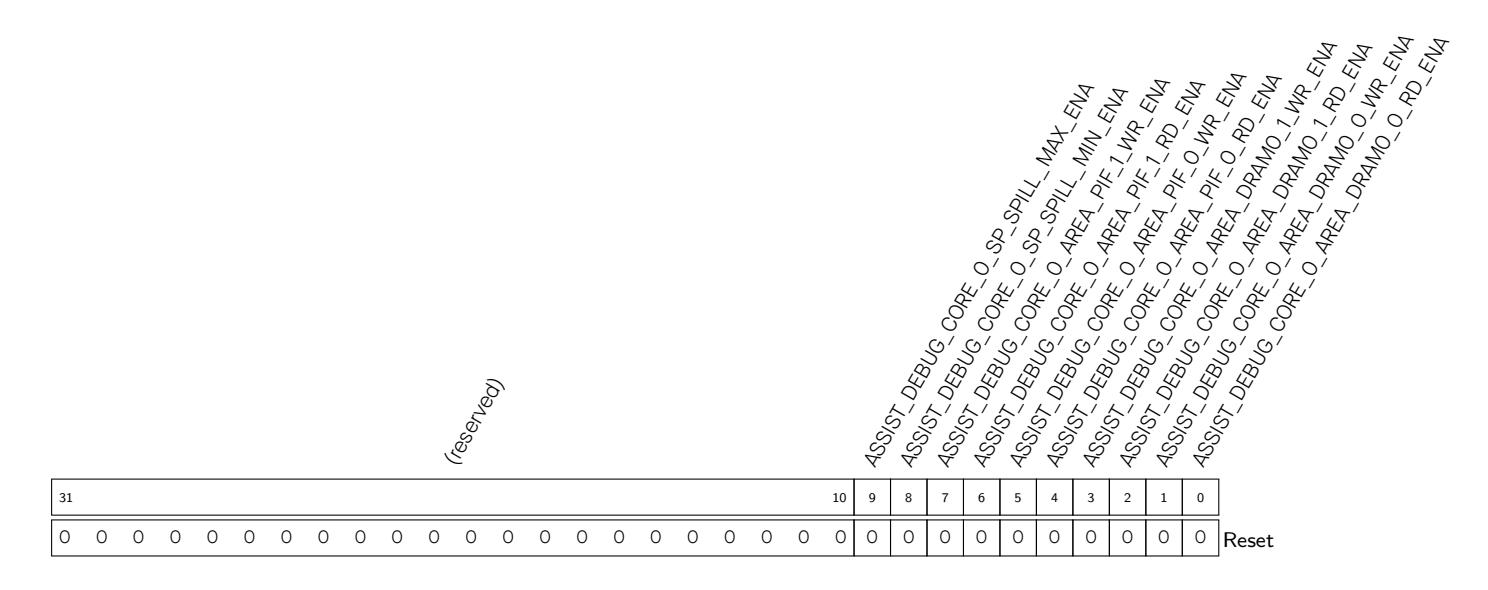

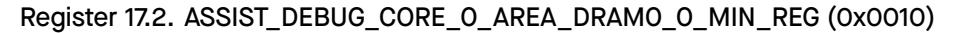

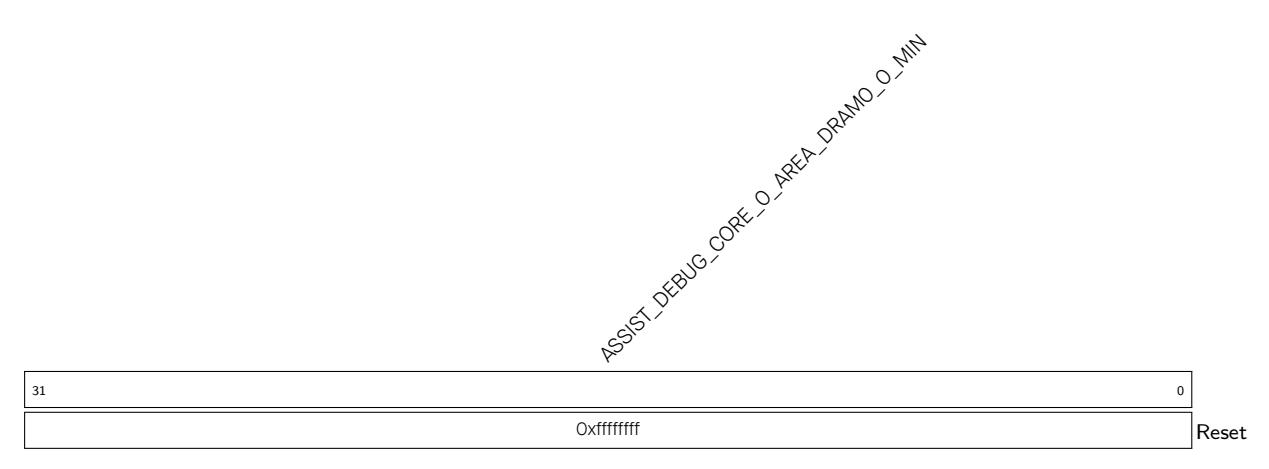

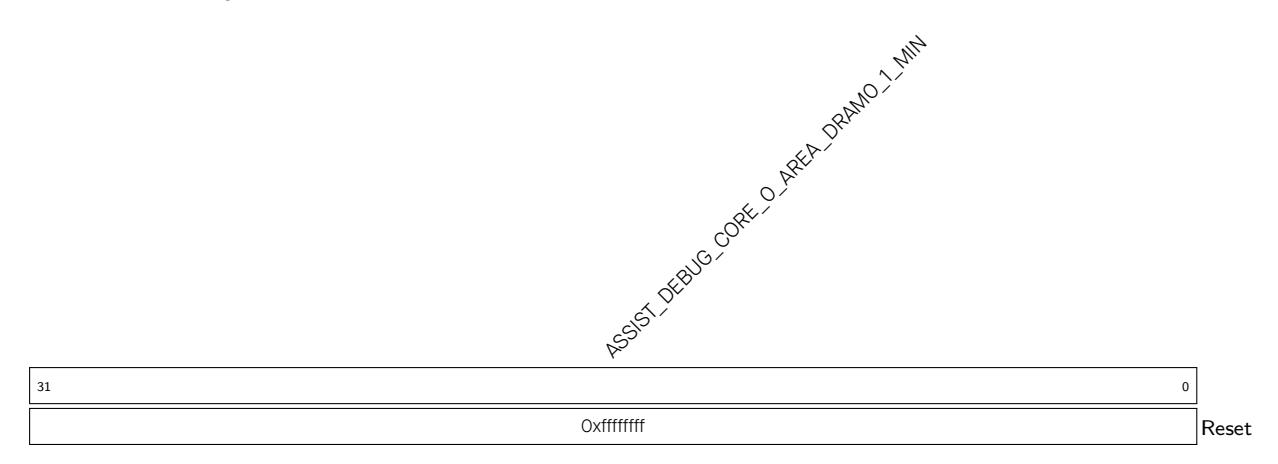

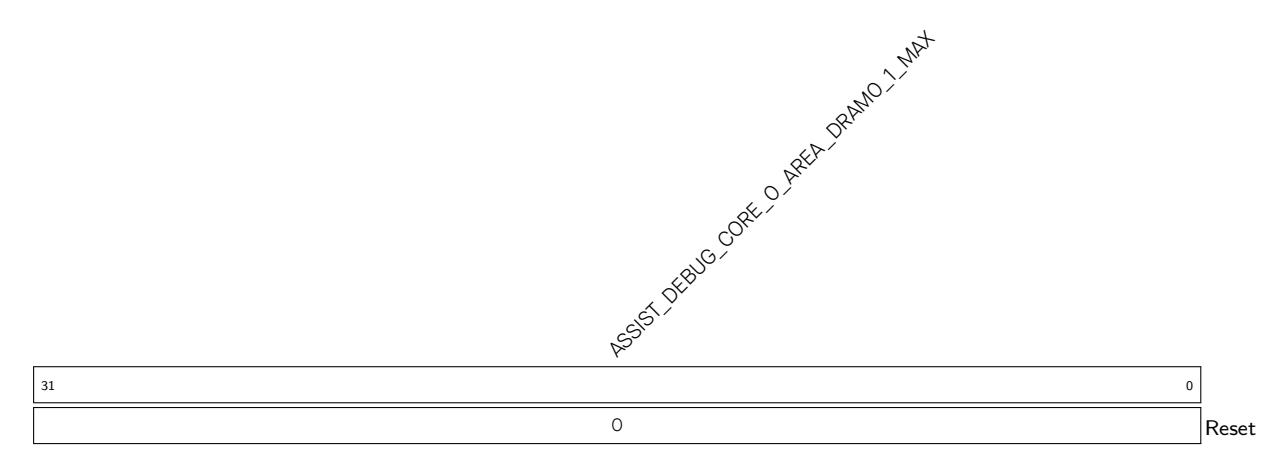

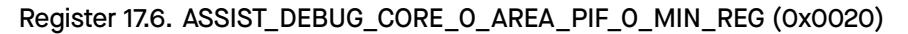

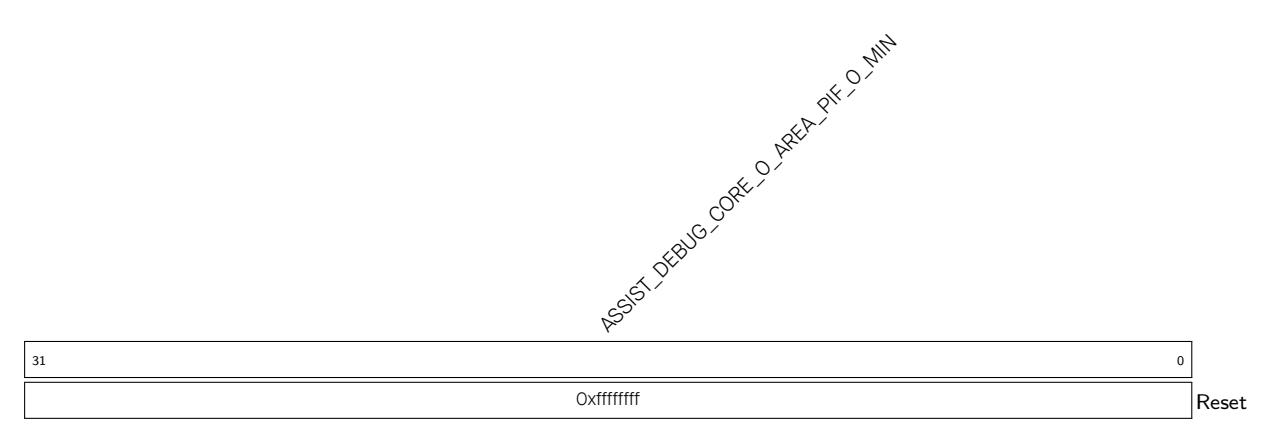

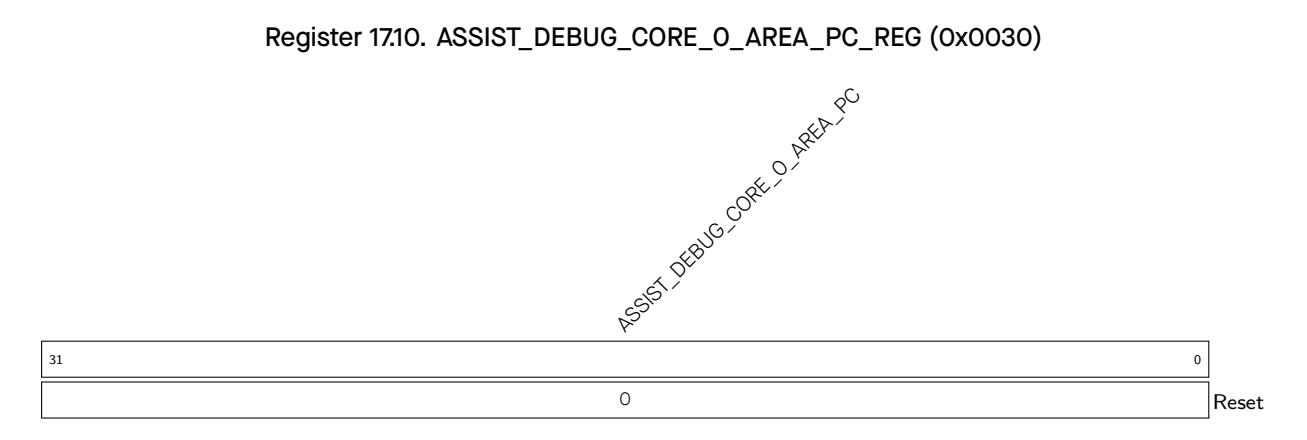

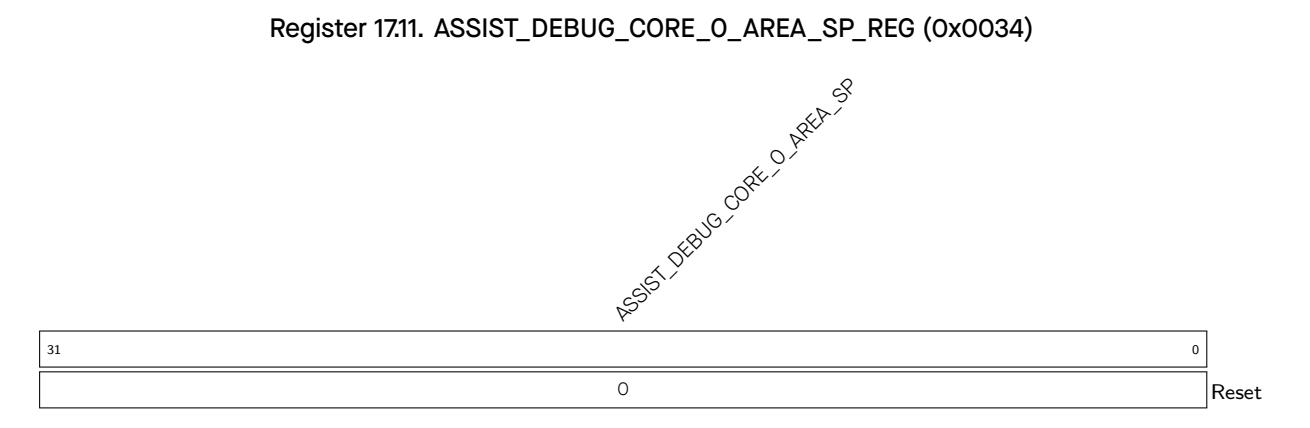

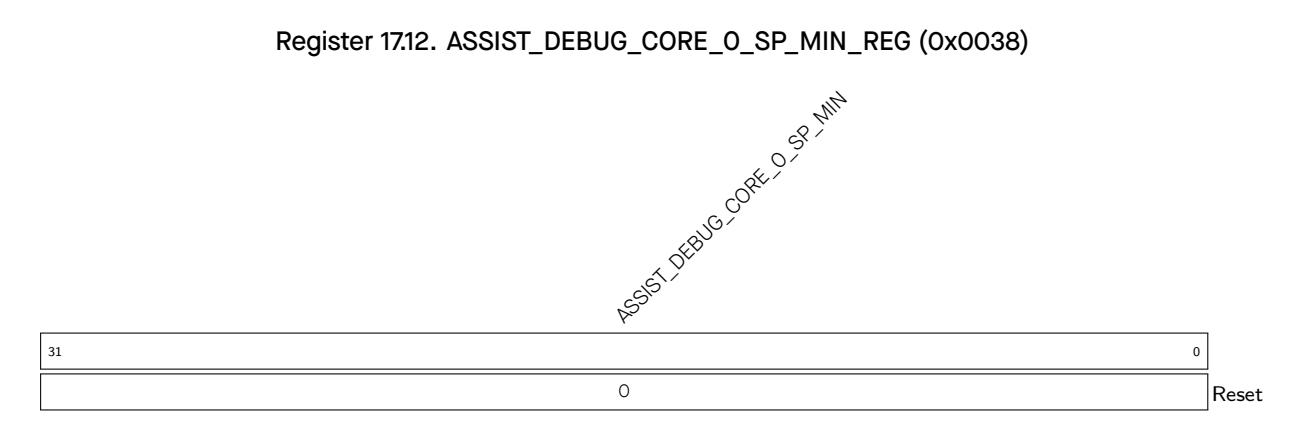

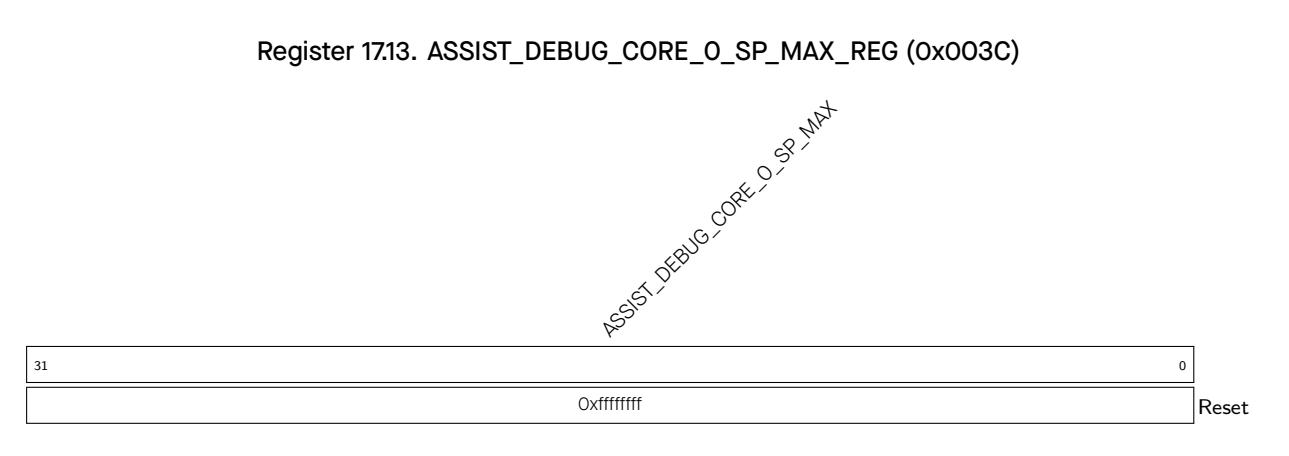

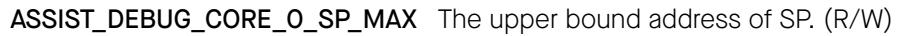

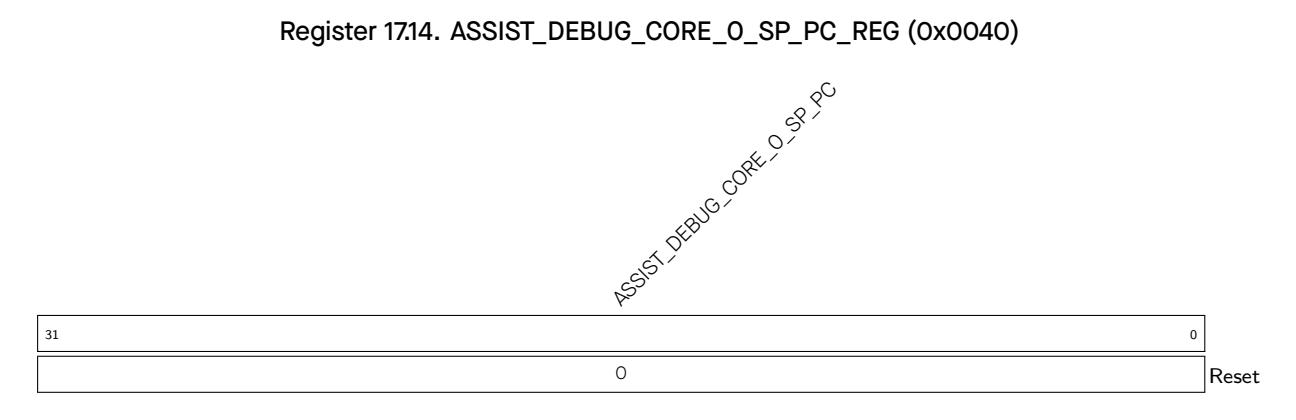

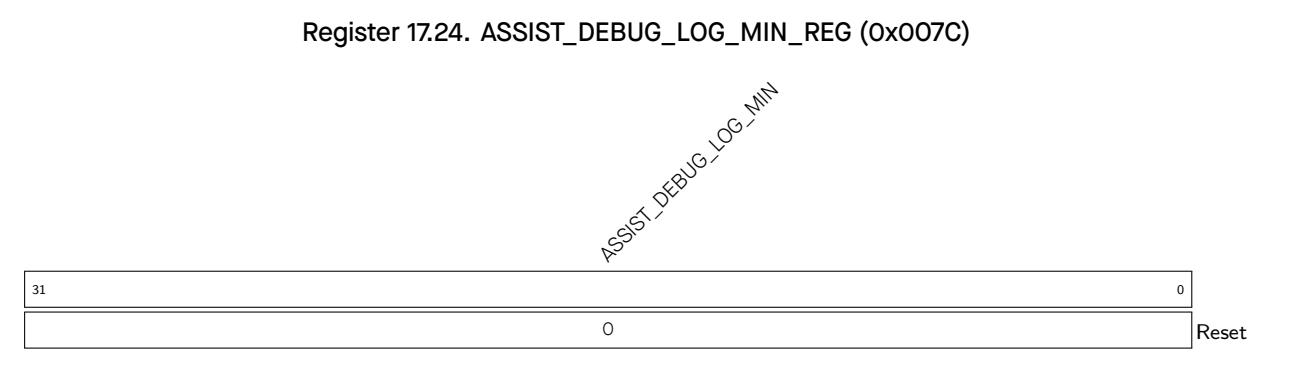

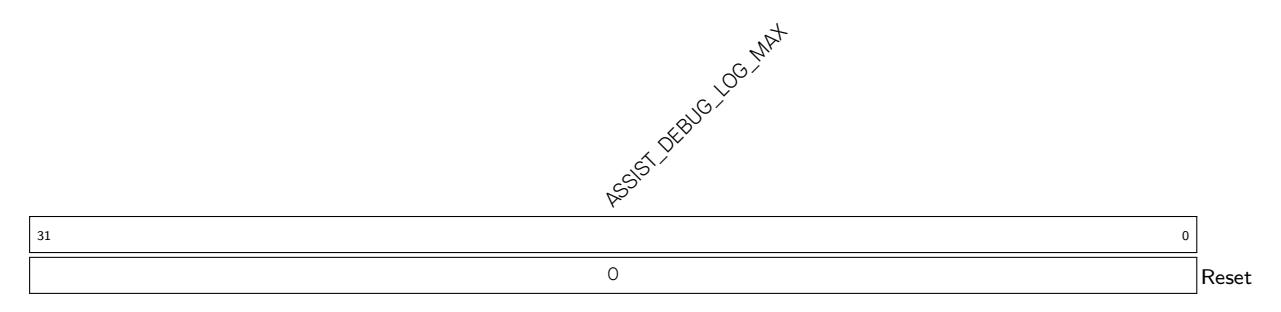

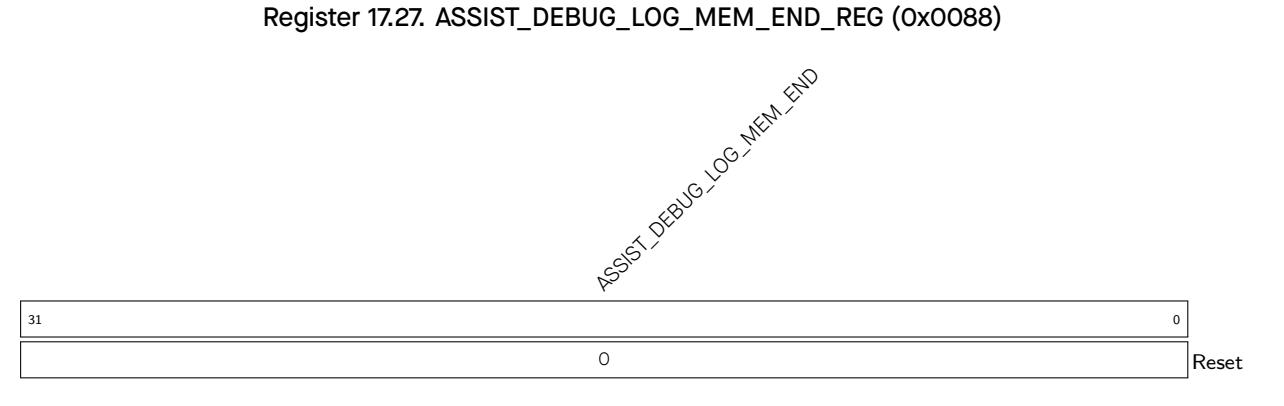

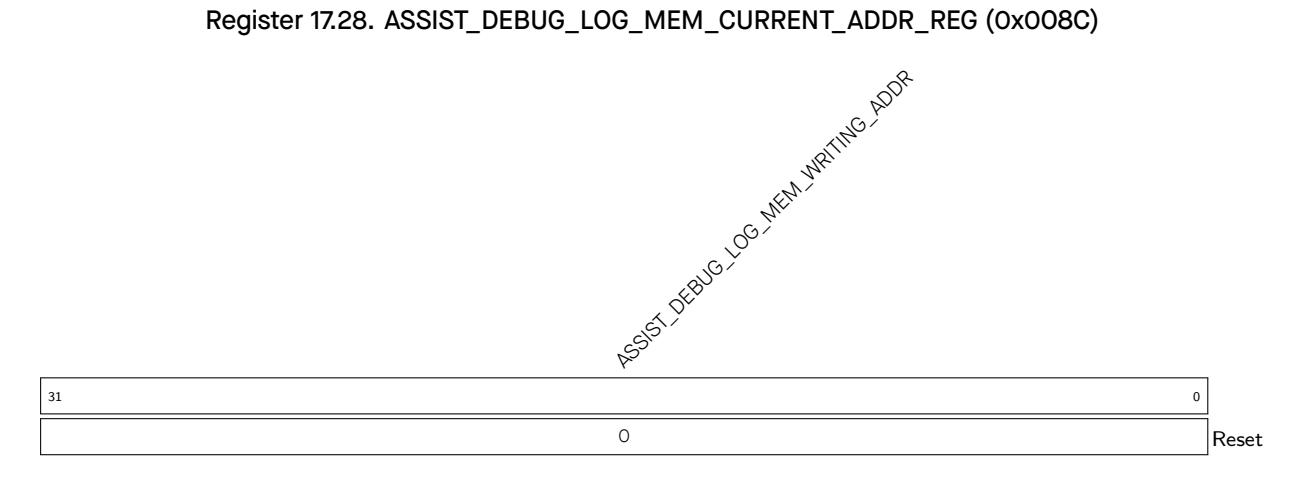

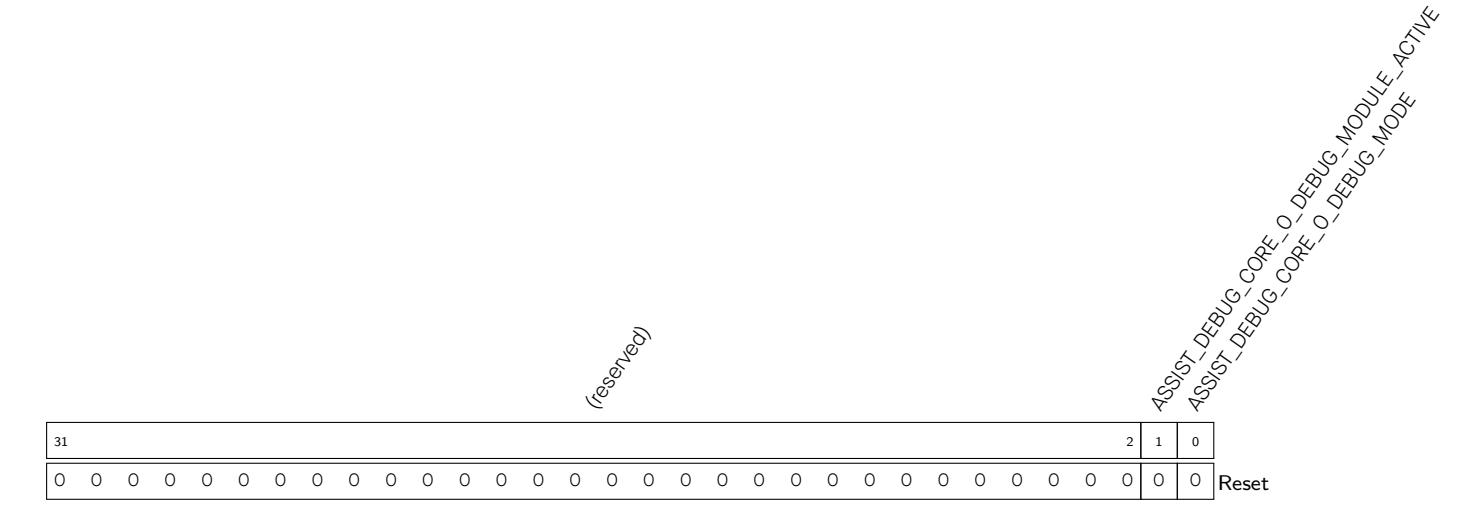

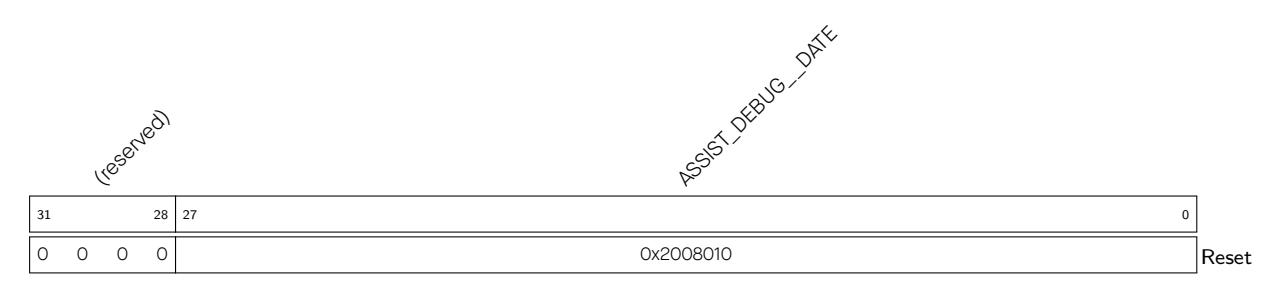

| 17 | Debug Assistant (ASSIST_DEBUG) | 446 |

| 17.1 | Overview | 446 |

| 17.2 | Features | 446 |

| 17.3 | Functional Description | 446 |

|

17.3.1

Region Read/Write Monitoring |

446 | |

|

17.3.2

SP Monitoring 17.3.3 PC Logging |

446

447 |

|

|

17.3.4

CPU/DMA Bus Access Logging |

447 | |

| 17.4 | Recommended Operation | 447 |

|

17.4.1

Region Monitoring and SP Monitoring Configuration Process |

447 |

| Contents | GoBack | |

|---|---|---|

|

17.4.2

PC Logging Configuration Process 17.4.3 CPU/DMA Bus Access Logging Configuration Process |

448

449 |

|

|

17.5

17.6 |

Register Summary

Registers |

453

455 |

| IV | Cryptography/Security Component | 472 |

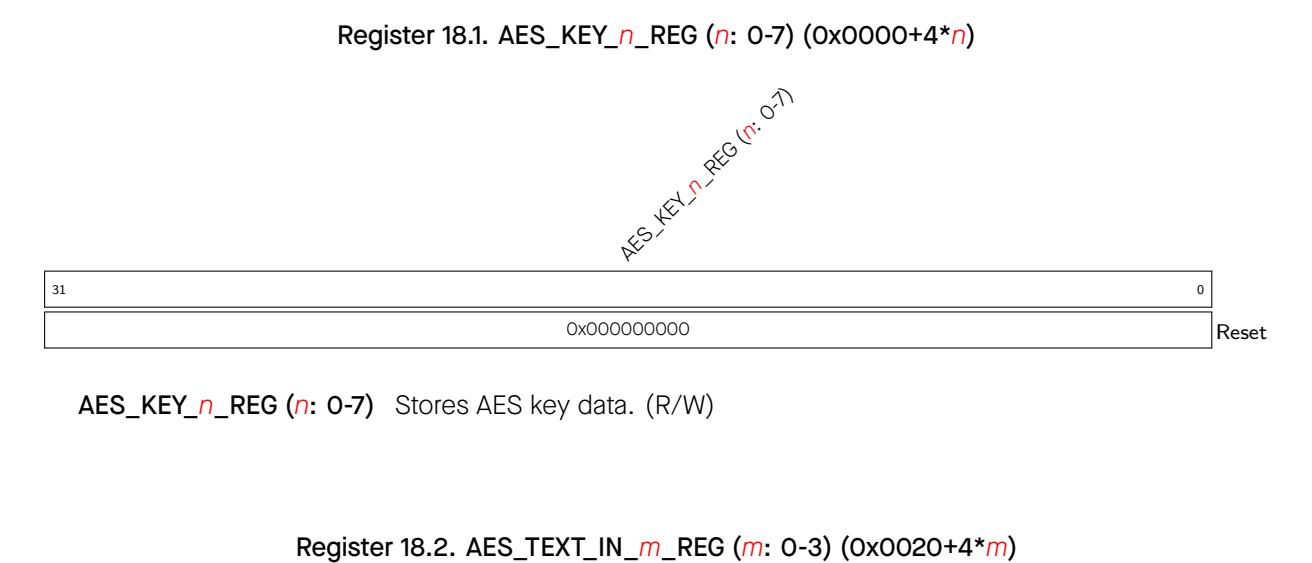

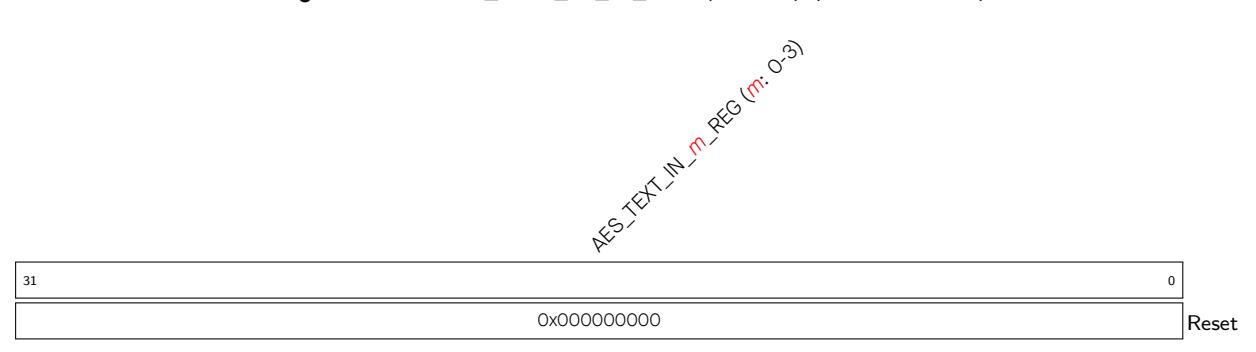

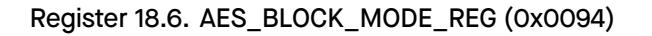

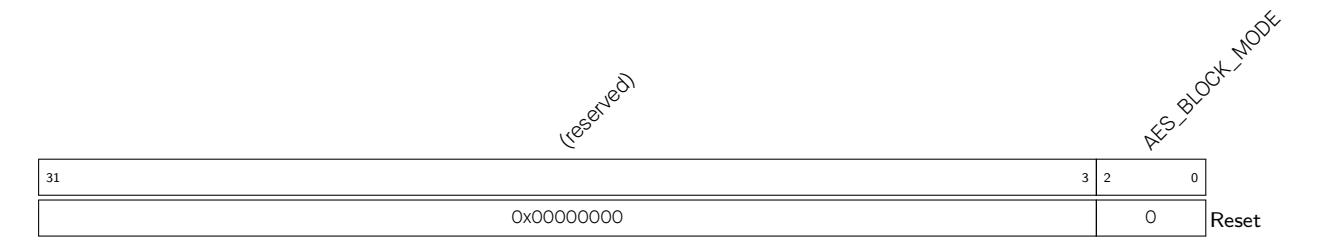

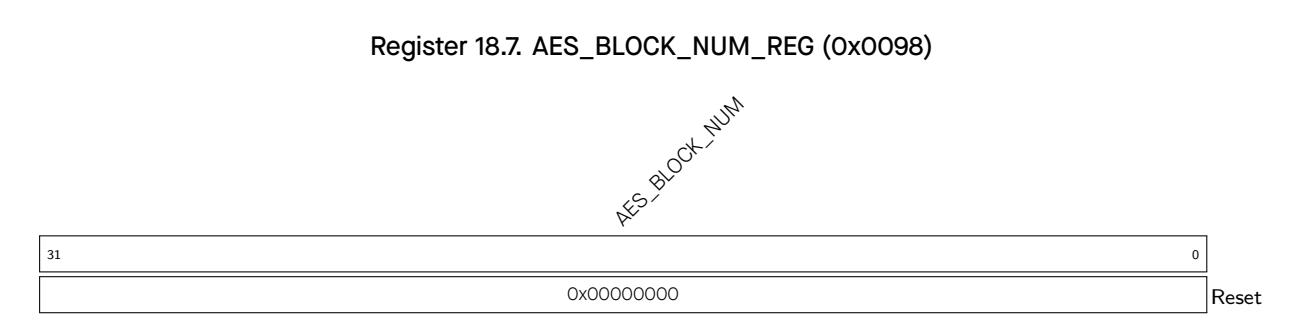

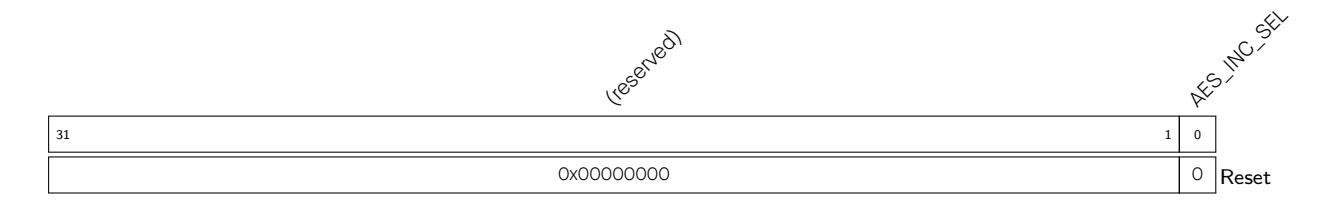

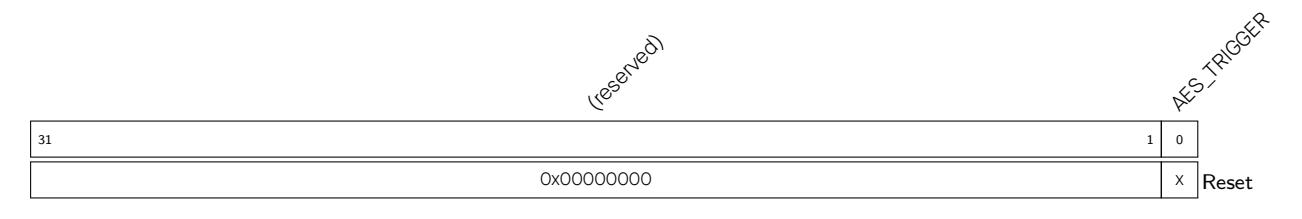

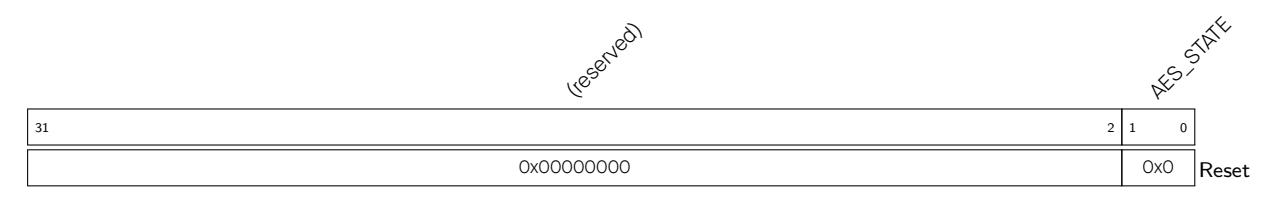

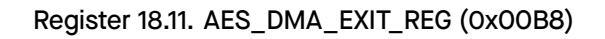

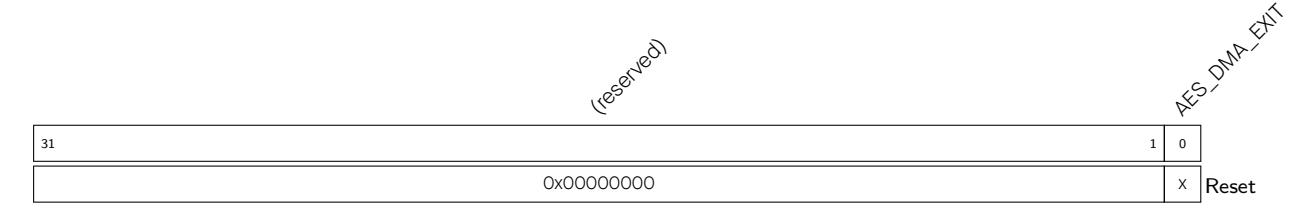

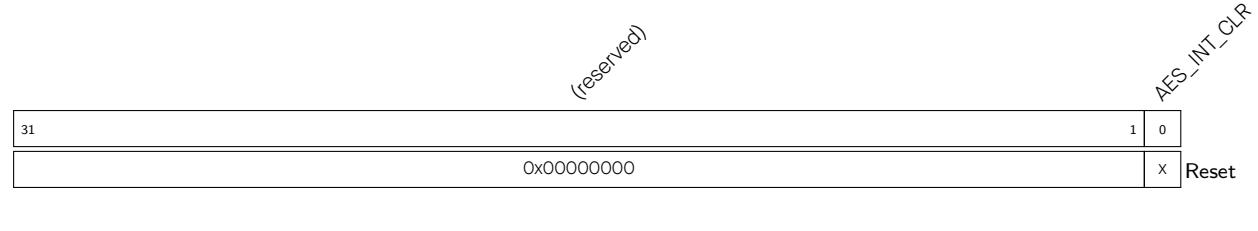

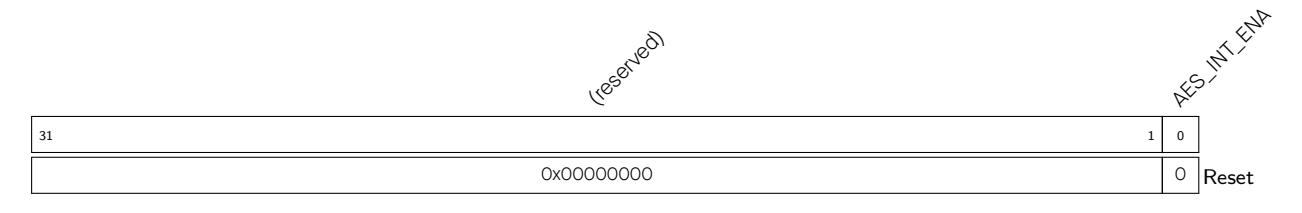

| 18 | AES Accelerator (AES) | 473 |

|

18.1

18.2 |

Introduction

Features |

473

473 |

| 18.3 | AES Working Modes | 473 |

| 18.4 | Typical AES Working Mode | 475 |

|

18.4.1

Key, Plaintext, and Ciphertext |

475 | |

|

18.4.2

Endianness |

475 | |

|

18.4.3

Operation Process |

477 | |

| 18.5 | DMA-AES Working Mode | 477 |

|

18.5.1

Key, Plaintext, and Ciphertext |

478 | |

|

18.5.2

Endianness |

479 | |

|

18.5.3

Standard Incrementing Function |

479 | |

|

18.5.4

Block Number |

479 | |

|

18.5.5

Initialization Vector 18.5.6 Block Operation Process |

479

480 |

|

| 18.6 | Memory Summary | 480 |

| 18.7 | Register Summary | 481 |

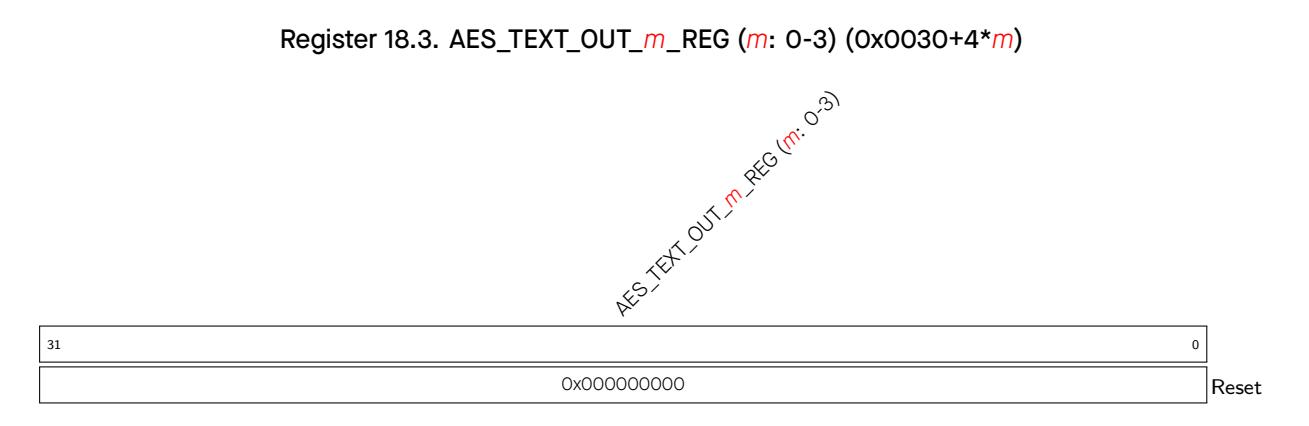

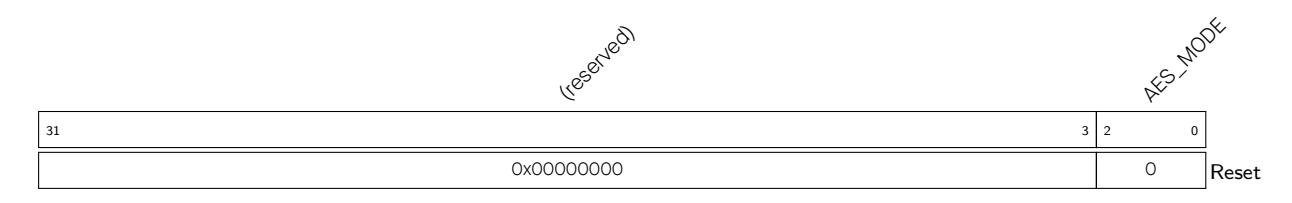

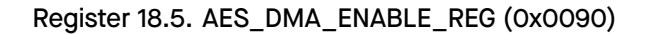

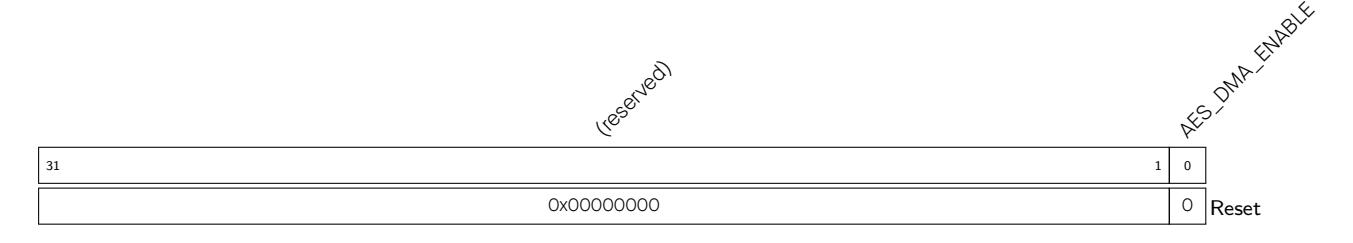

| 18.8 | Registers | 482 |

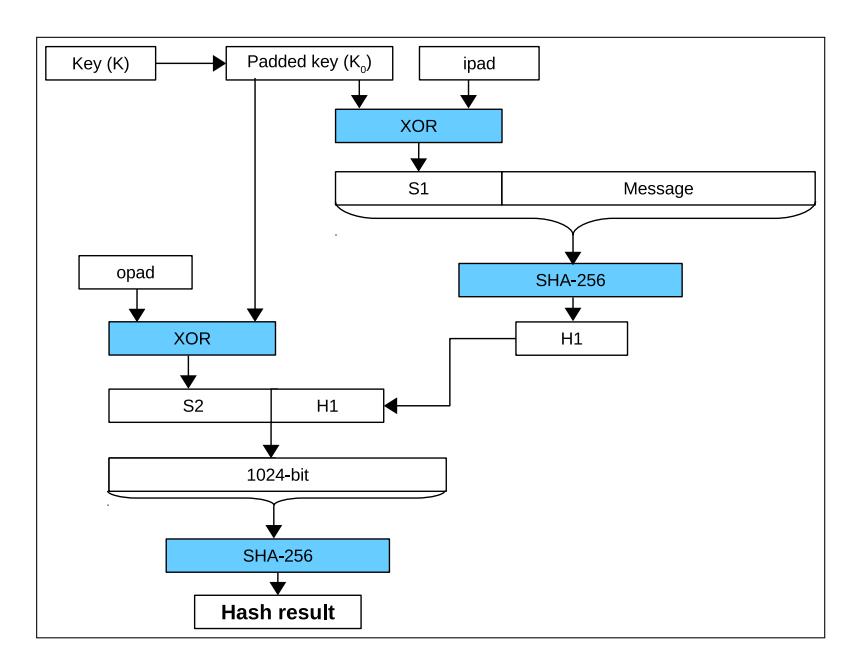

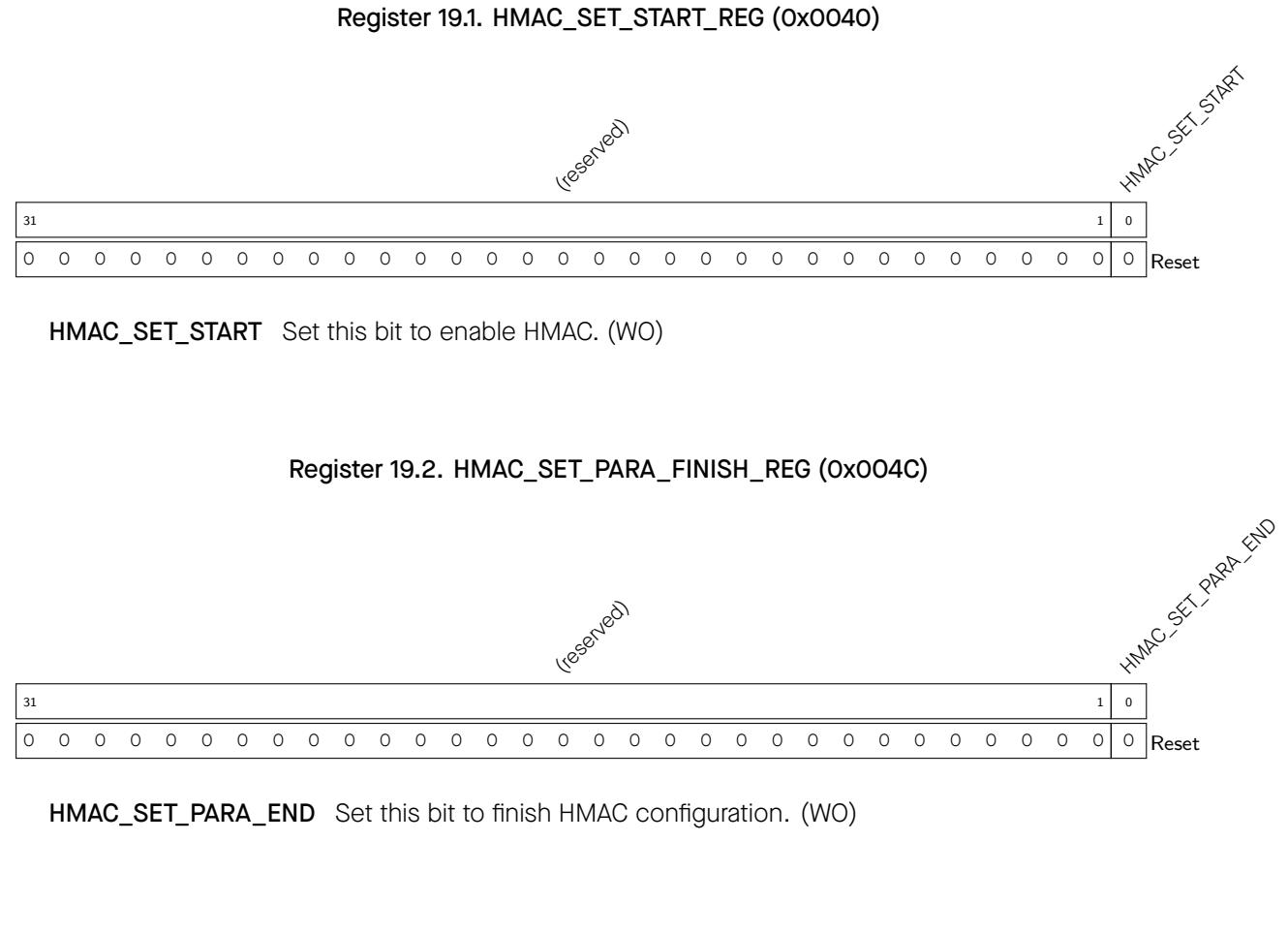

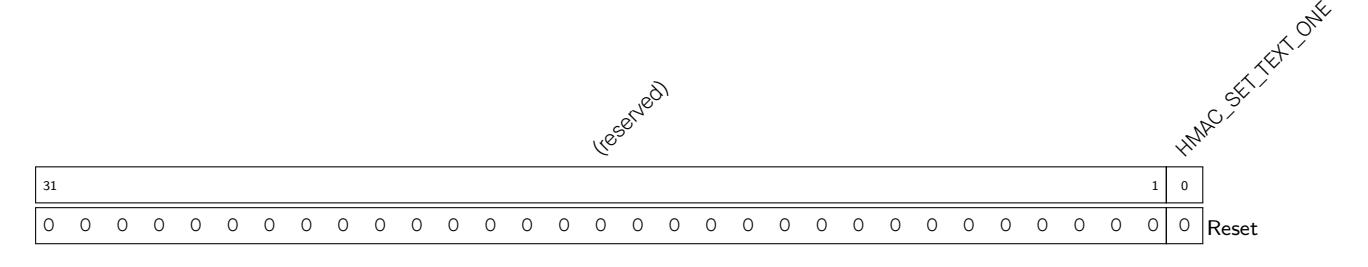

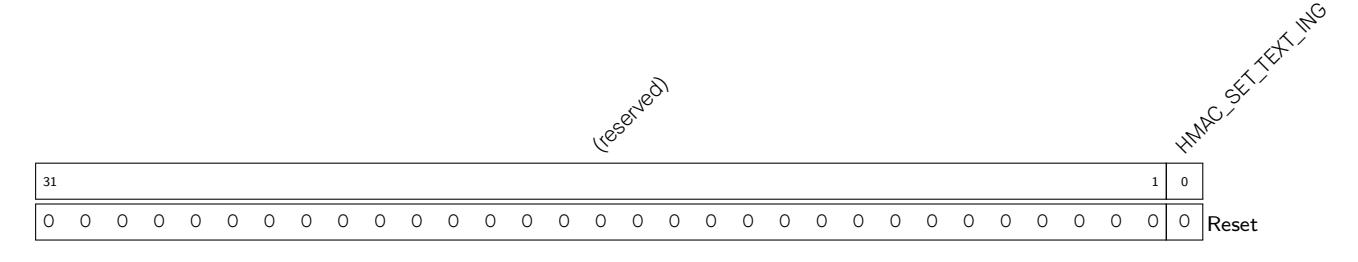

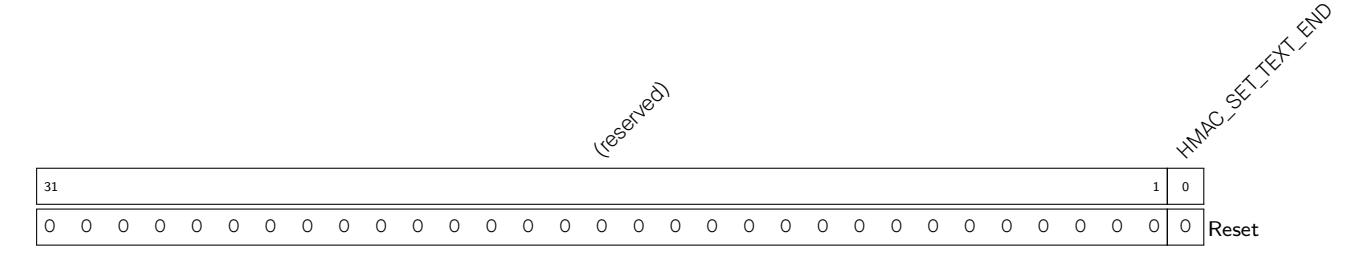

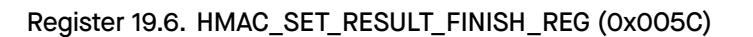

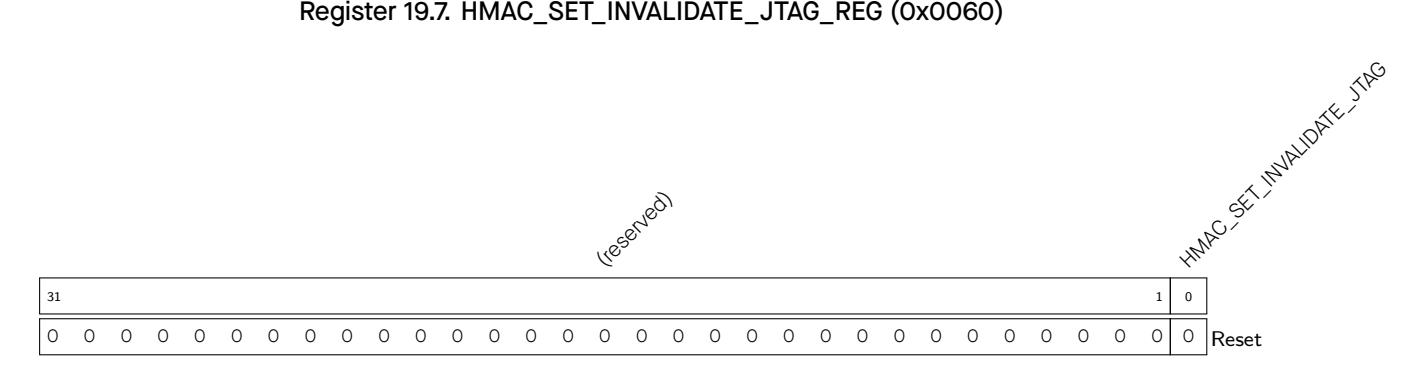

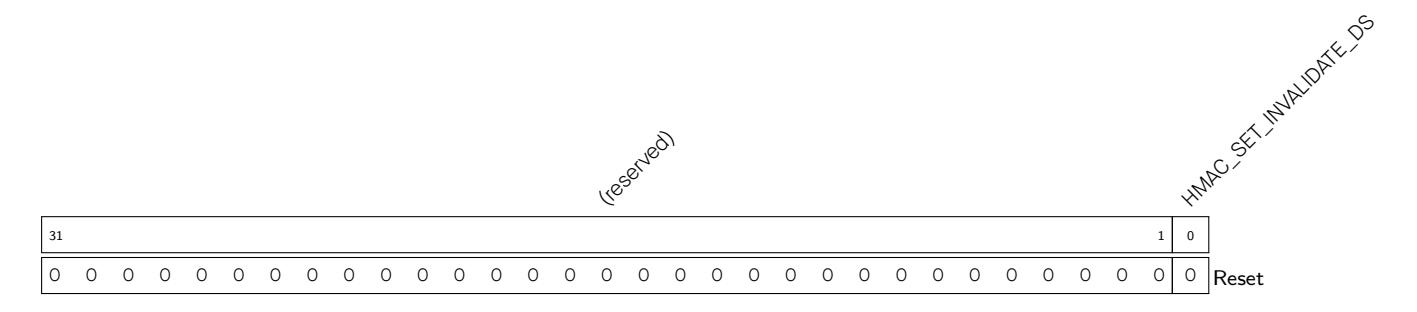

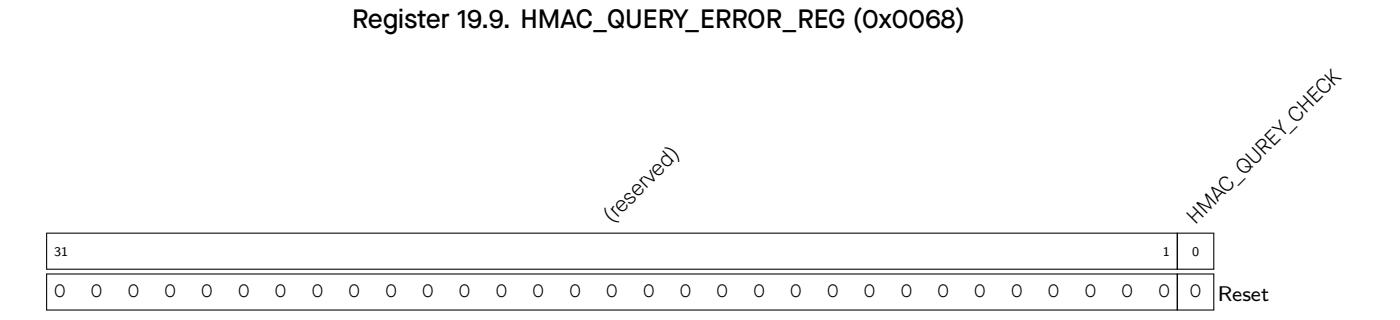

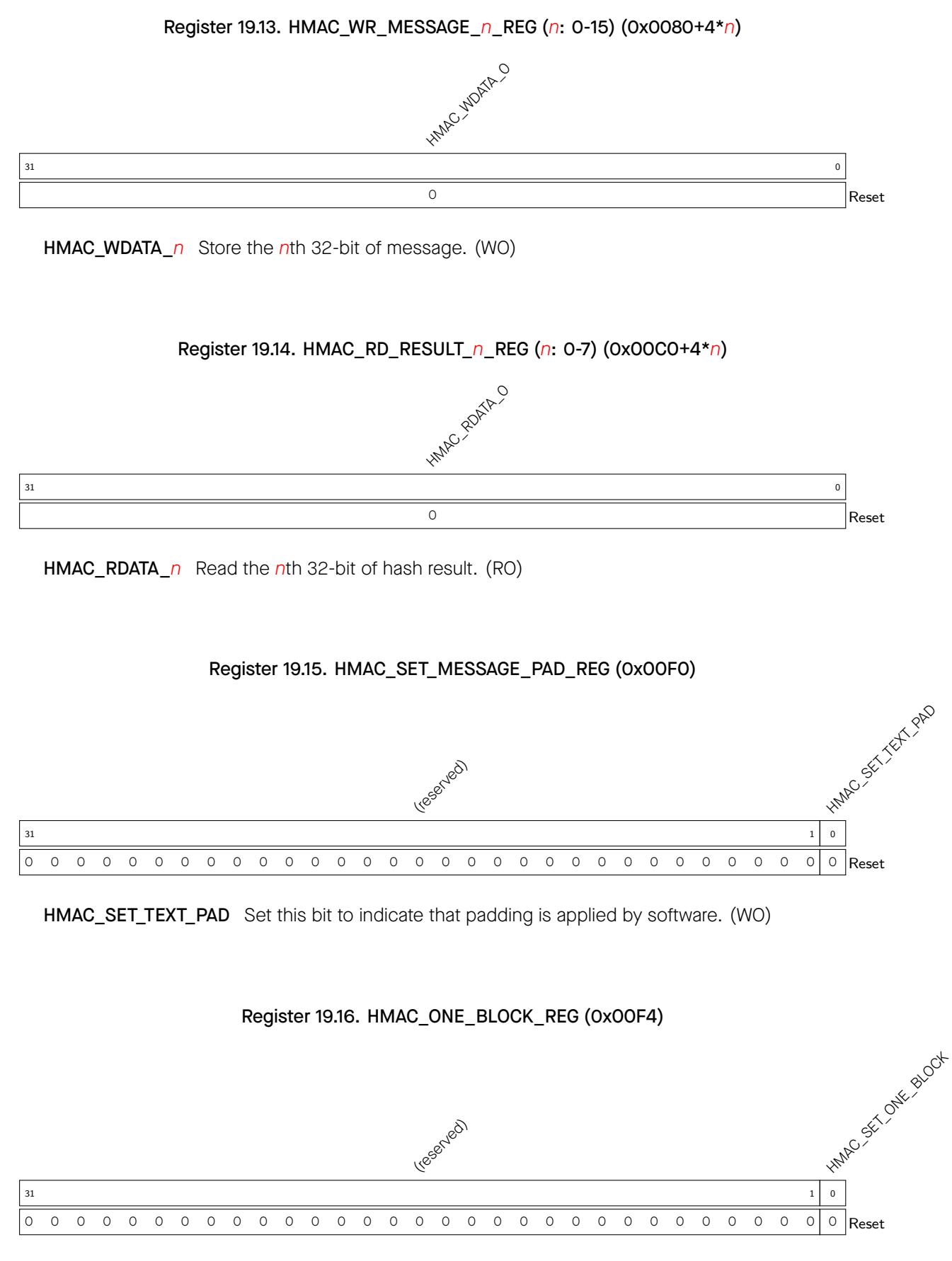

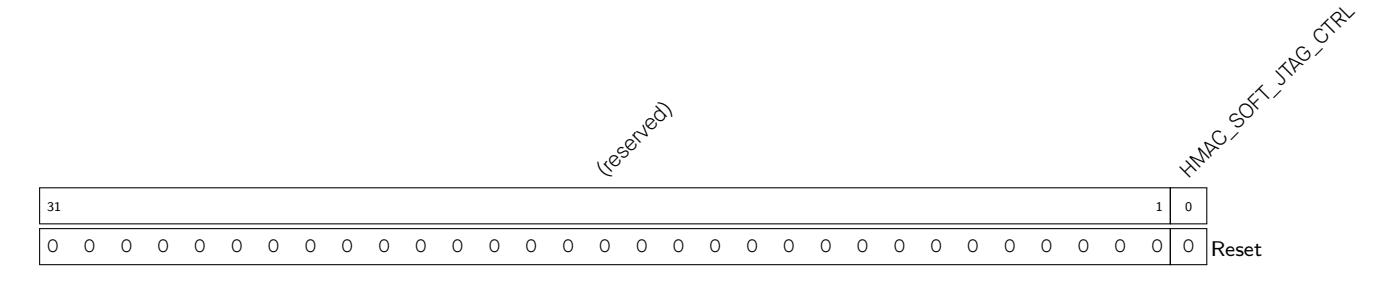

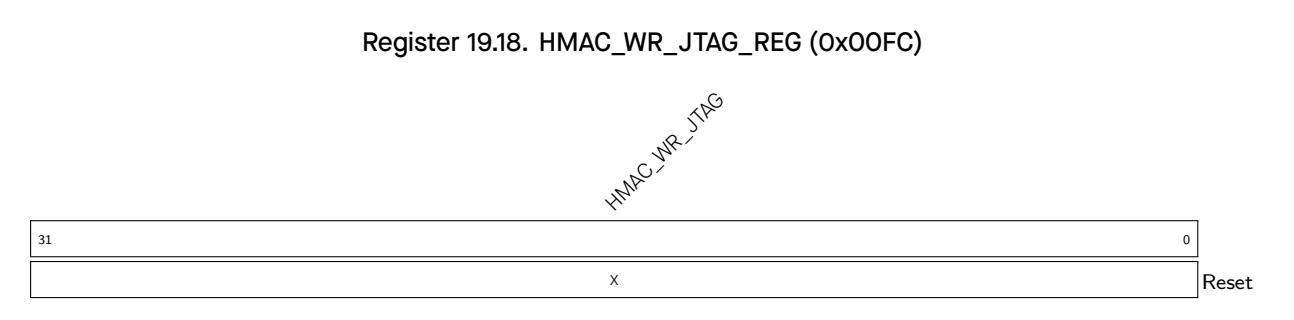

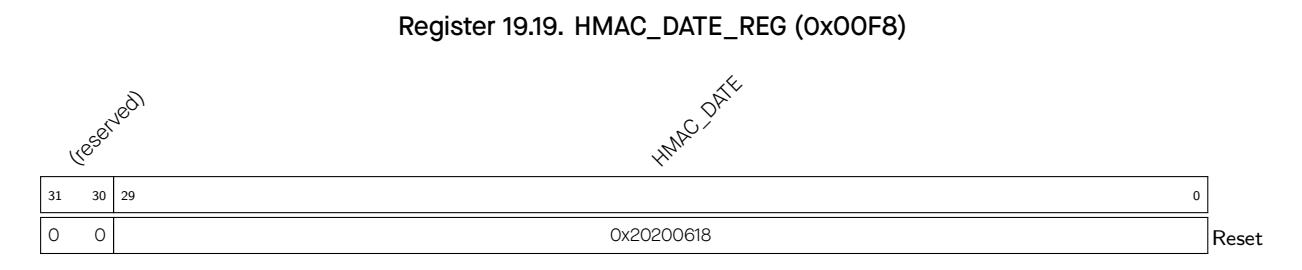

| 19 | HMAC Accelerator (HMAC) | 486 |

| 19.1 | Main Features | 486 |

| 19.2 | Functional Description | 486 |

|

19.2.1

Upstream Mode |

486 | |

|

19.2.2

Downstream JTAG Enable Mode |

487 | |

|

19.2.3

Downstream Digital Signature Mode |

487 | |

|

19.2.4

HMAC eFuse Configuration |

488 | |

|

19.2.5

HMAC Process (Detailed) |

489 | |

| 19.3 | HMAC Algorithm Details | 490 |

|

19.3.1

Padding Bits |

491 | |

|

19.3.2

HMAC Algorithm Structure |

491 | |

|

19.4

19.5 |

Register Summary

Registers |

494

496 |

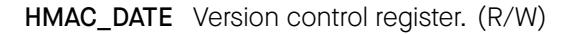

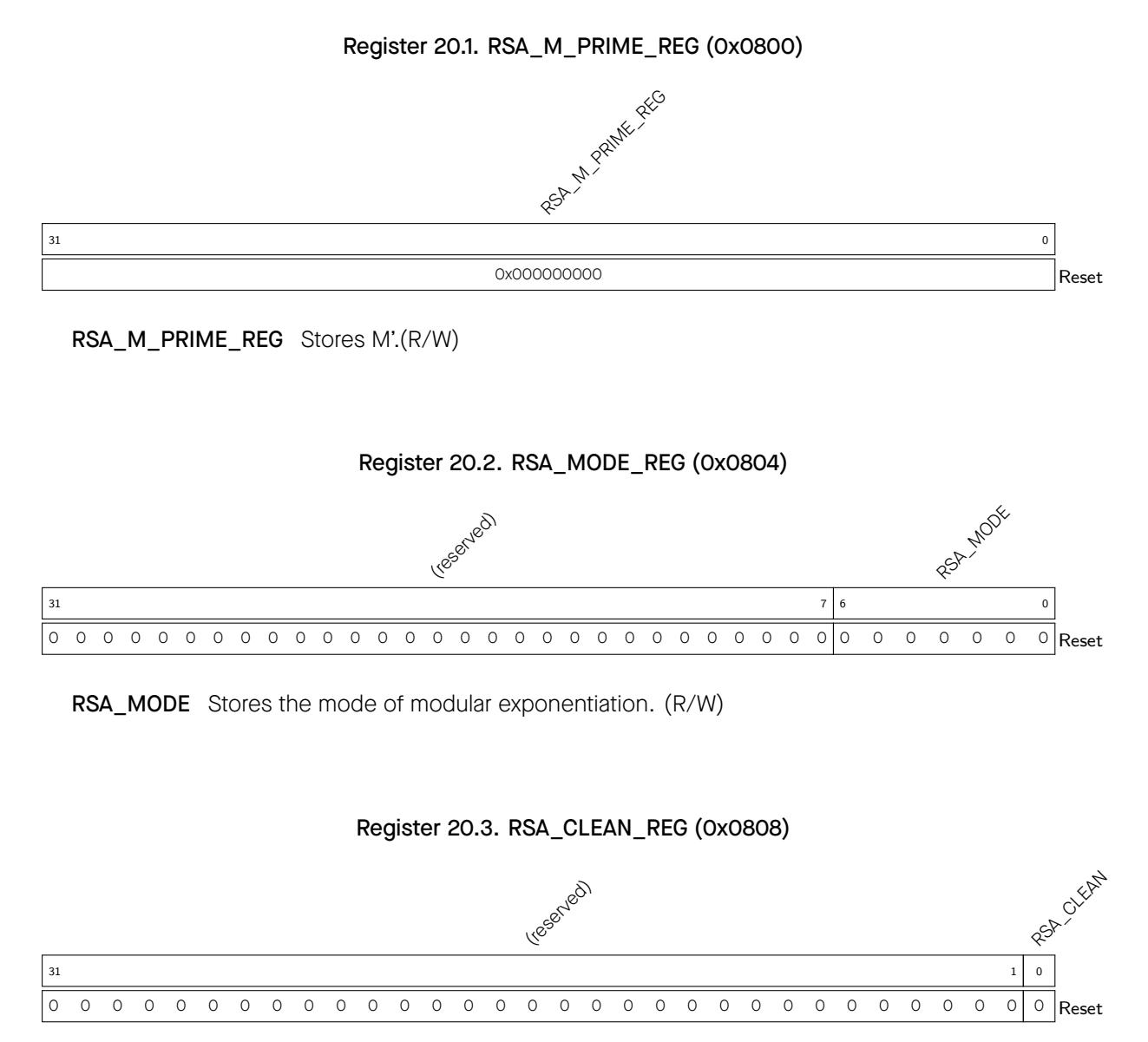

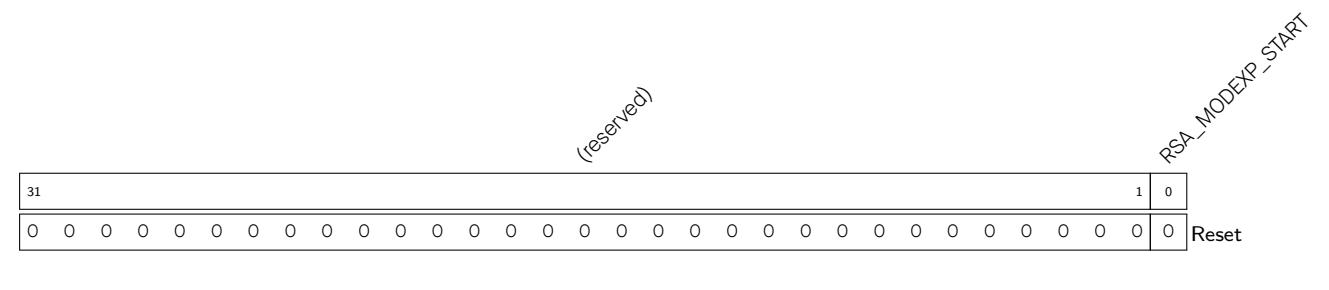

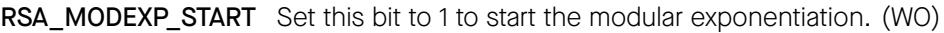

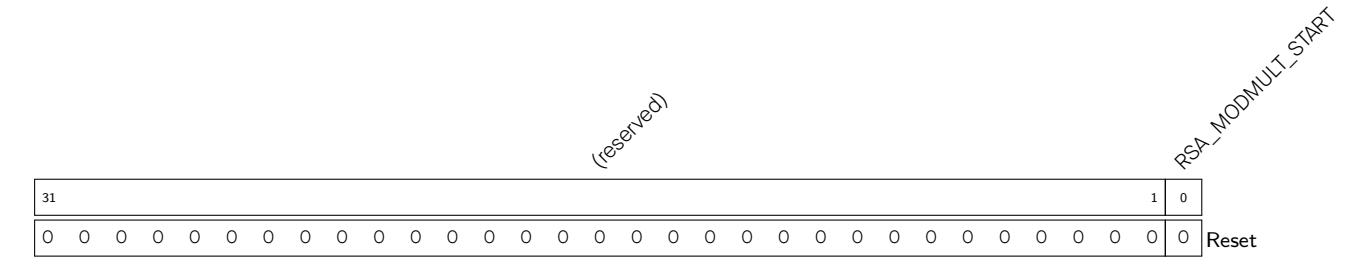

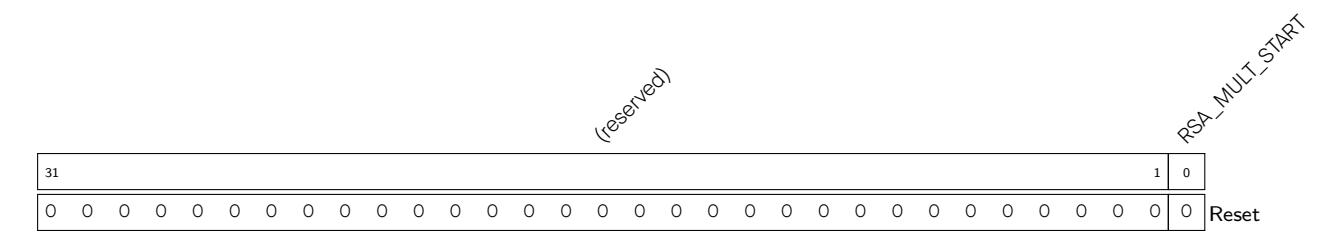

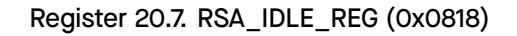

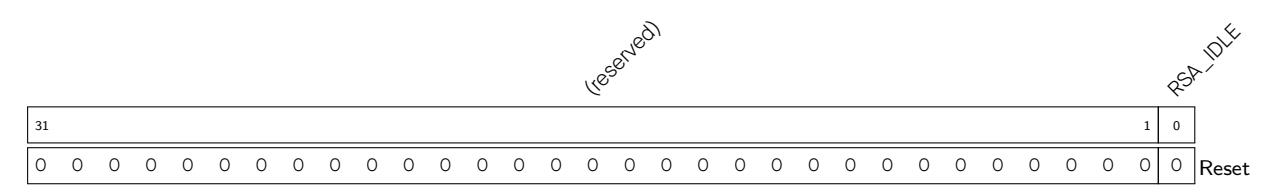

| 20 | RSA Accelerator (RSA) | 502 |

|

20.1

20.2 |

Introduction

Features |

502

502 |

| 20.3 |

Functional Description

20.3.1 Large Number Modular Exponentiation |

502

503 |

|

20.4

20.5 20.6 |

20.3.3 Large Number Multiplication

20.3.4 Options for Acceleration Memory Summary Register Summary Registers |

505

505 507 508 509 |

|---|---|---|

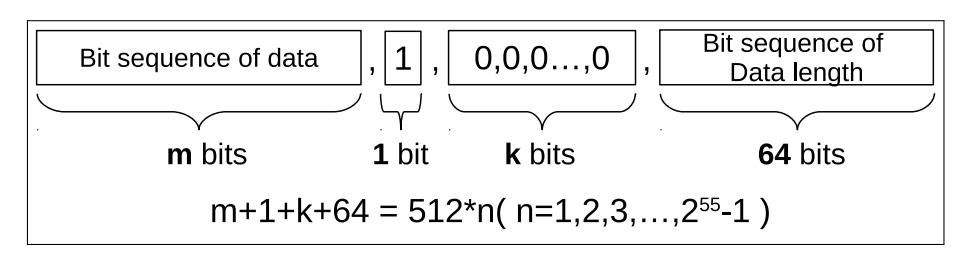

|

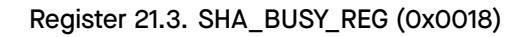

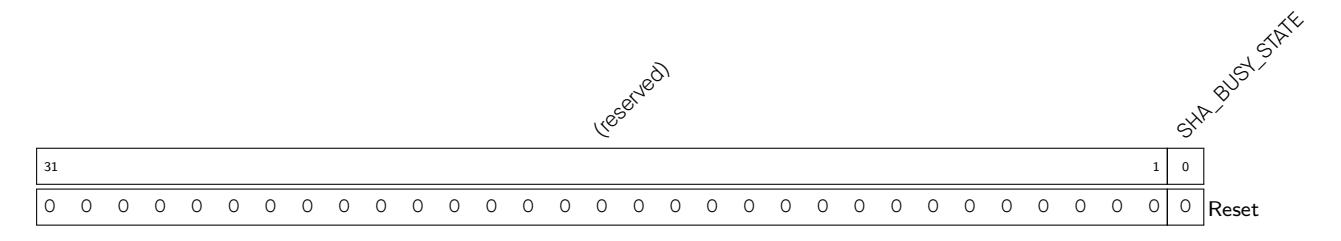

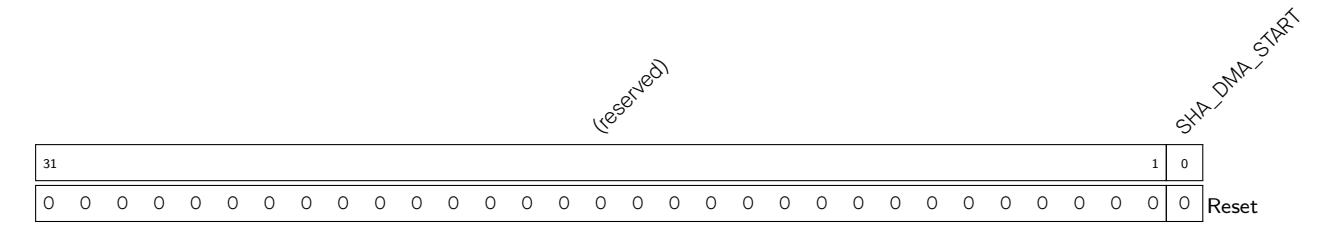

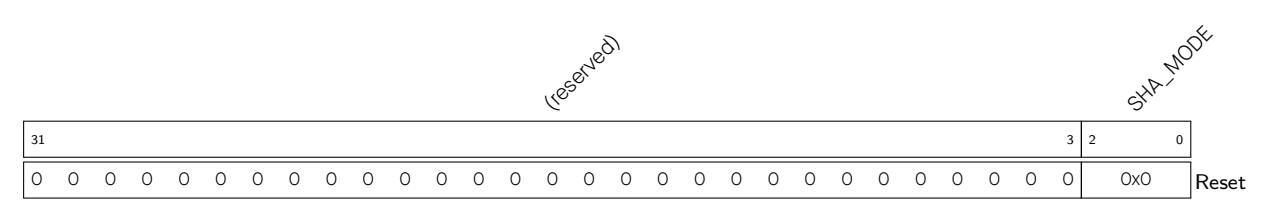

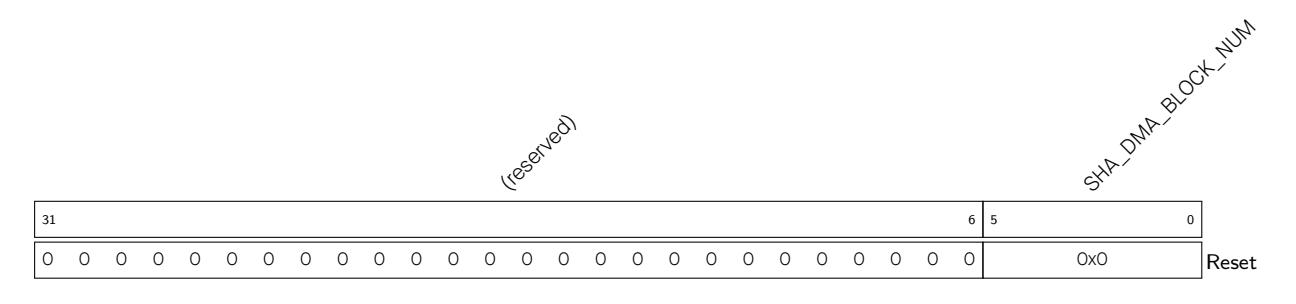

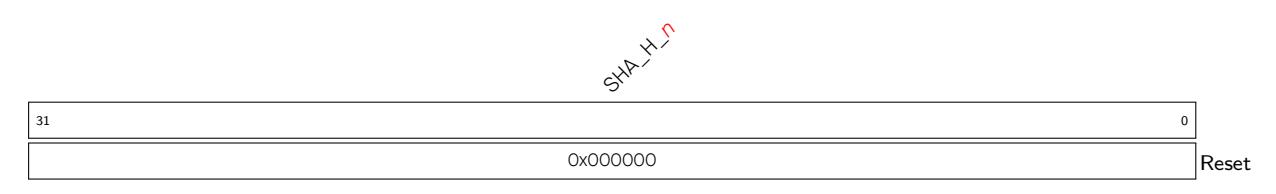

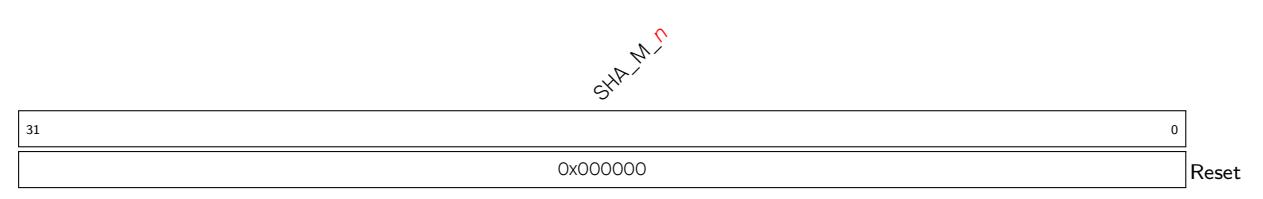

21

21.1 21.2 21.3 21.4 |

SHA Accelerator (SHA)

Introduction Features Working Modes Function Description 21.4.1 Preprocessing 21.4.1.1 Padding the Message 21.4.1.2 Parsing the Message Setting the Initial Hash Value 21.4.1.3 |

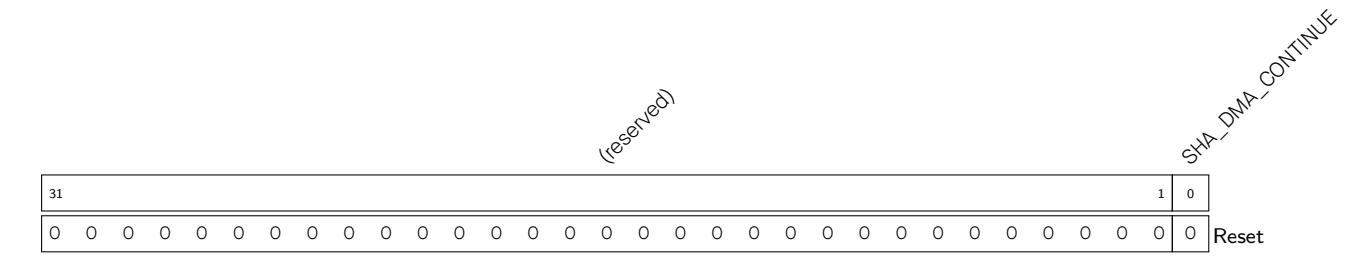

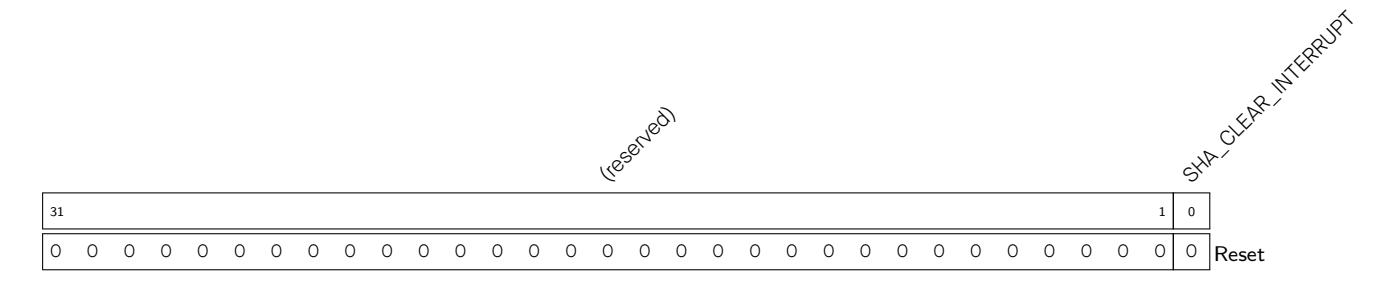

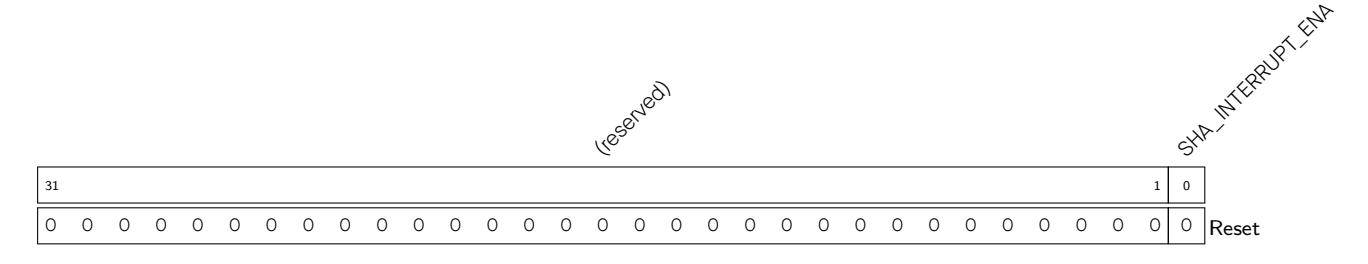

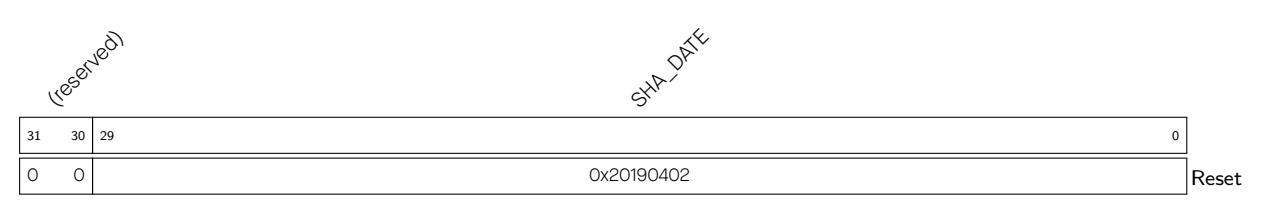

513

513 513 513 514 514 514 514 515 |

|

21.5

21.6 |

21.4.2 Hash Operation

Typical SHA Mode Process 21.4.2.1 DMA-SHA Mode Process 21.4.2.2 Message Digest 21.4.3 Interrupt 21.4.4 Register Summary Registers |

515

515 517 517 518 518 519 |

|

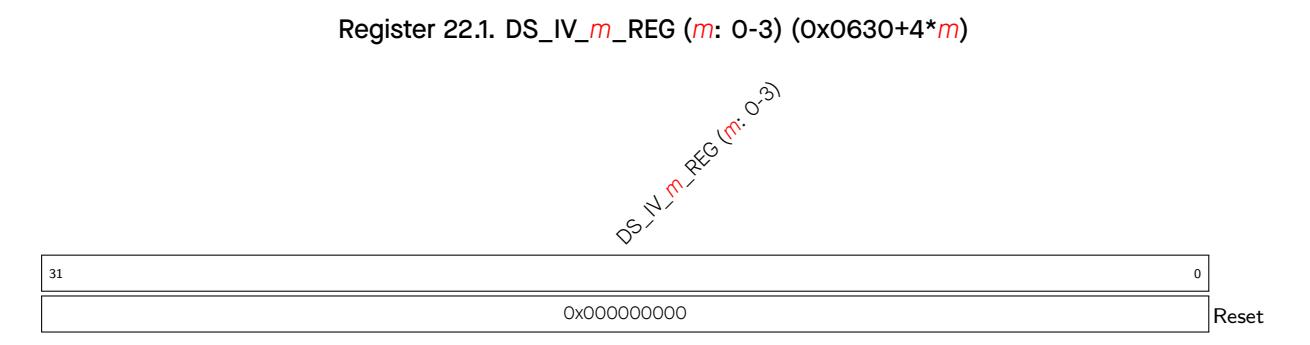

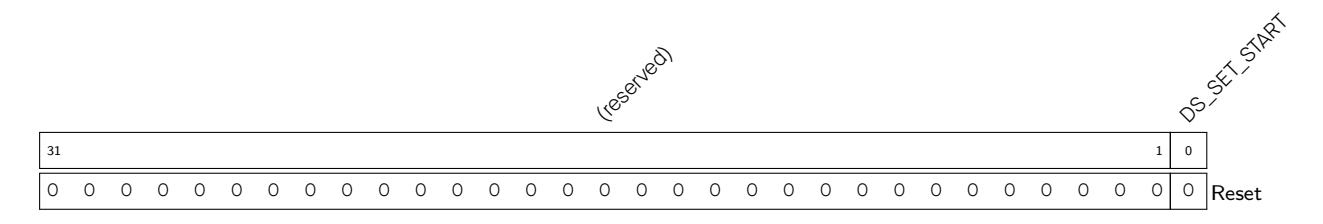

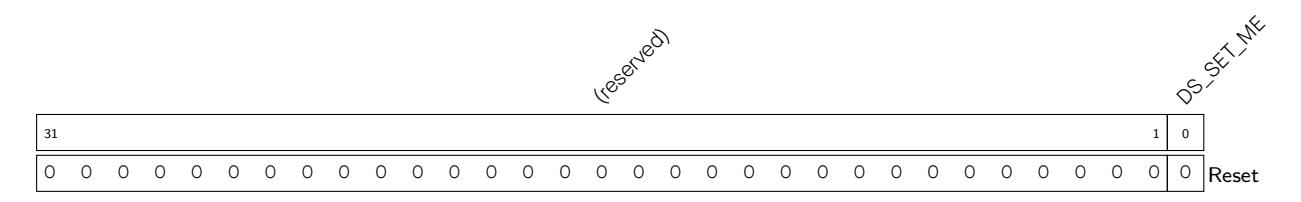

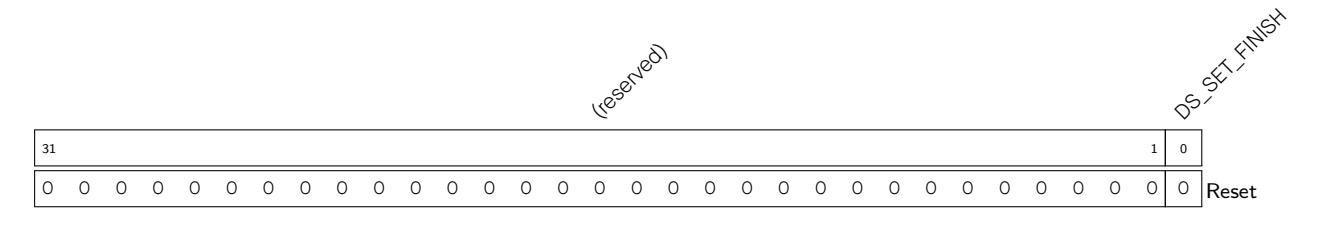

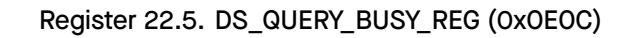

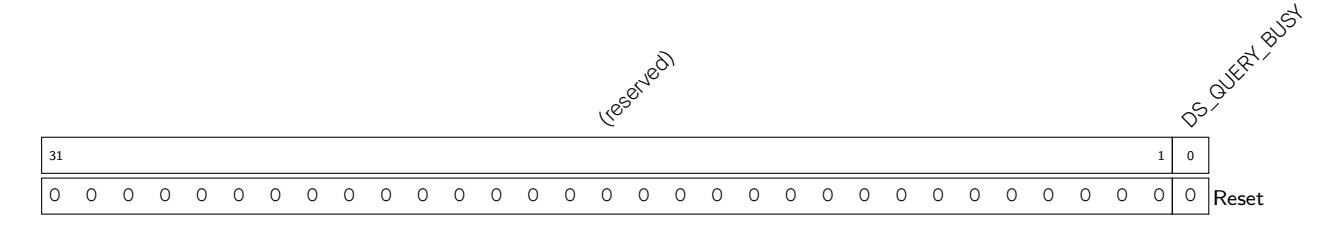

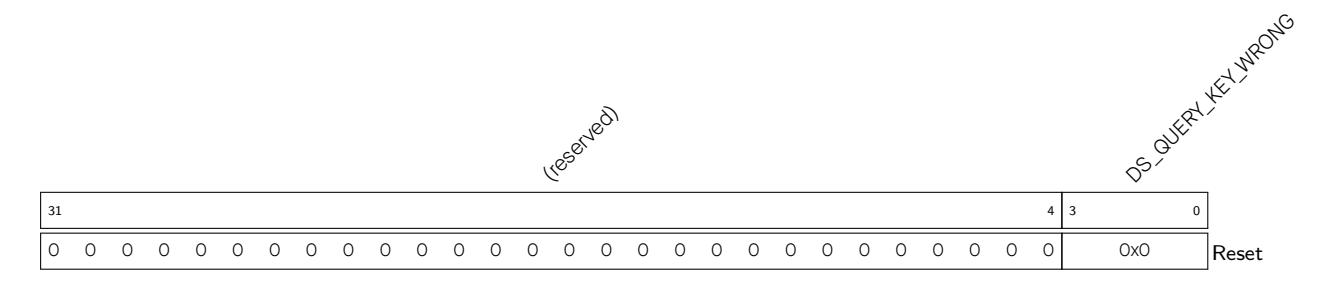

22

22.1 22.2 22.3 22.4 22.5 22.6 |

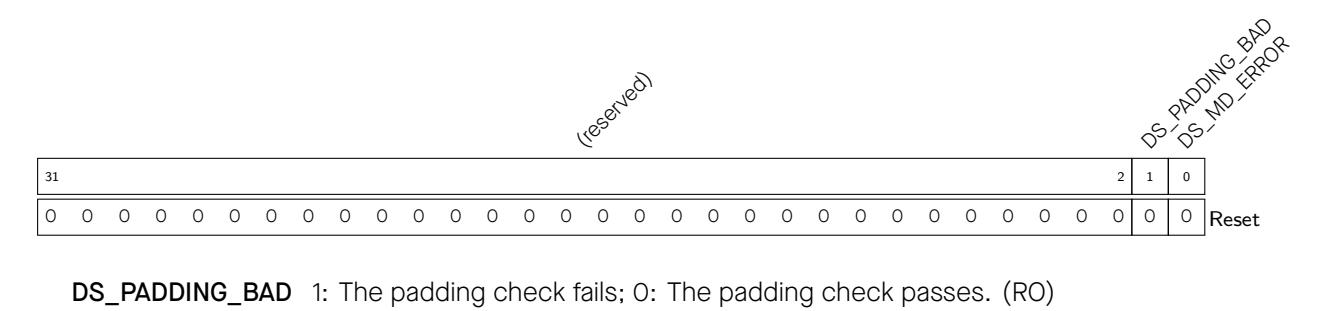

Digital Signature (DS)

Overview Features Functional Description 22.3.1 Overview 22.3.2 Private Key Operands 22.3.3 Software Prerequisites 22.3.4 DS Operation at the Hardware Level 22.3.5 DS Operation at the Software Level Memory Summary Register Summary Registers |

523

523 523 523 523 524 524 526 526 529 530 531 |

|

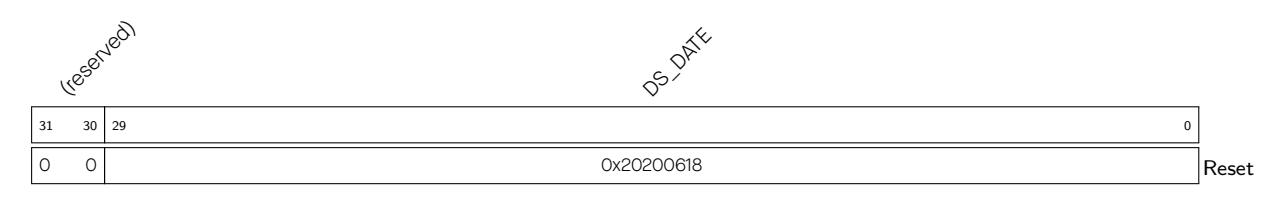

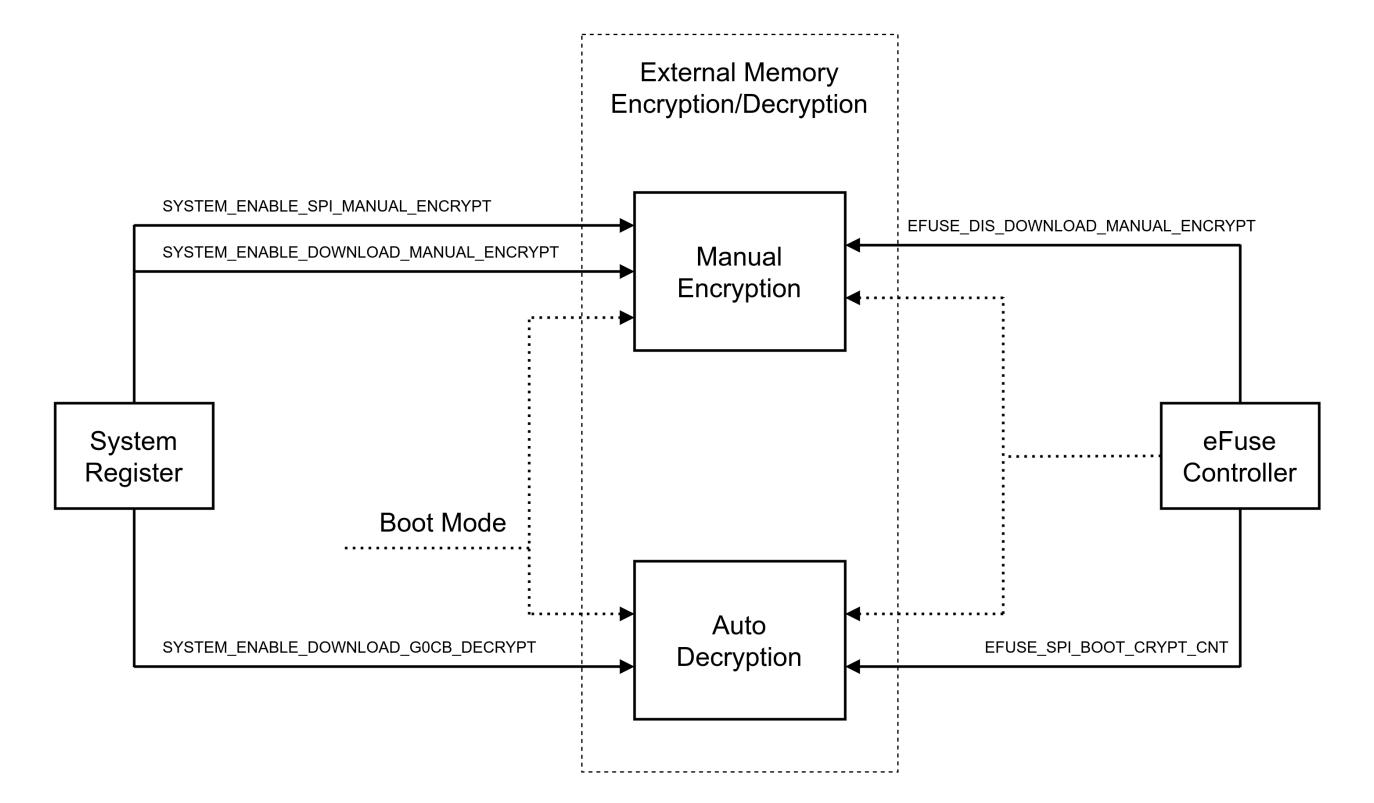

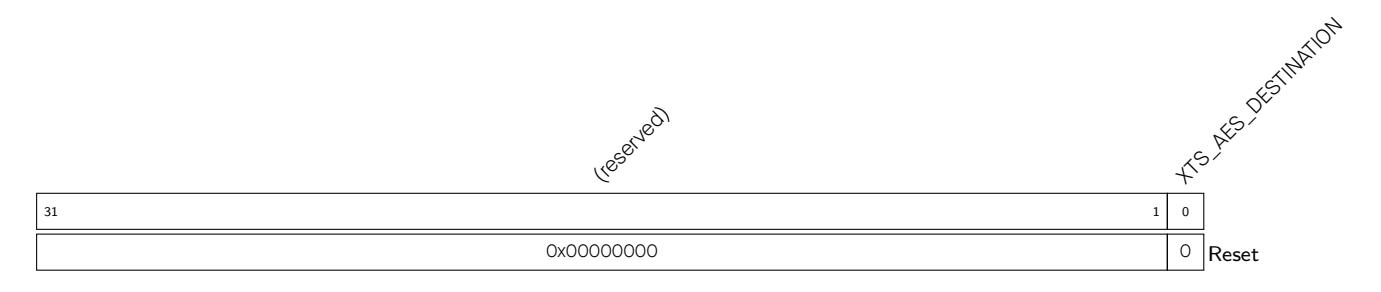

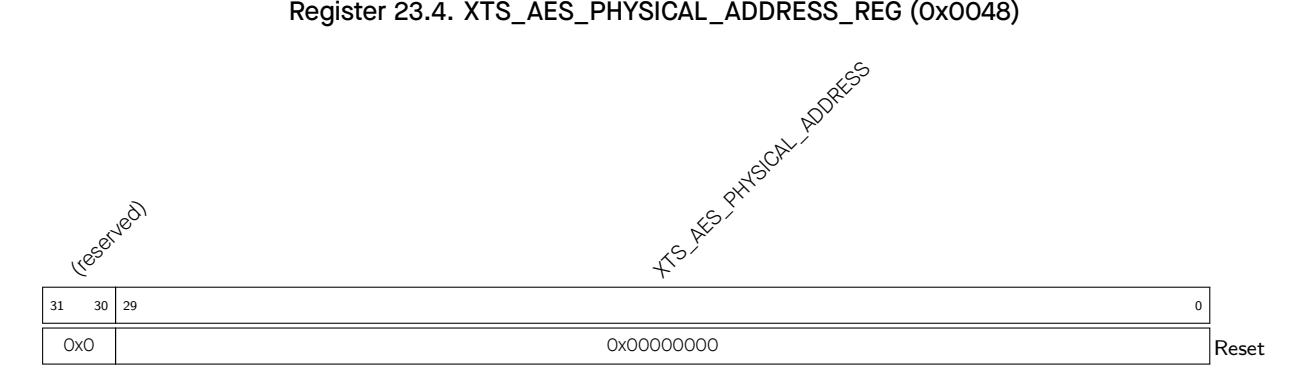

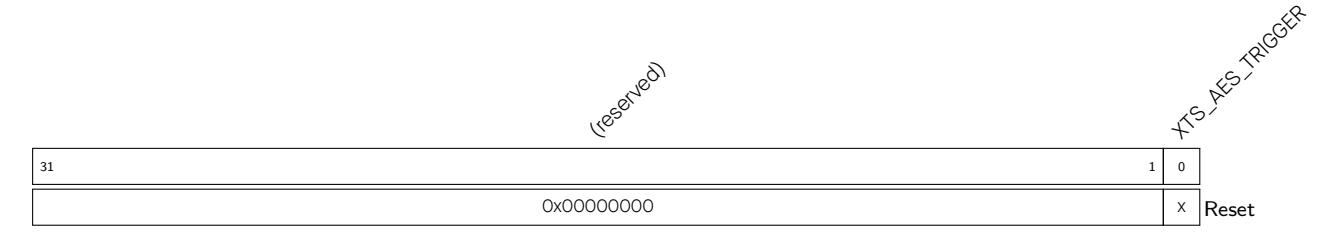

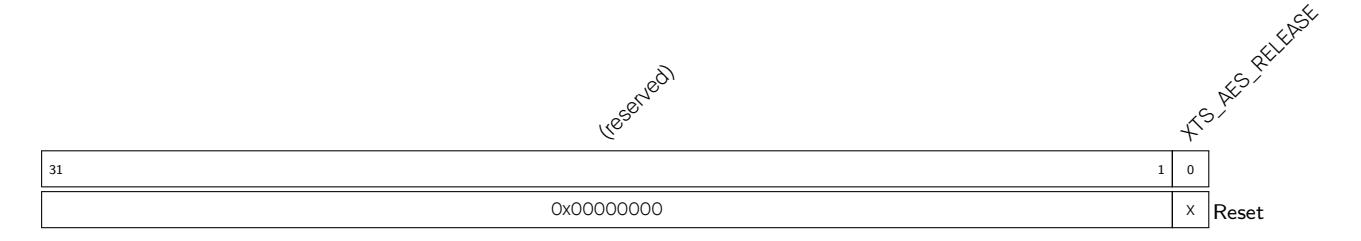

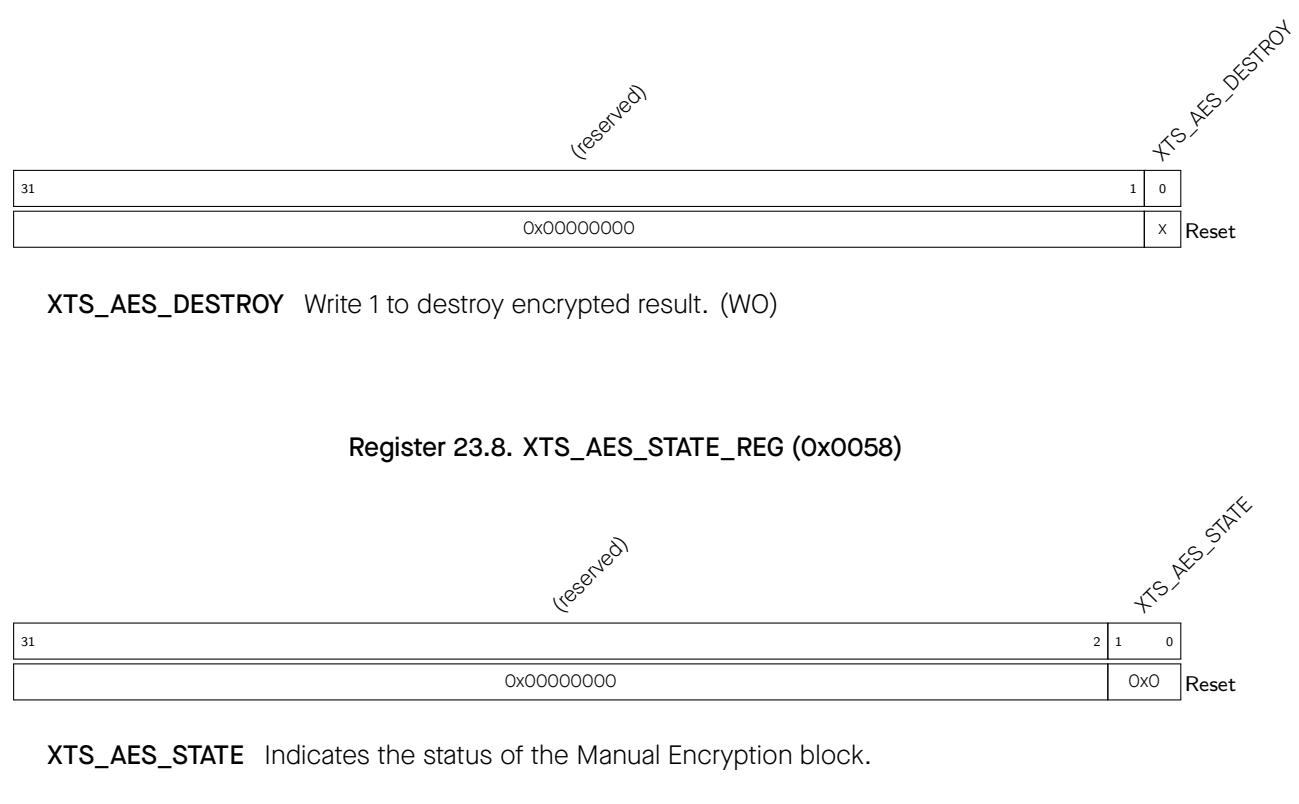

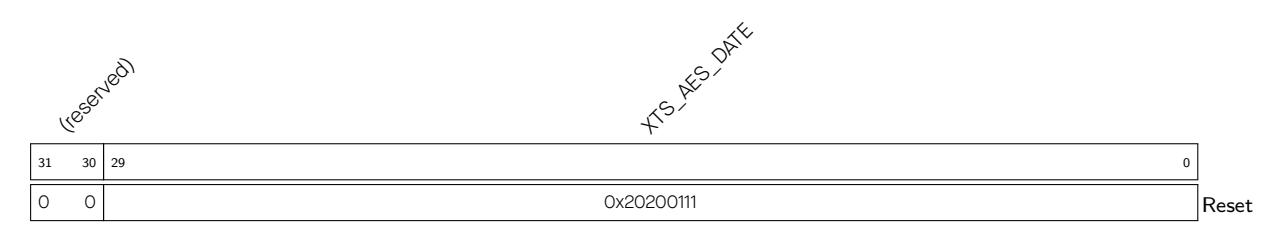

23

23.1 23.2 23.3 23.4 |

External Memory Encryption and Decryption (XTS_AES)

Overview Features Module Structure Functional Description 23.4.1 XTS Algorithm 23.4.2 Key 23.4.3 Target Memory Space 23.4.4 Data Writing 23.4.5 Manual Encryption Block |

534

534 534 534 535 535 536 536 537 537 |

| Contents | GoBack | |

| 23.5 |

23.4.6

Auto Decryption Block Software Process |

538

538 |

| 23.6 | Register Summary | 540 |

| 23.7 | Registers | 541 |

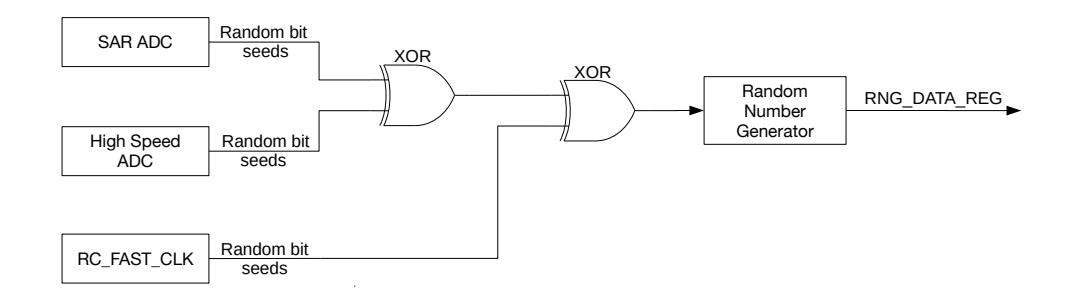

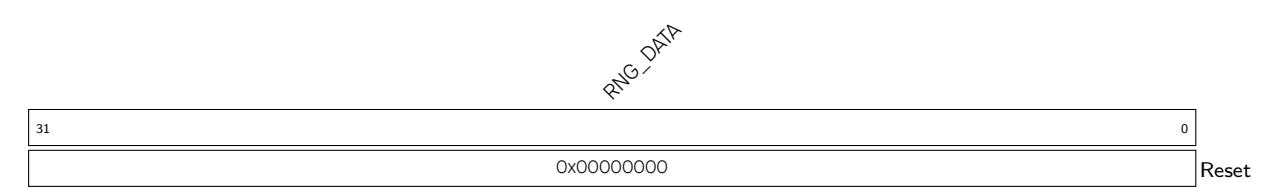

| 24 | Random Number Generator (RNG) | 544 |

|

24.1

24.2 |

Introduction

Features |

544

544 |

| 24.3 | Functional Description | 544 |

| 24.4 | Programming Procedure | 545 |

|

24.5

24.6 |

Register Summary

Register |

545

546 |

| 25 | Clock Glitch Detection | 547 |

| 25.1 | Overview | 547 |

| 25.2 | Functional Description | 547 |

|

25.2.1

Clock Glitch Detection 25.2.2 Reset |

547

547 |

|

| V | Connectivity Interface | 548 |

| 26 | UART Controller (UART) | 549 |

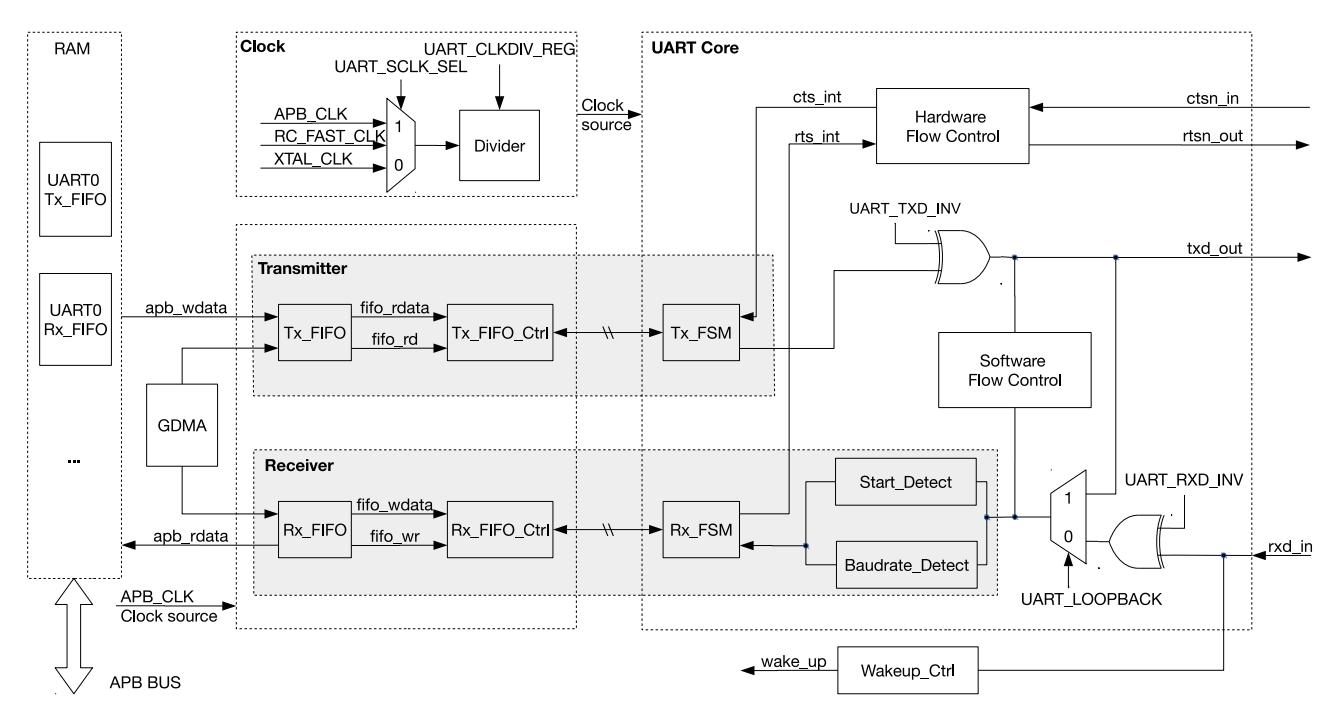

| 26.1 | Overview | 549 |

| 26.2 | Features | 549 |

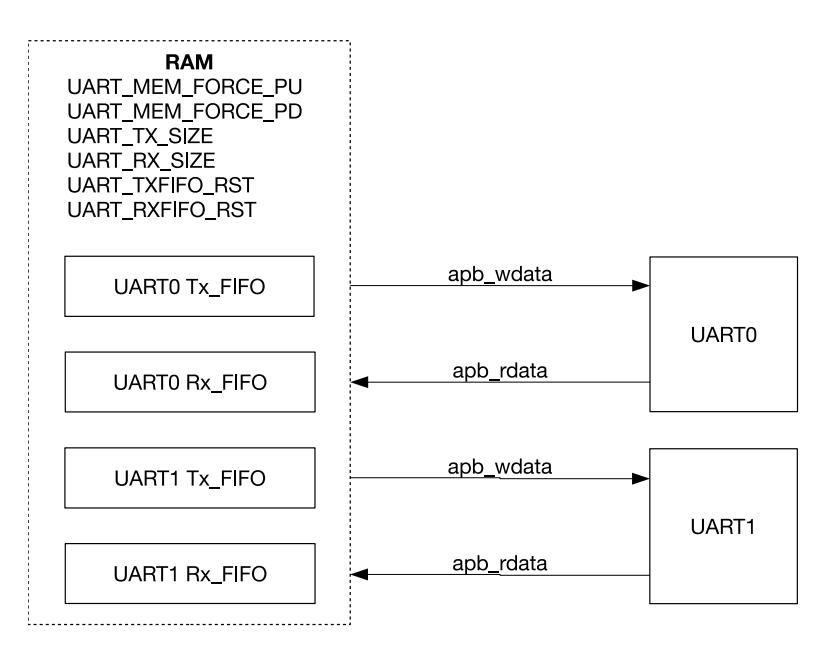

| 26.3 | UART Structure | 550 |

| 26.4 | Functional Description | 551 |

|

26.4.1

Clock and Reset |

551 | |

|

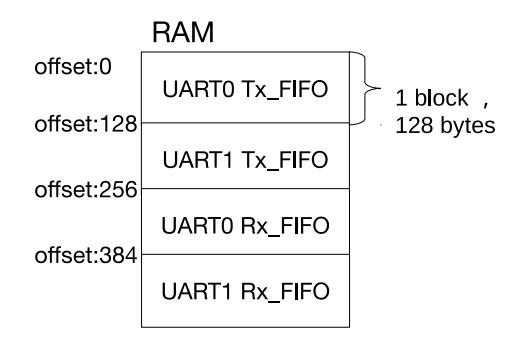

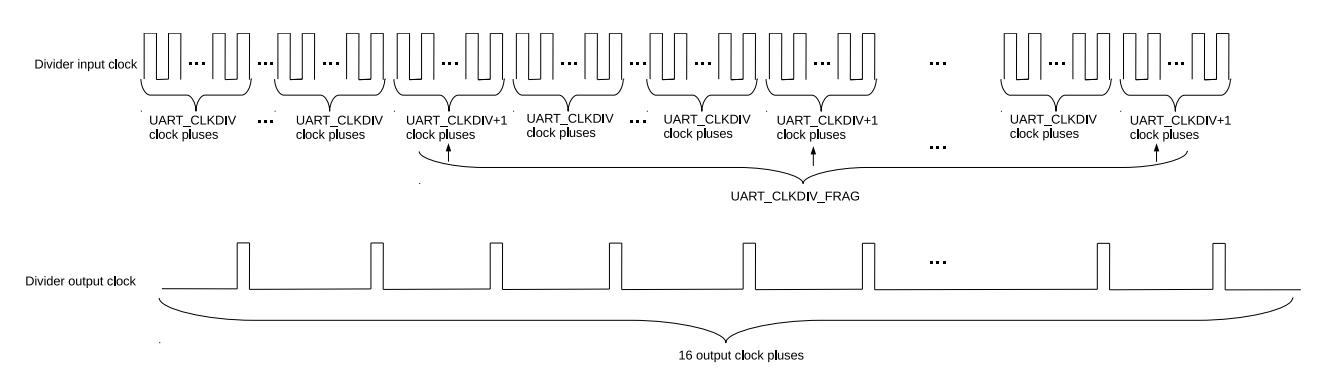

26.4.2

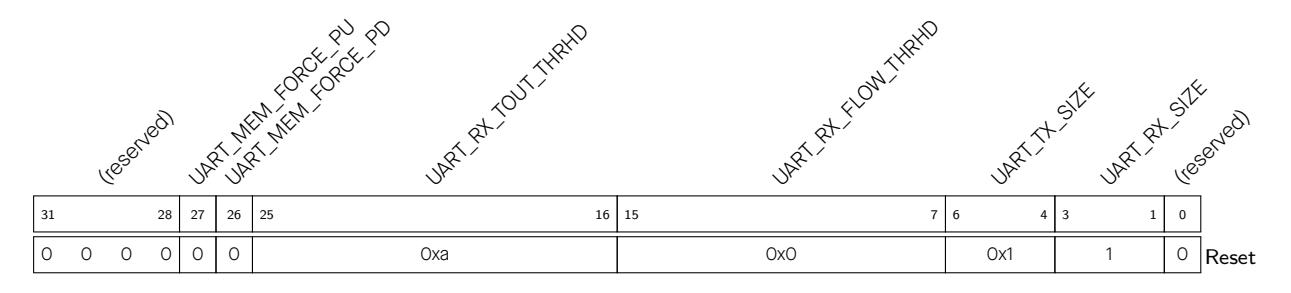

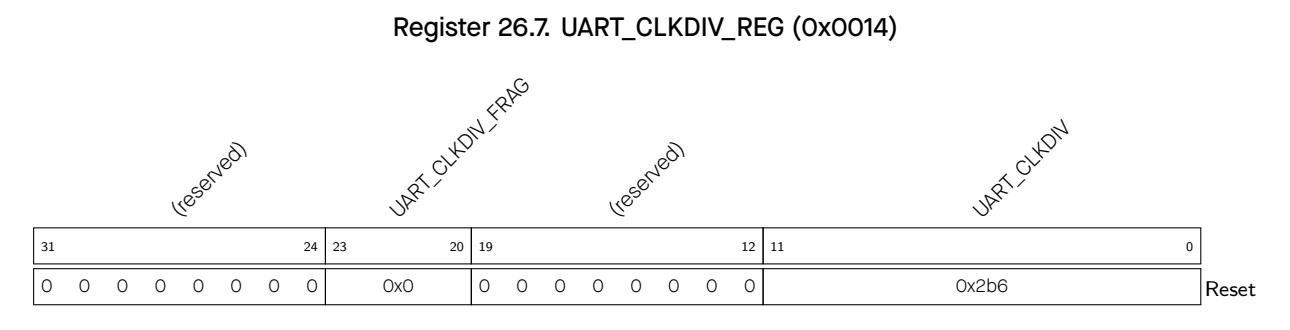

UART RAM 26.4.3 Baud Rate Generation and Detection |

552

553 |

|

|

26.4.3.1

Baud Rate Generation |

553 | |

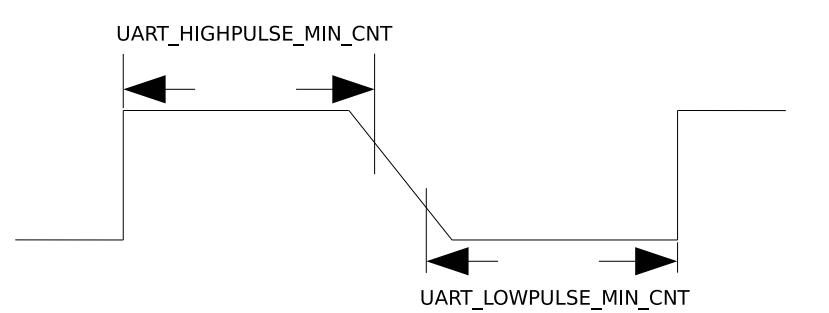

|

26.4.3.2

Baud Rate Detection |

554 | |

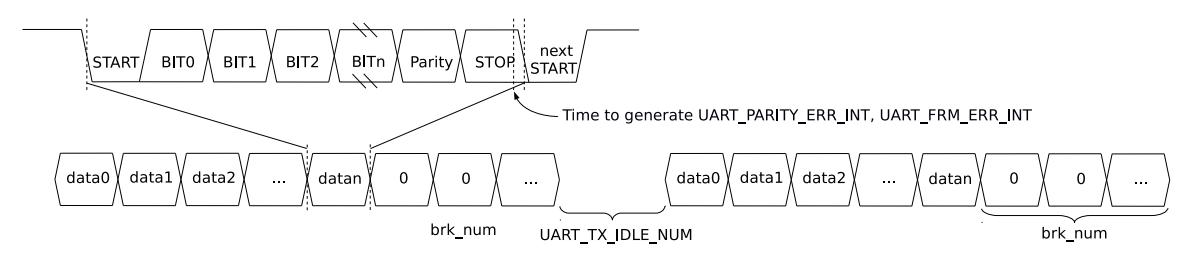

|

26.4.4

UART Data Frame |

555 | |

|

26.4.5

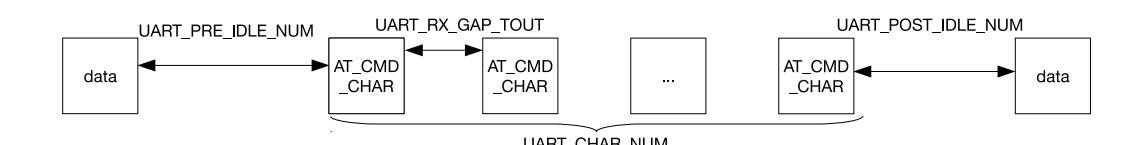

AT_CMD Character Structure |

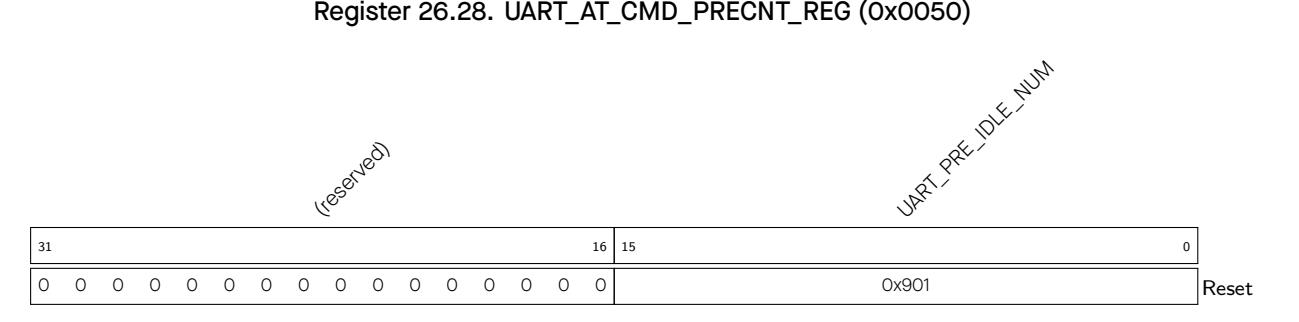

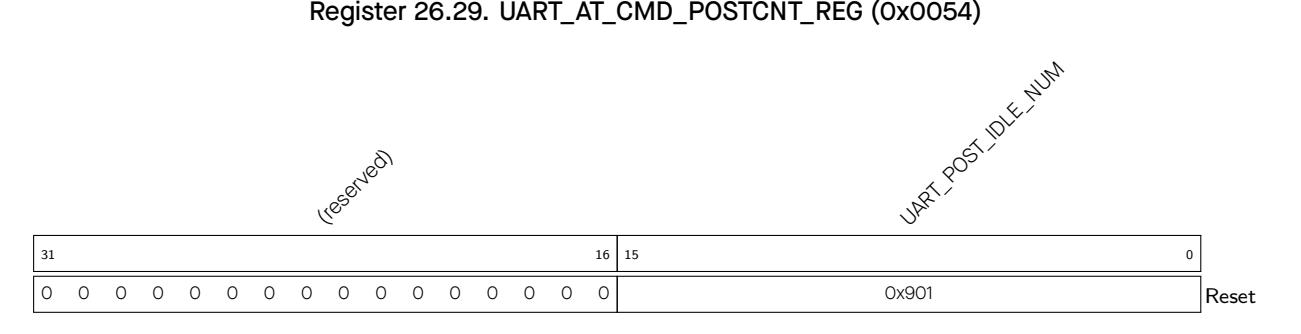

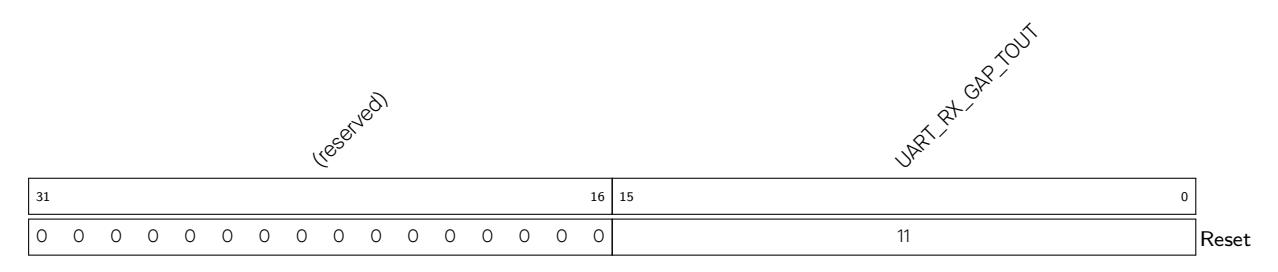

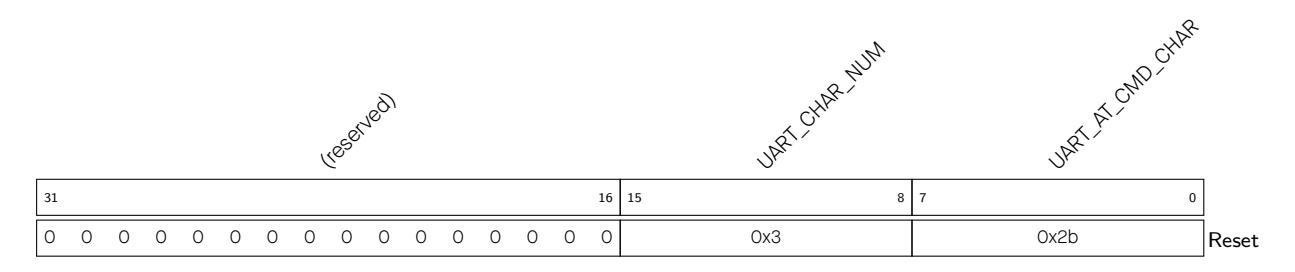

556 | |

|

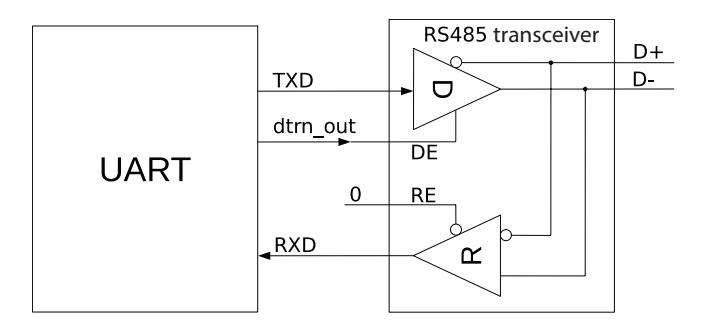

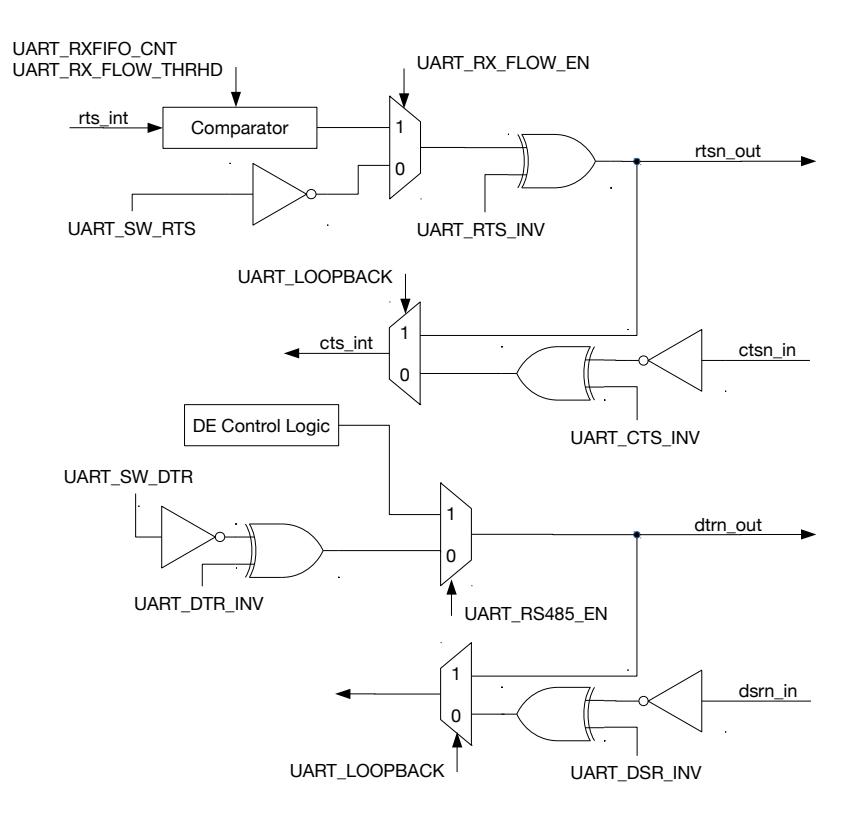

26.4.6

RS485 |

556 | |

|

26.4.6.1

Driver Control |

556 | |

|

26.4.6.2

Turnaround Delay |

557 | |

|

26.4.6.3

Bus Snooping |

557 | |

|

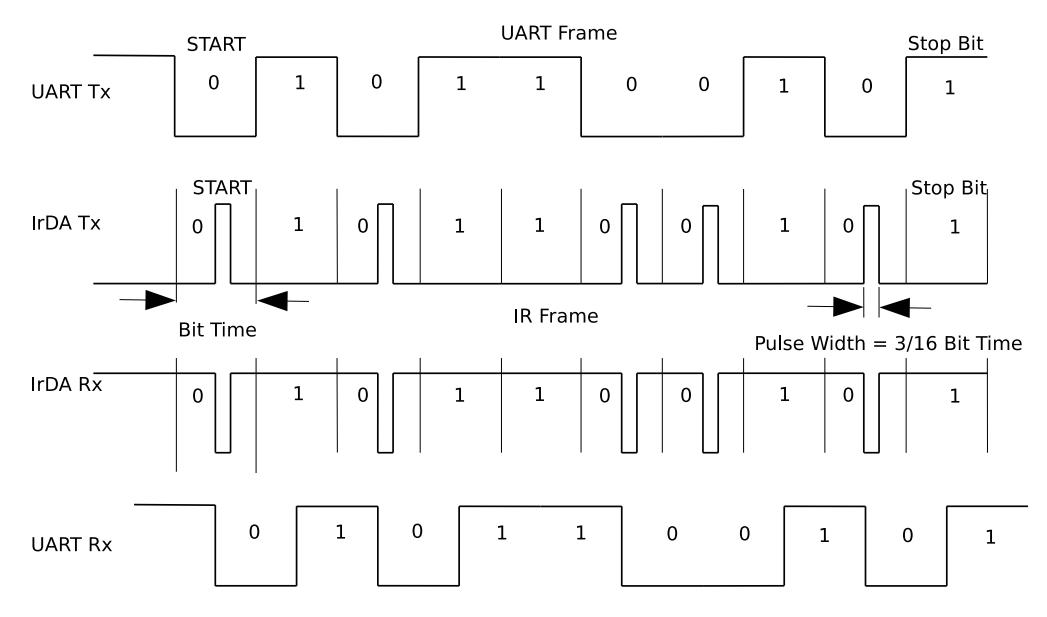

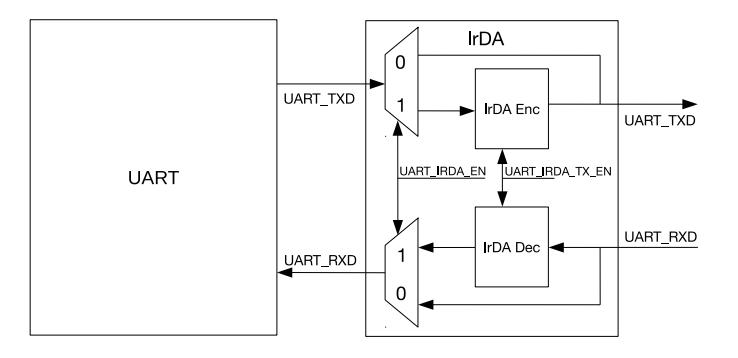

26.4.7

IrDA |

557 | |

|

26.4.8

Wake-up 26.4.9 Flow Control |

558

559 |

|

|

26.4.9.1

Hardware Flow Control |

559 | |

|

26.4.9.2

Software Flow Control |

560 | |

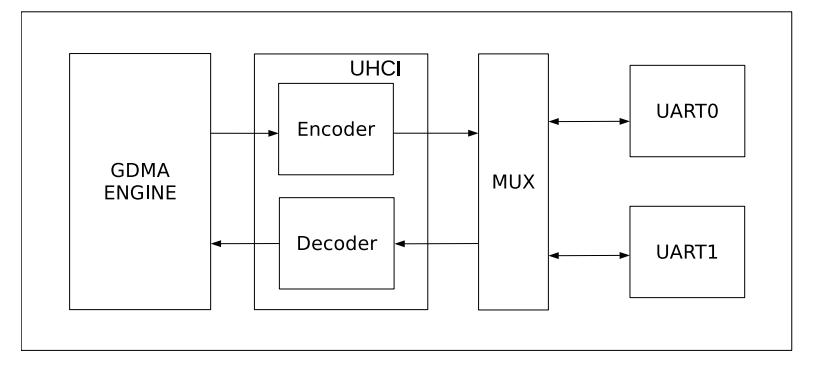

| 26.4.10 GDMA Mode | 561 | |

|

26.4.11

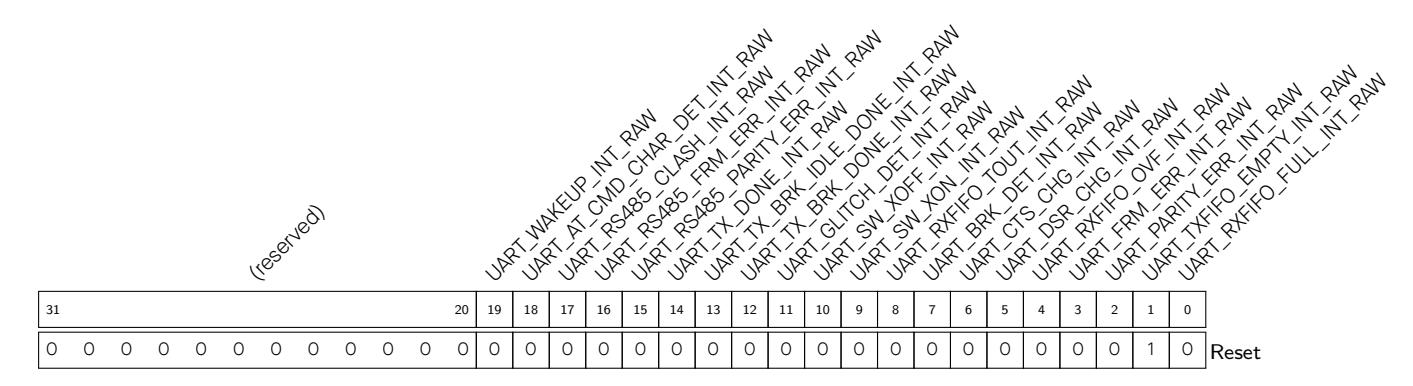

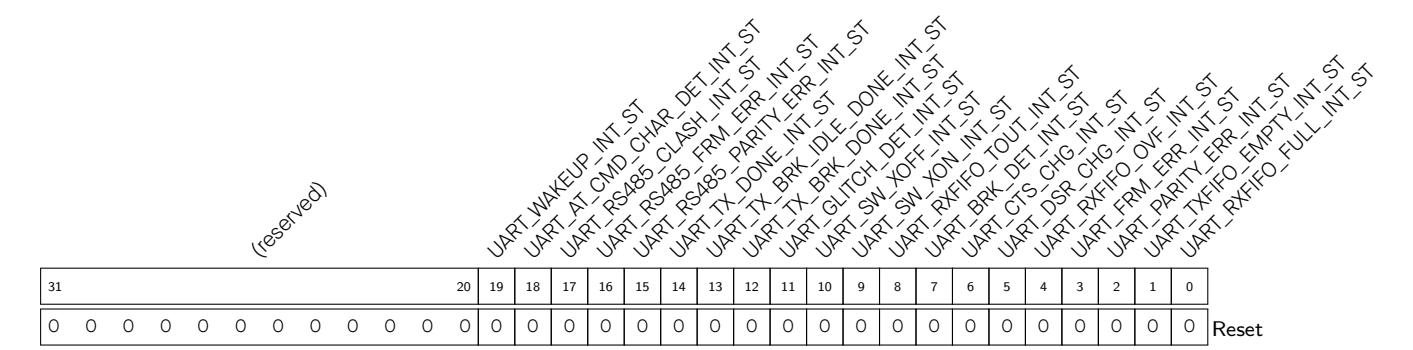

UART Interrupts |

561 | |

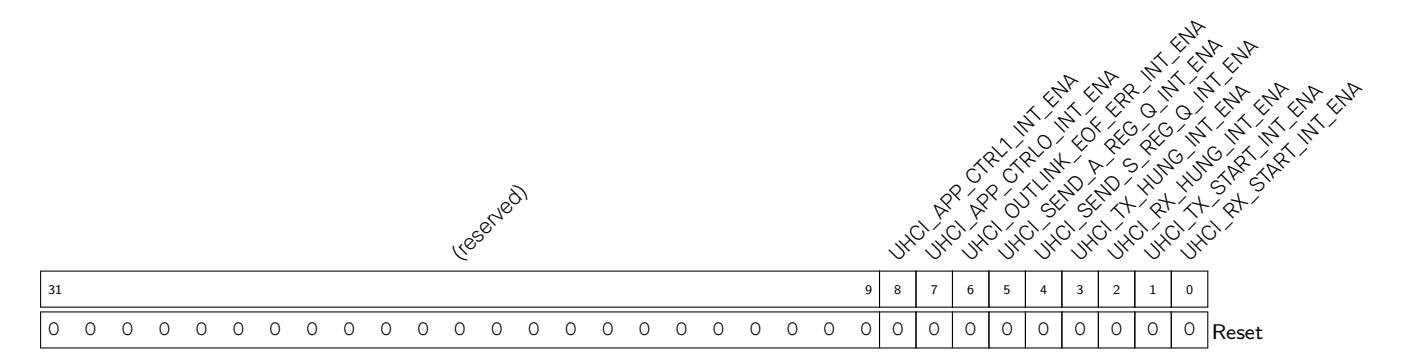

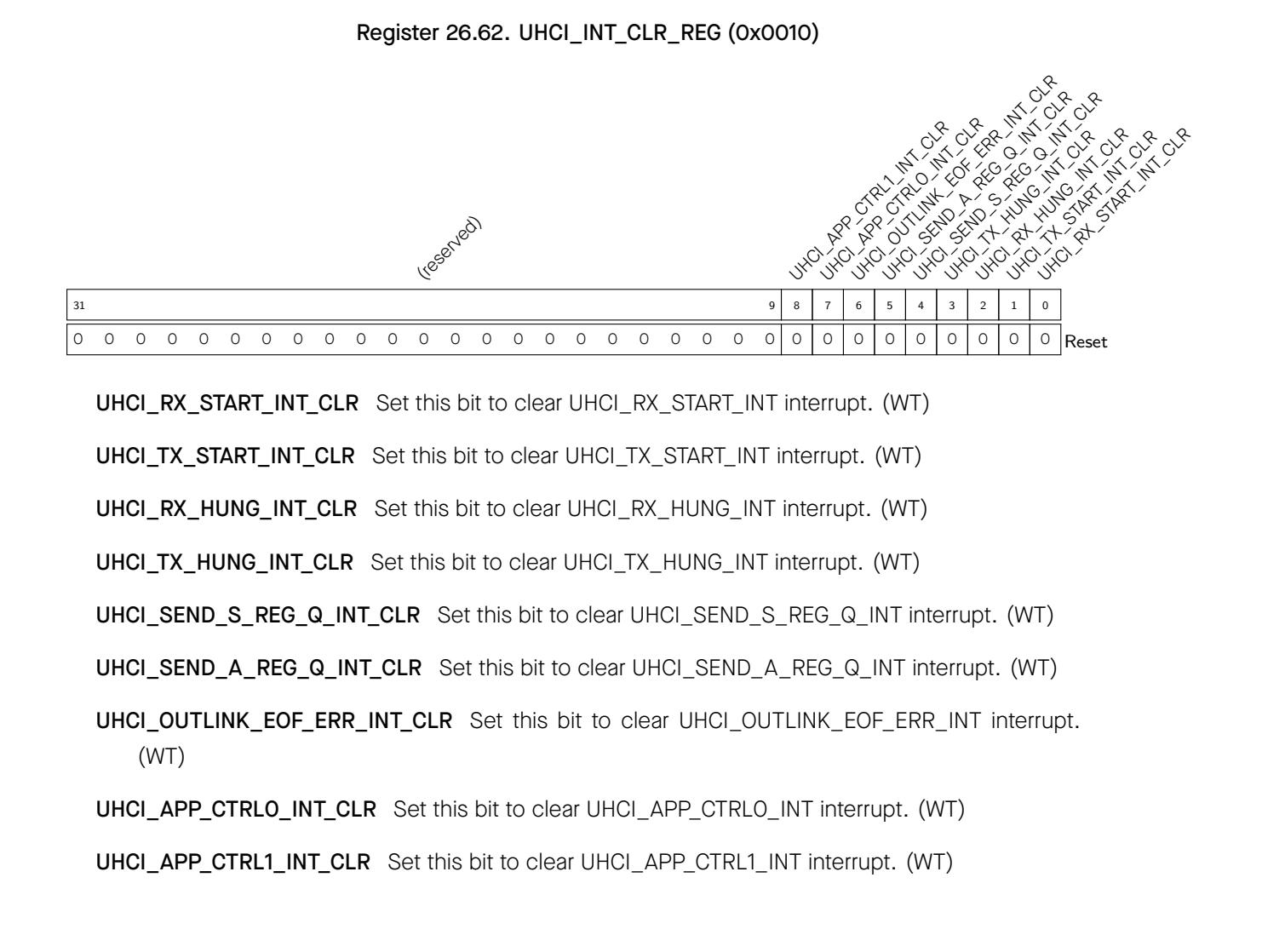

| 26.4.12 UHCI Interrupts | 562 | |

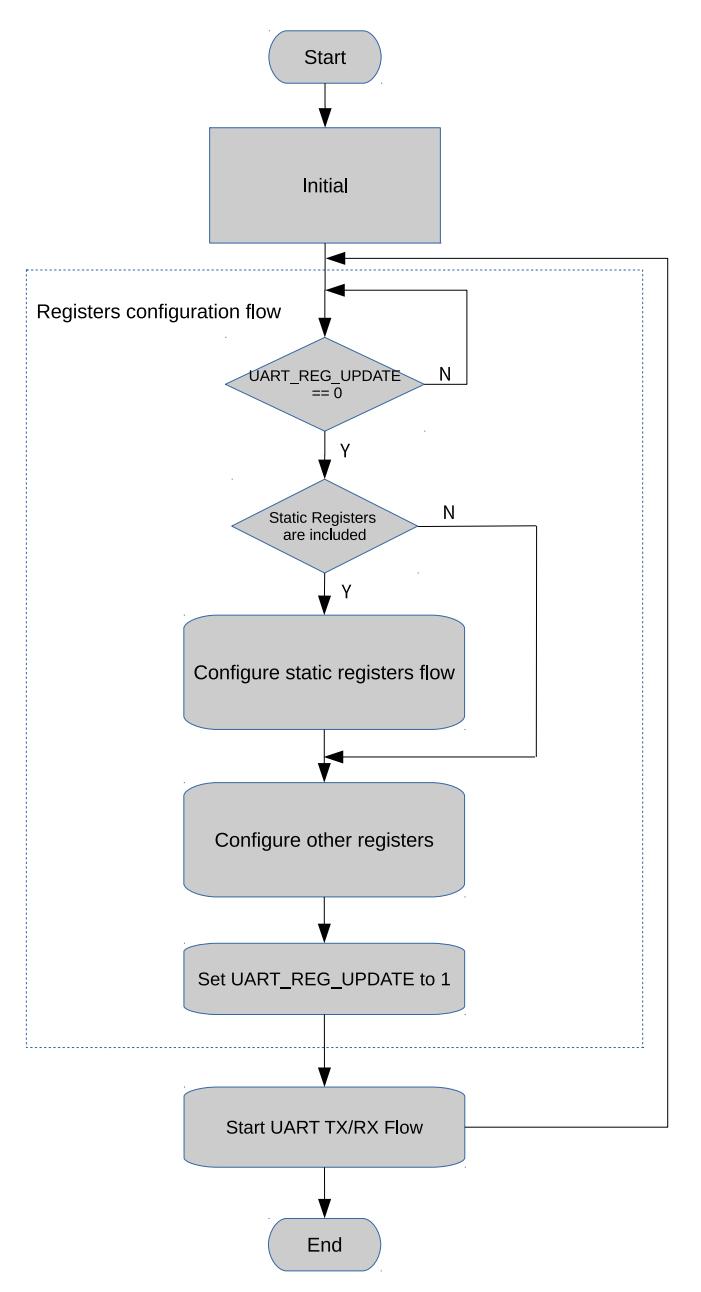

| 26.5.1 | Register Type | 563 | ||

|---|---|---|---|---|

| 26.5.11 | Synchronous Registers | 563 | ||

| 26.5.1.2 | Static Registers | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 26.5.1.3 | Immediate Registers | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 26.5.2 Detailed Steps | 565 | |||

| 26.5.2.1 | Initializing UARTn | 566 | ||

| 26.5.2.2 Configuring UARTn Communication | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | |||

| 26.5.2.3 Enabling UARTn | 566 | |||

| 26.6 | Register Summary | 568 | ||

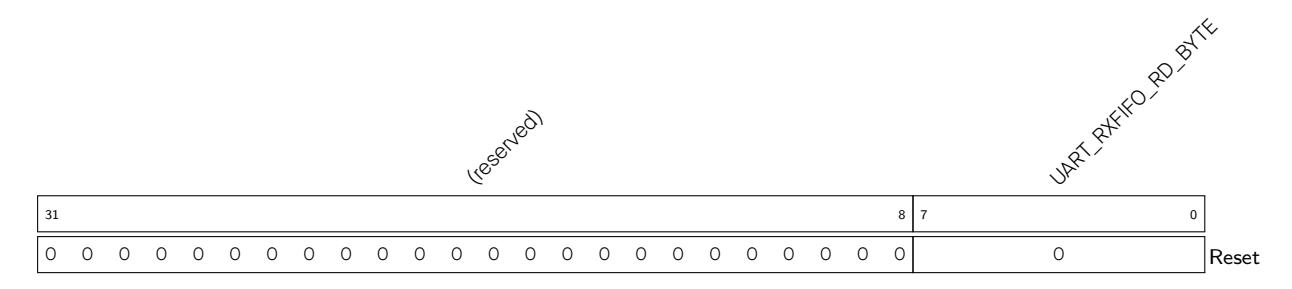

| 26.7 | Registers | 571 | ||

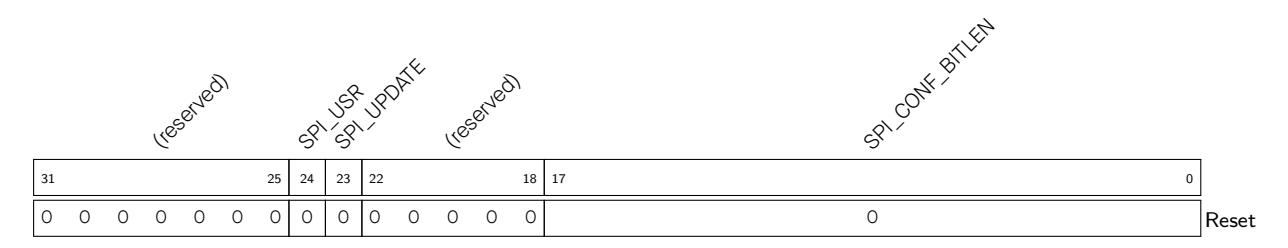

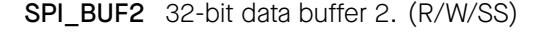

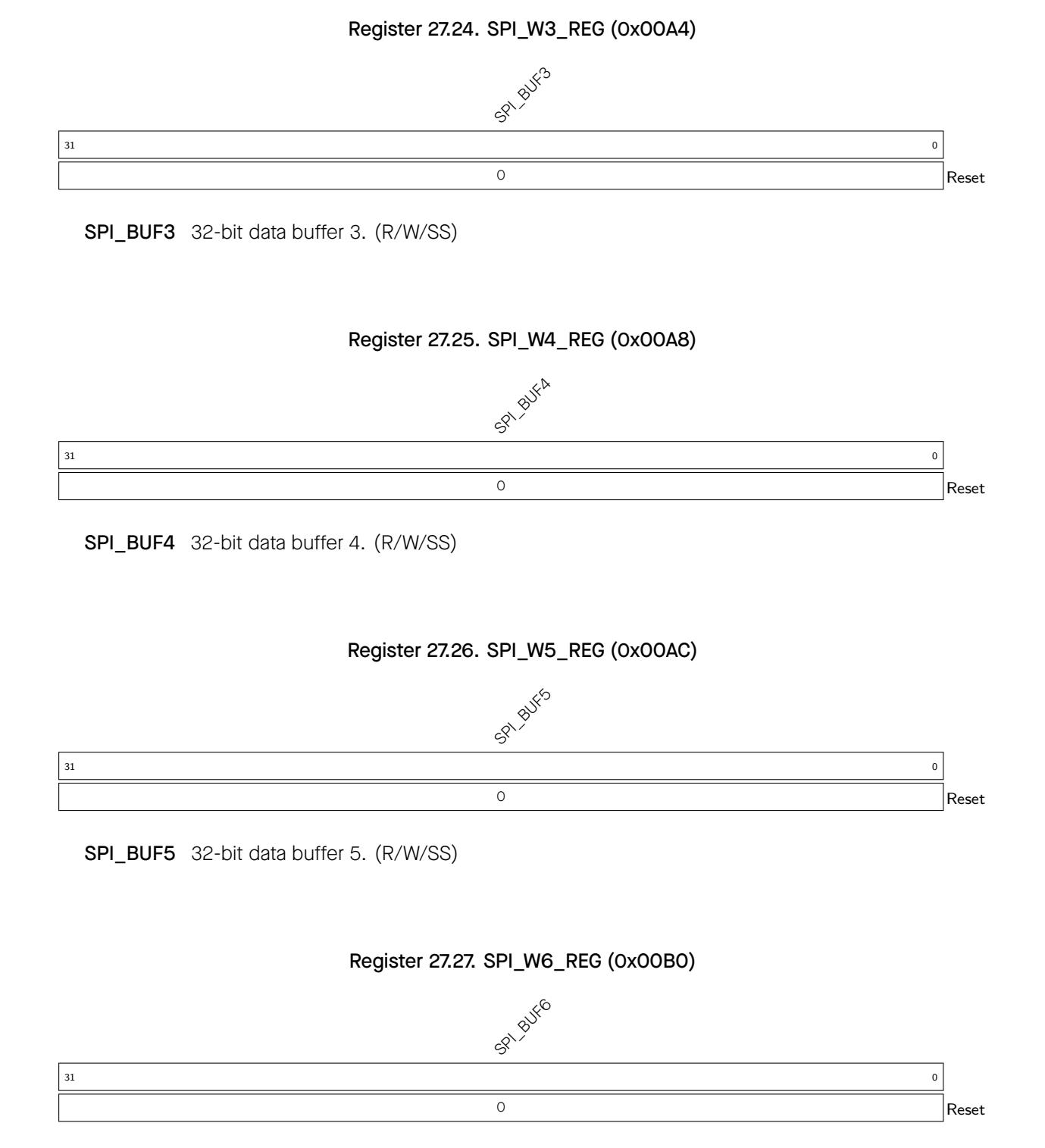

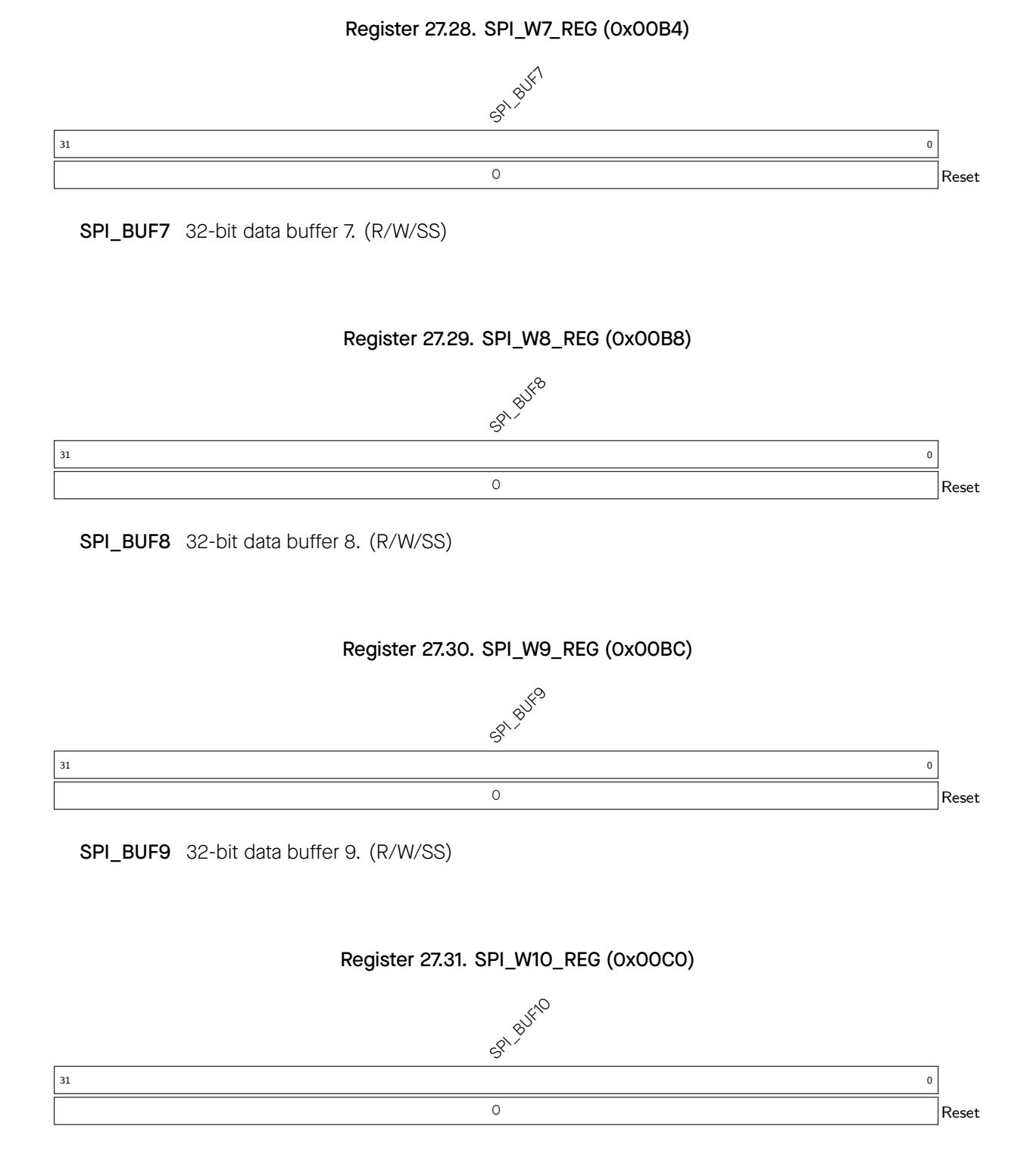

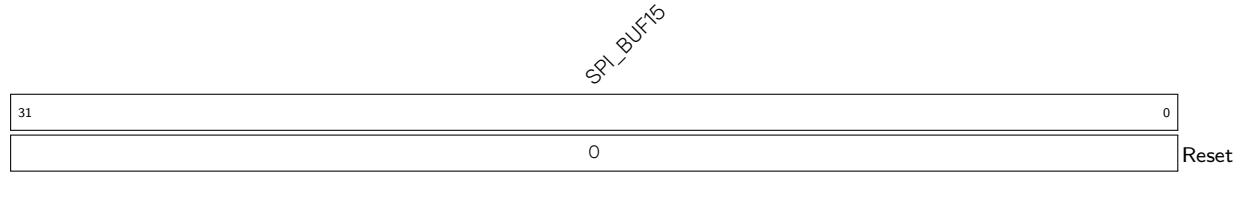

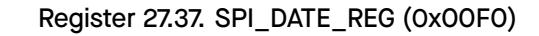

| 27 SPI Controller (SPI) | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | |||

| 27.1 | Overview | 608 | ||

|---|---|---|---|---|

| 27.2 | Glossary | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 27.3 | Features | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

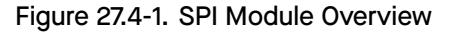

| 27.4 | Architectural Overview | 610 | ||

| 27.5 | Functional Description | 610 | ||

| 27.5.1 | Data Modes | 611 | ||

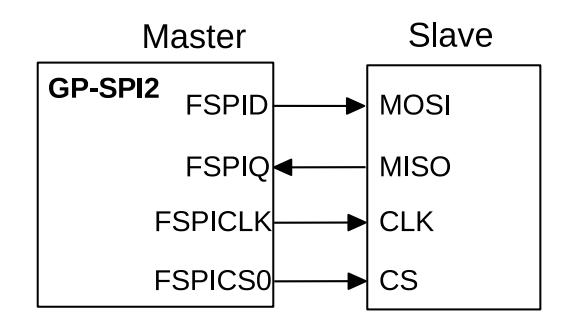

| 27.5.2 FSPI Bus Signal Mapping | 611 | |||

| 27.5.3 | Bit Read/Write Order Control | 614 | ||

| 27.5.4 | Transfer Modes | 614 | ||

|

CPU-Controlled Data Transfer

27.5.5 |

614 | |||

| 27.5.5.1 | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | 615 | ||

| 27.5.5.2 | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | 616 | ||

| 27.5.6 | DMA-Controlled Data Transfer | 616 | ||

| 27.5.6.1 | GDMA Configuration | 617 | ||

| 27.5.6.2 | GDMA TX/RX Buffer Length Control | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 27.5.7 | Data Flow Control in GP-SPI2 Master and Slave Modes | 618 | ||

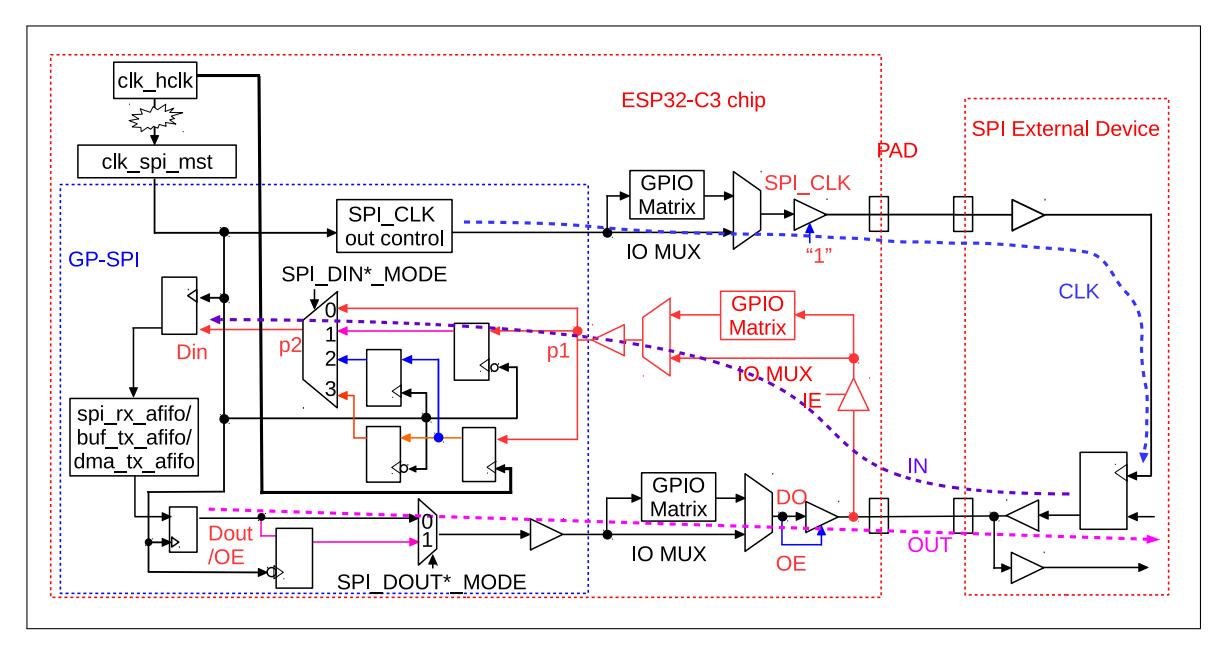

| 27.5.7.1 | GP-SPI2 Functional Blocks | 618 | ||

| 27.5.7.2 | Data Flow Control in Master Mode | 619 | ||

| 27.5.7.3 | Data Flow Control in Slave Mode | 620 | ||

|

GP-SPI2 Works as a Master

27.5.8 |

621 | |||

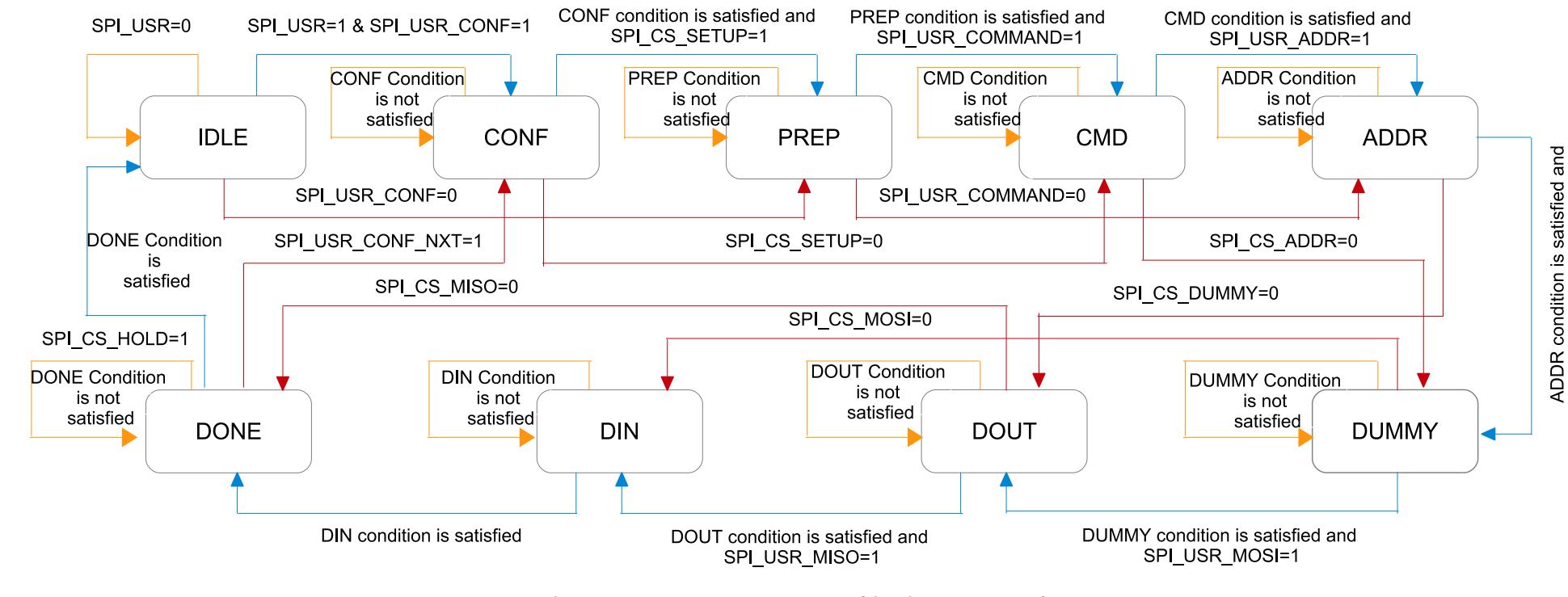

| 27.5.8.1 | State Machine | 621 | ||

| 27.5.8.2 | Register Configuration for State and Bit Mode Control | 623 | ||

| 27.5.8.3 | Full-Duplex Communication (1-bit Mode Only) | 626 | ||

| 27.5.8.4 | Half-Duplex Communication (1/2/4-bit Mode) | 627 | ||

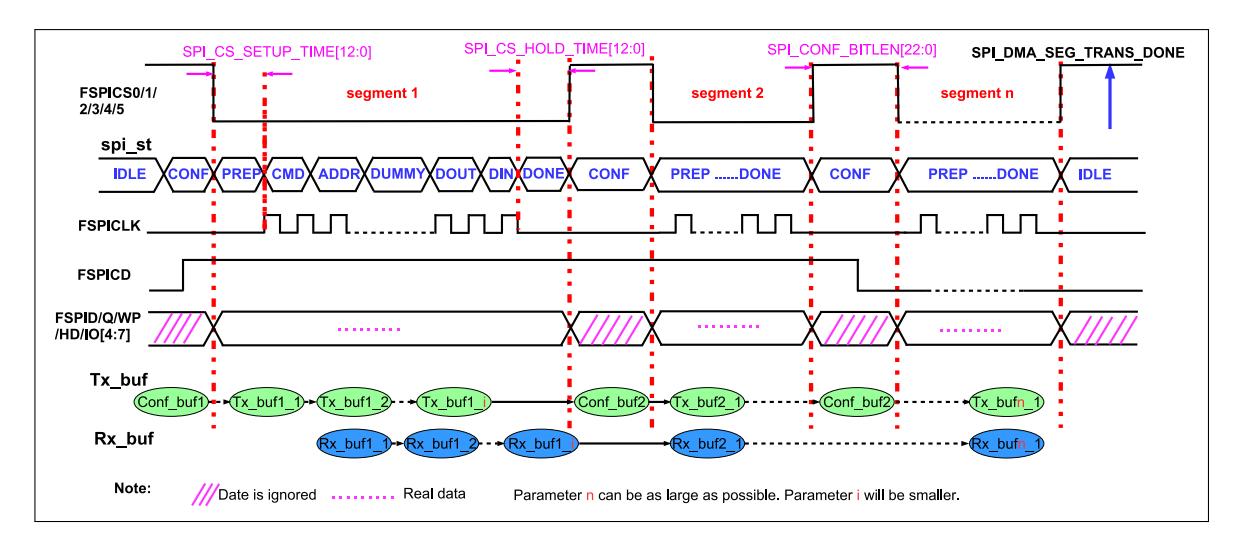

| 27.5.8.5 | DMA-Controlled Configurable Segmented Transfer | 629 | ||

| 27.5.9 | GP-SPI2 Works as a Slave | 633 | ||

| 27.5.9.1 | Communication Formats | 633 | ||

| 27.5.9.2 | Supported CMD Values in Half-Duplex Communication | 634 | ||

| 27.5.9.3 | Slave Single Transfer and Slave Segmented Transfer | 637 | ||

| 27.5.9.4 | Configuration of Slave Single Transfer | 637 | ||

| 27.5.9.5 | Configuration of Slave Segmented Transfer in Half-Duplex | 638 | ||

| 27.5.9.6 | Configuration of Slave Segmented Transfer in Full-Duplex | 638 | ||

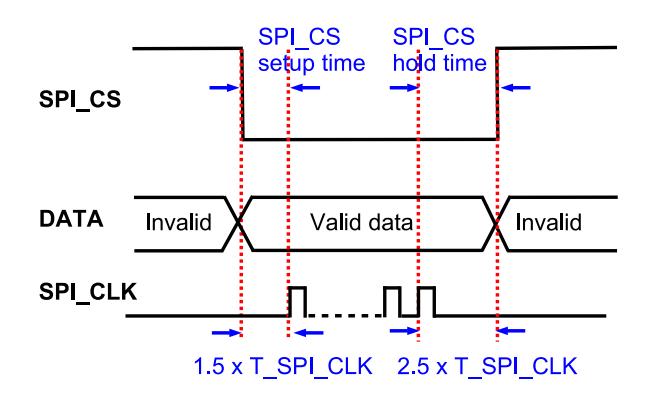

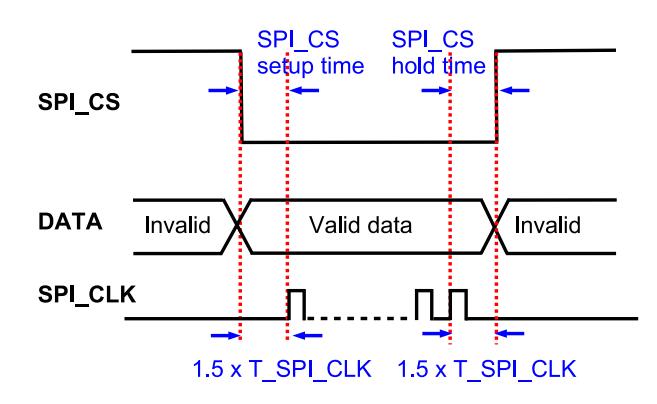

| 27.6 | CS Setup Time and Hold Time Control | 639 | ||

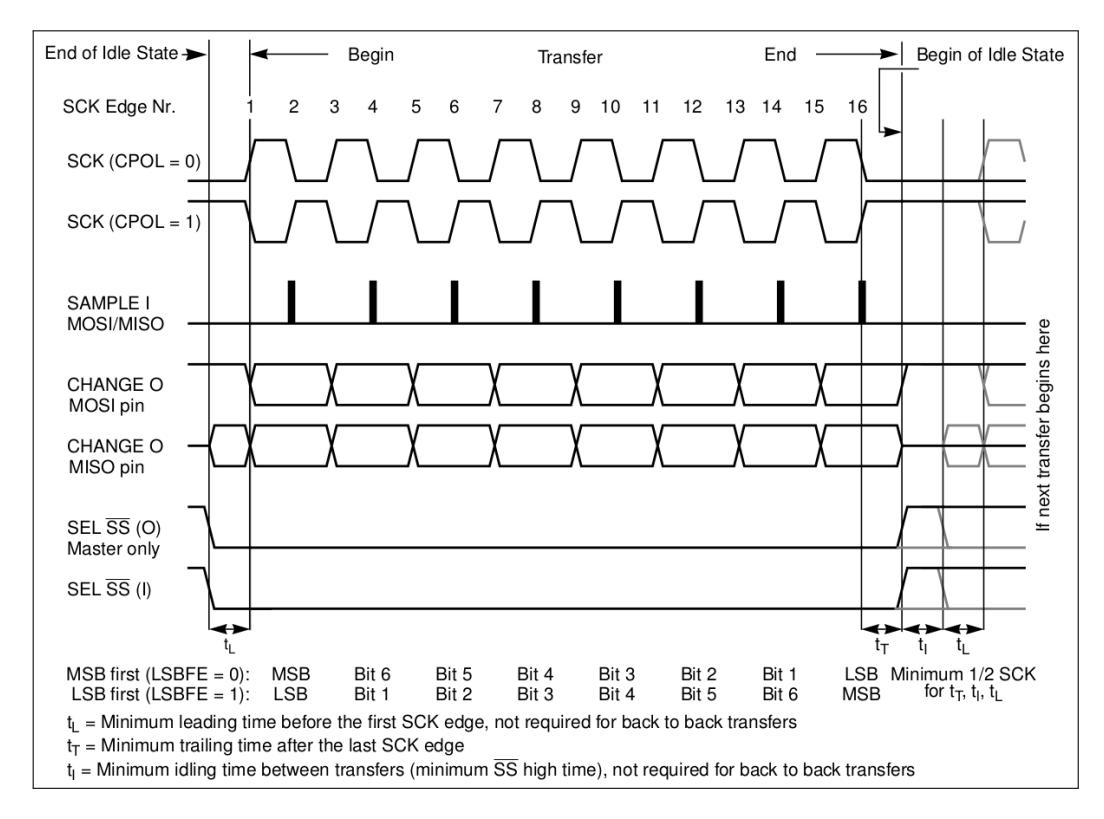

27.7 GP-SPI 2 Clock Control 640

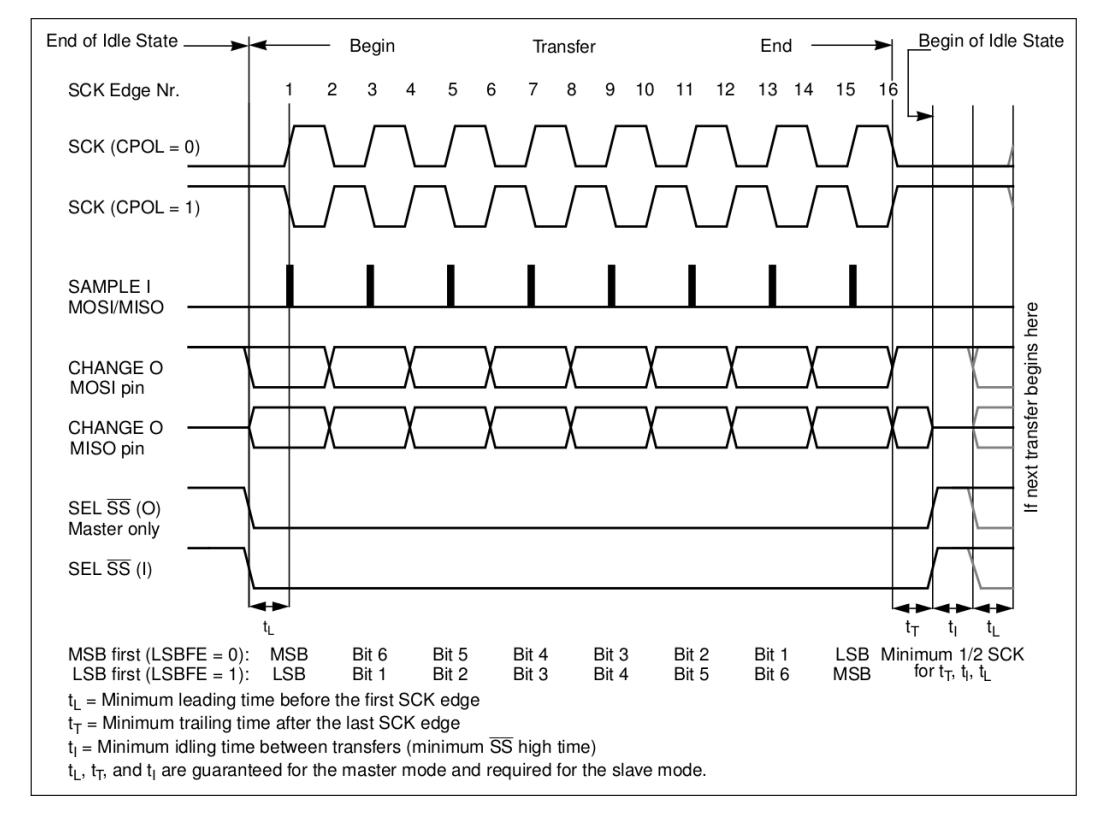

| 27.7.1 | Clock Phase and Polarity | 640 | |

|---|---|---|---|

| 27.7.2 | Clock Control in Master Mode | 642 | |

| 27.7.3 | Clock Control in Slave Mode | 642 | |

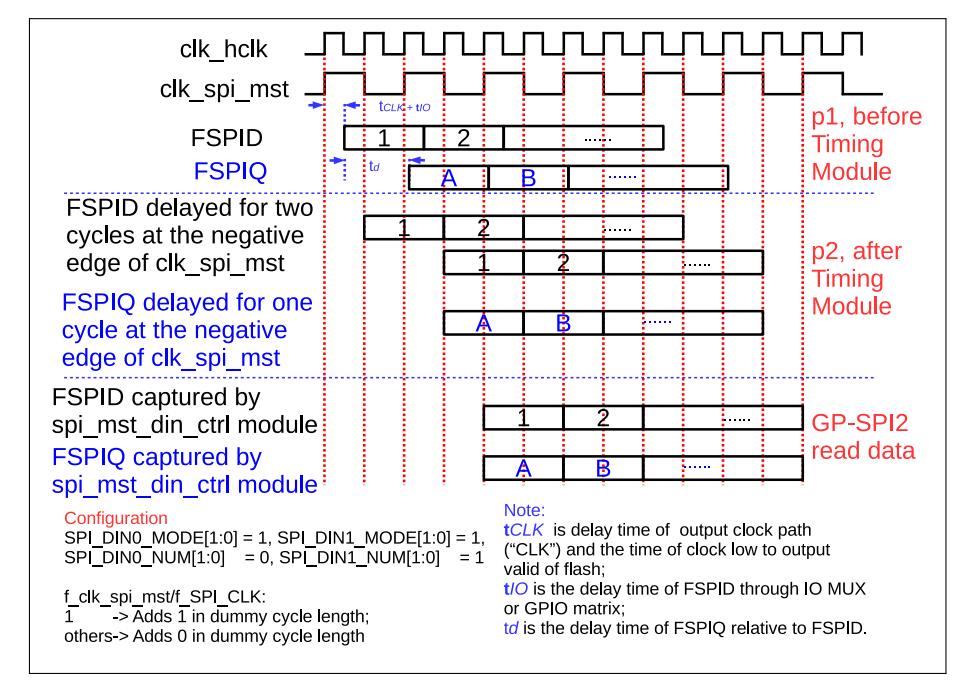

| 27.8 | GP-SPI2 Timing Compensation | 642 | |

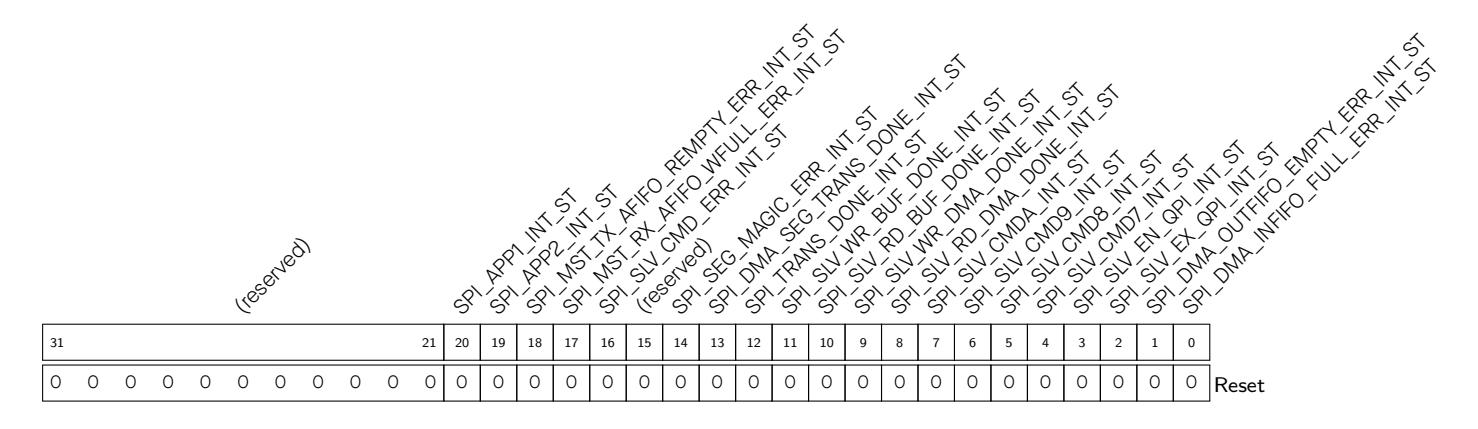

| 27.9 | Interrupts | ||

| 27.10 Register Summary | |||

| 27.11 | Registers | ||

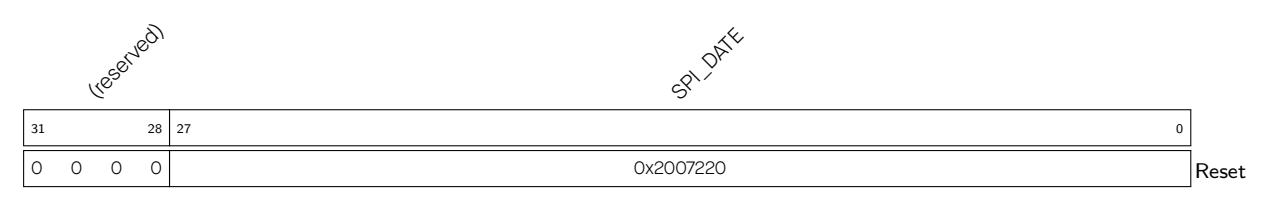

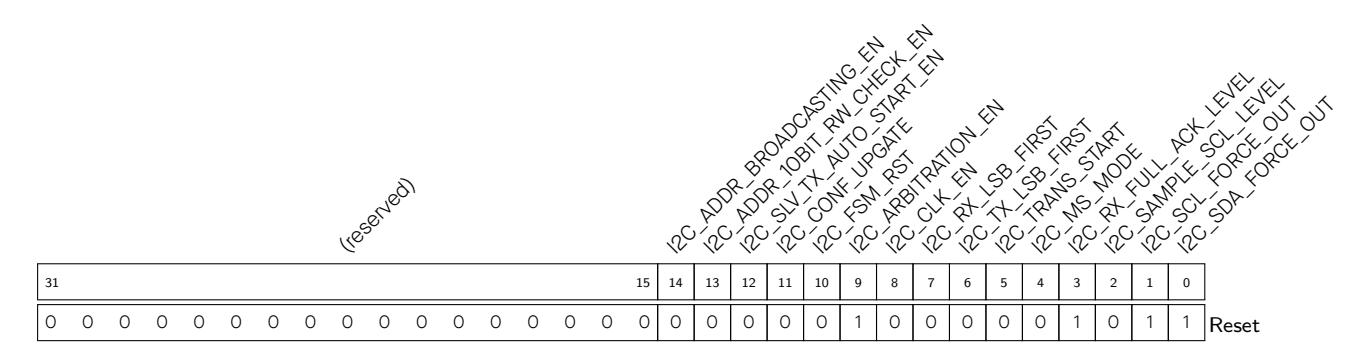

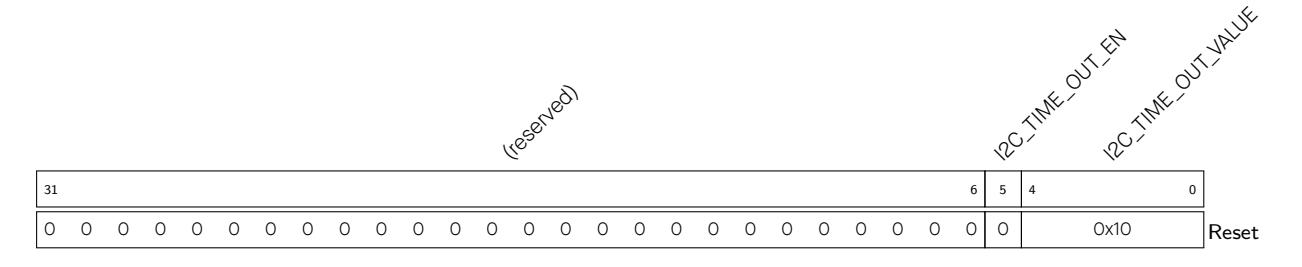

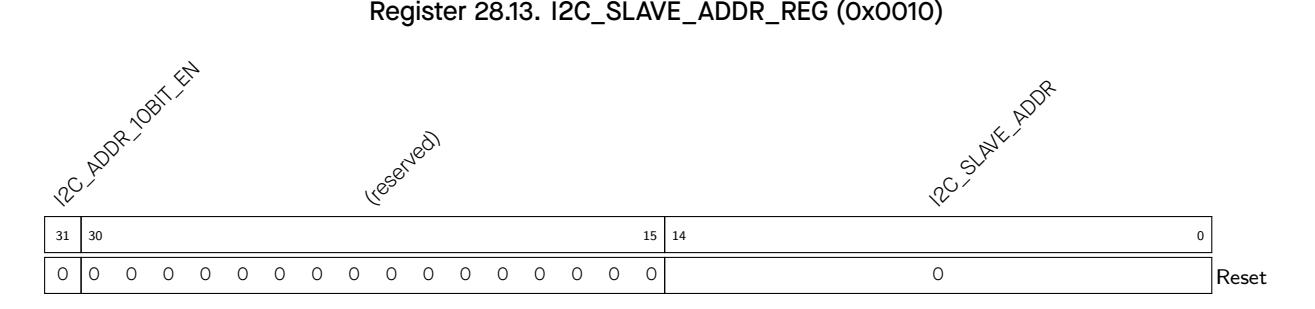

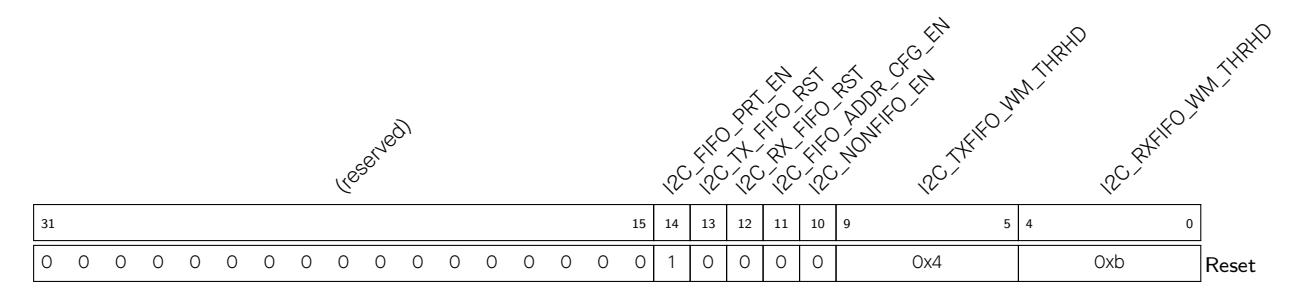

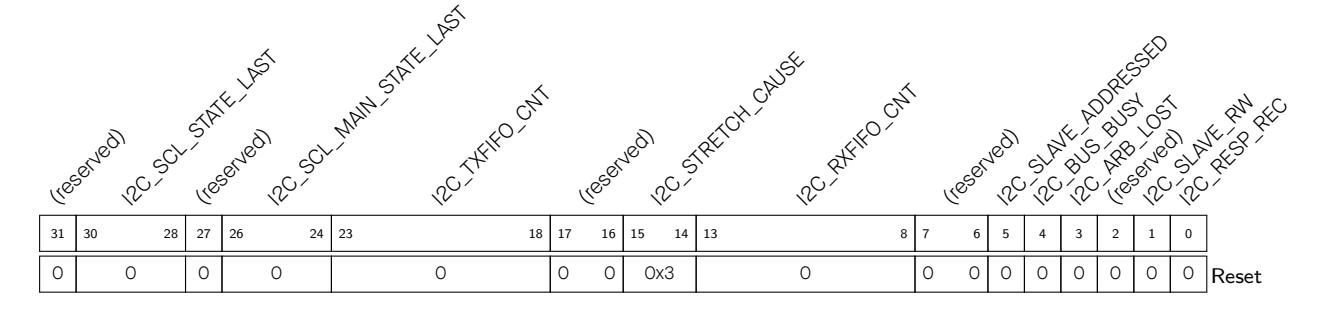

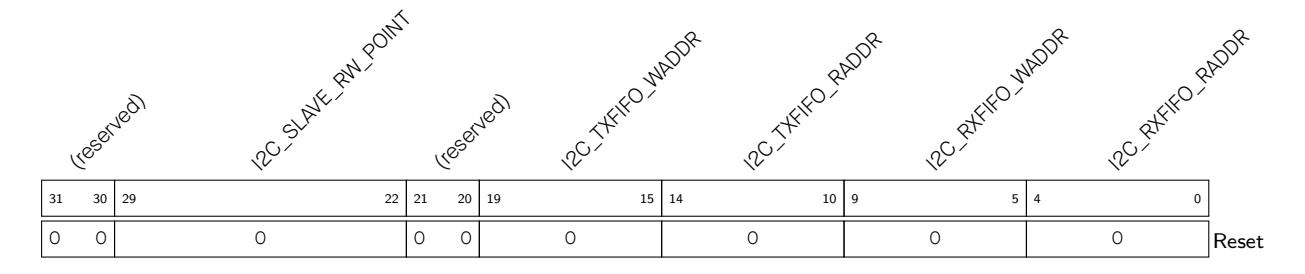

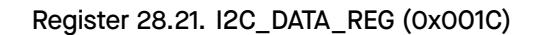

| 28.1 | Overview | ||

|---|---|---|---|

| 28.2 | Features | ||

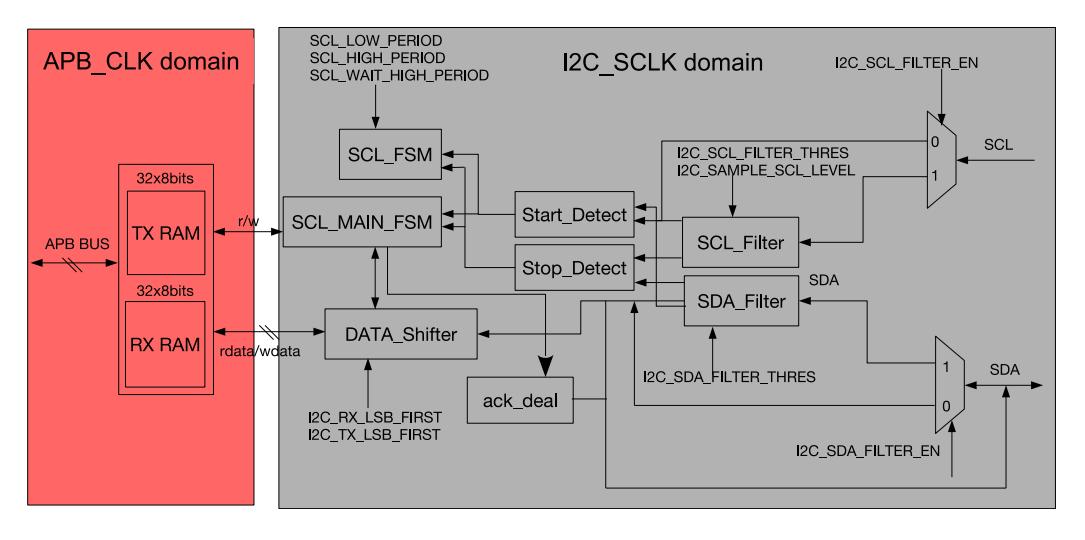

| 28.3 | I2C Architecture | ||

| 28.4 | Functional Description | ||

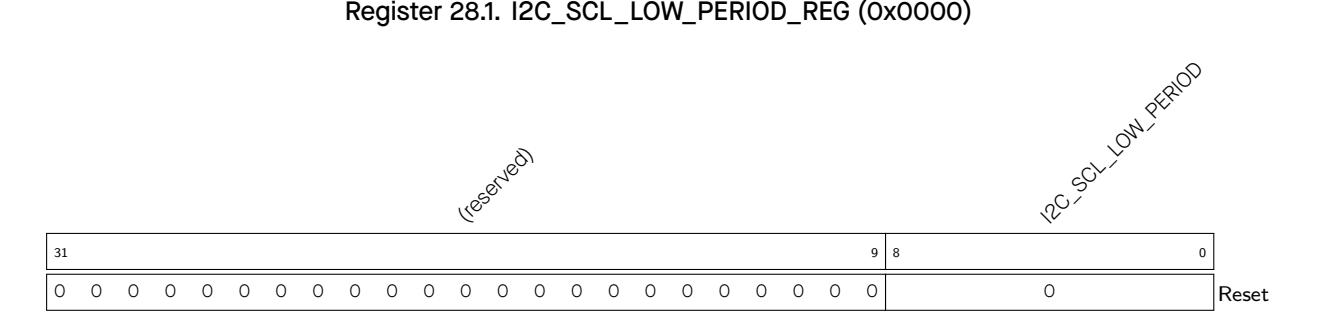

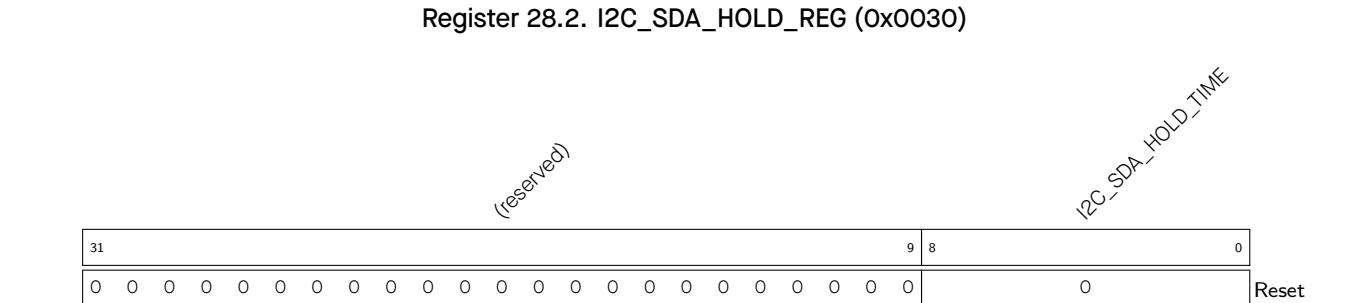

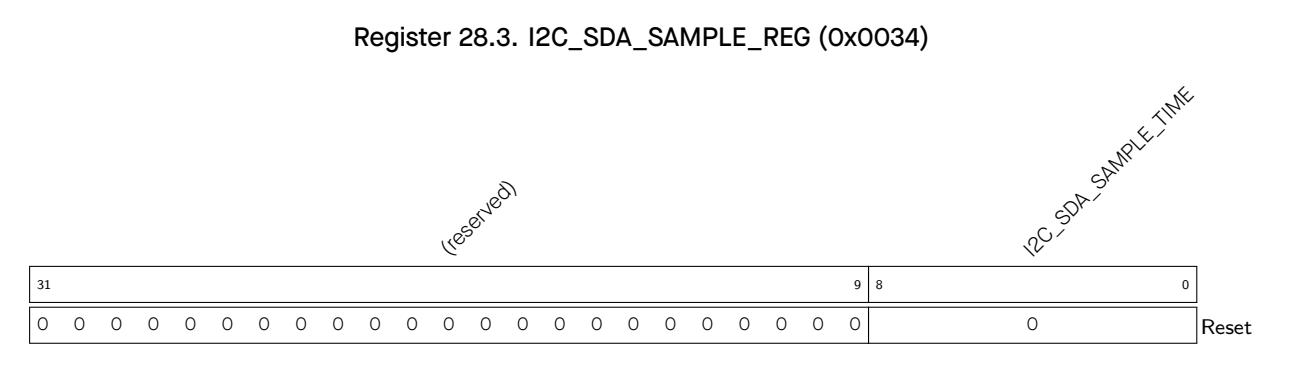

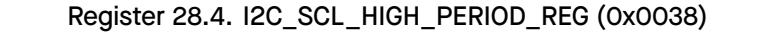

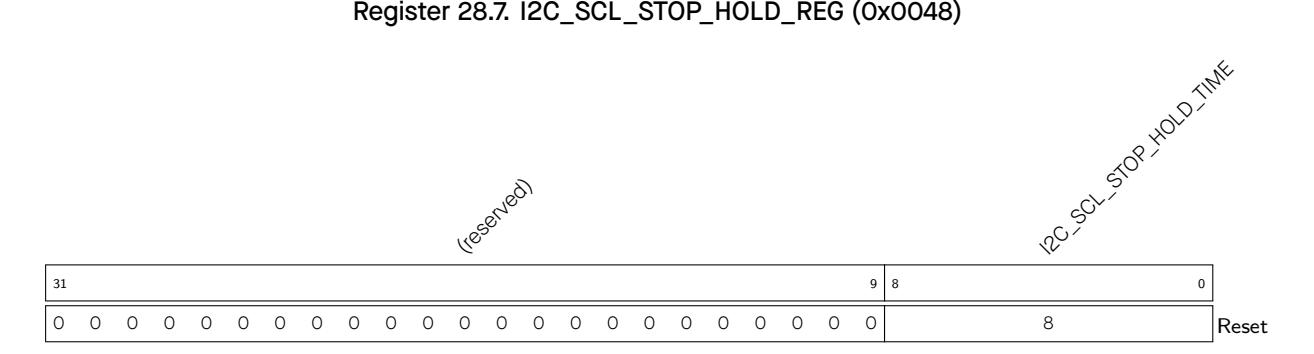

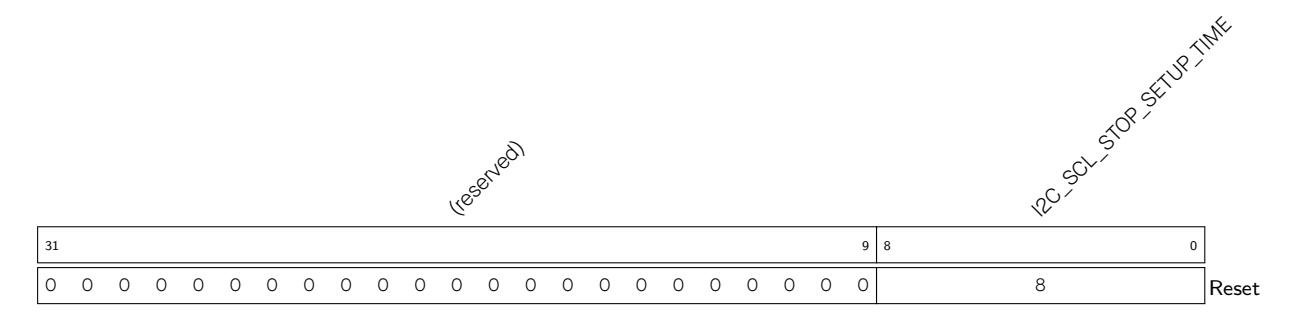

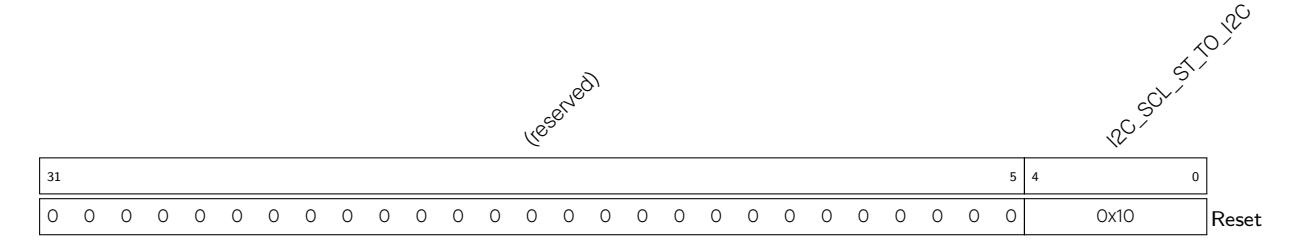

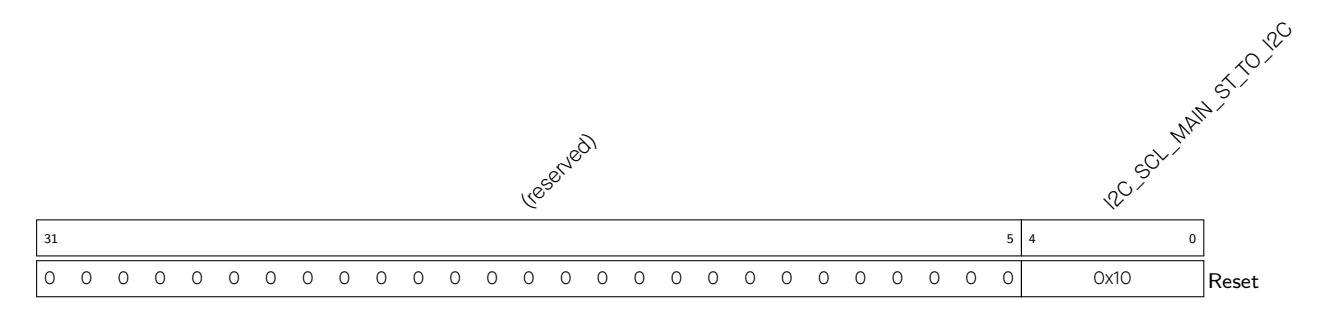

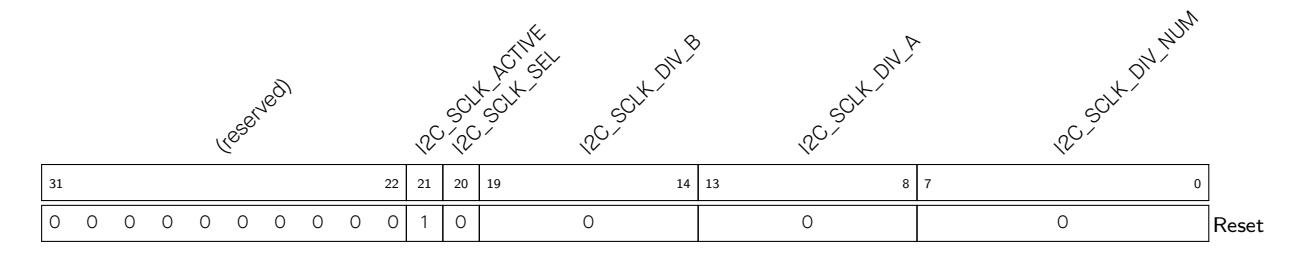

| 28.4.1 Clock Configuration | 679 | ||

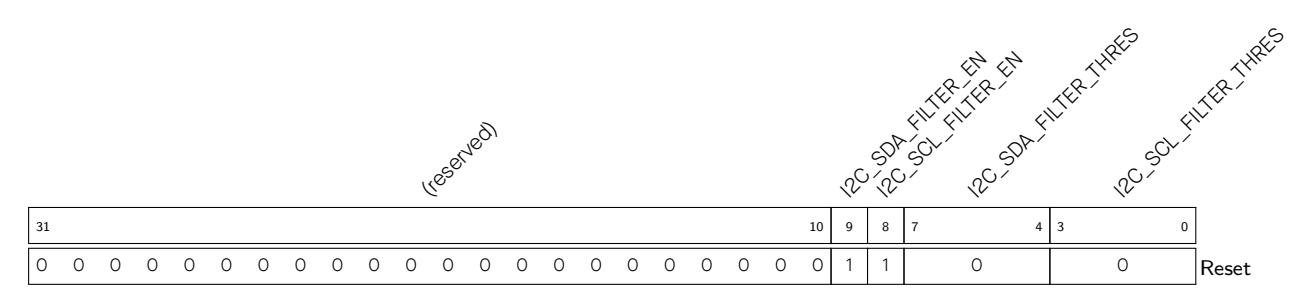

| 28.4.2 SCL and SDA Noise Filtering | 679 | ||

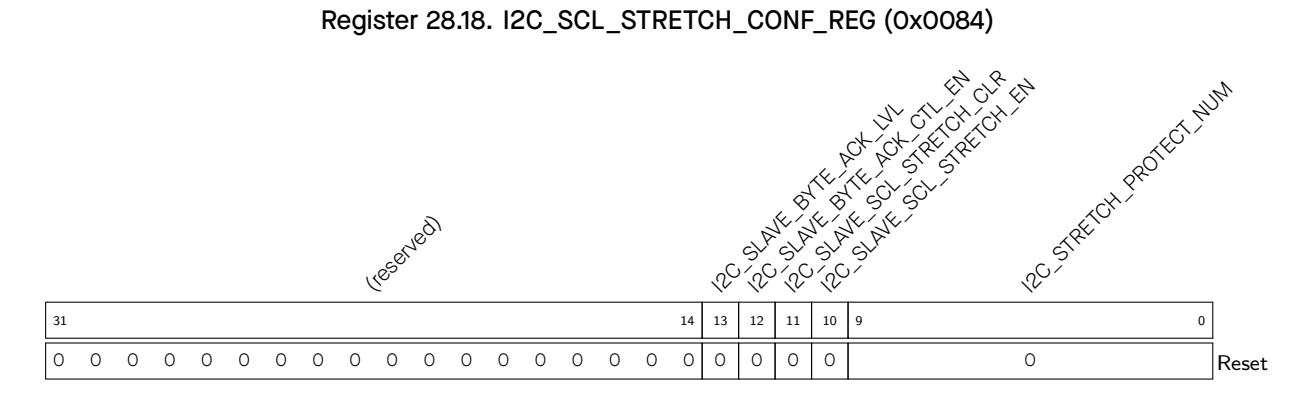

| 28.4.3 SCL Clock Stretching | |||

| 28.4.4 Generating SCL Pulses in Idle State | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 28.4.5 Synchronization | |||

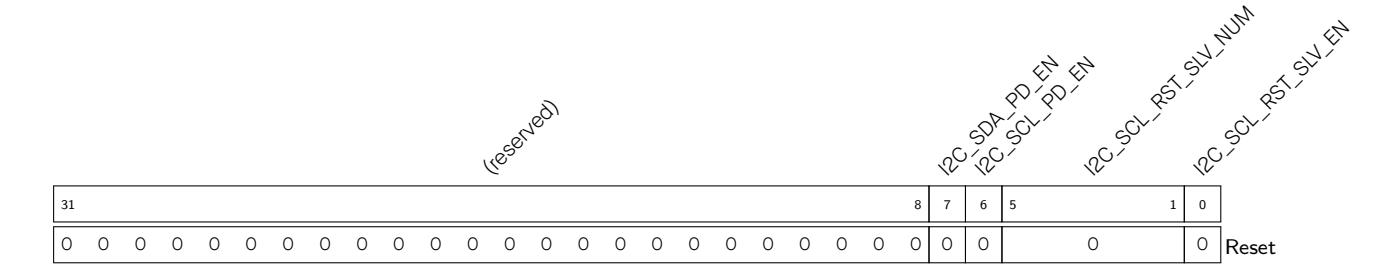

| 28.4.6 Open-Drain Output | |||

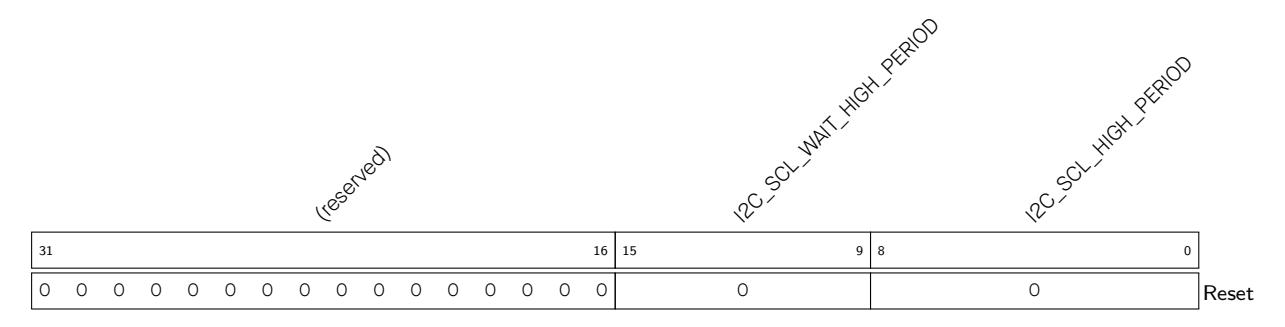

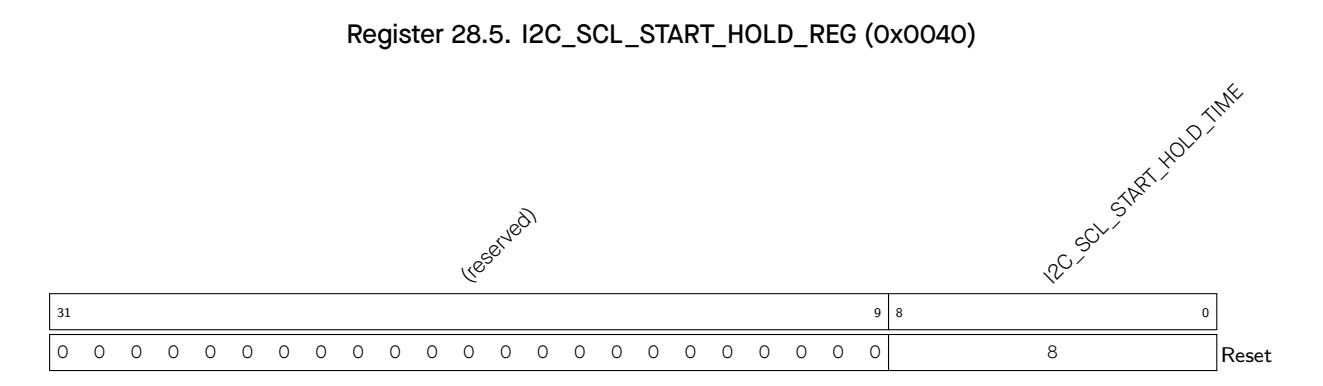

| 28.4.7 Timing Parameter Configuration | |||

| 28.4.8 Timeout Control | |||

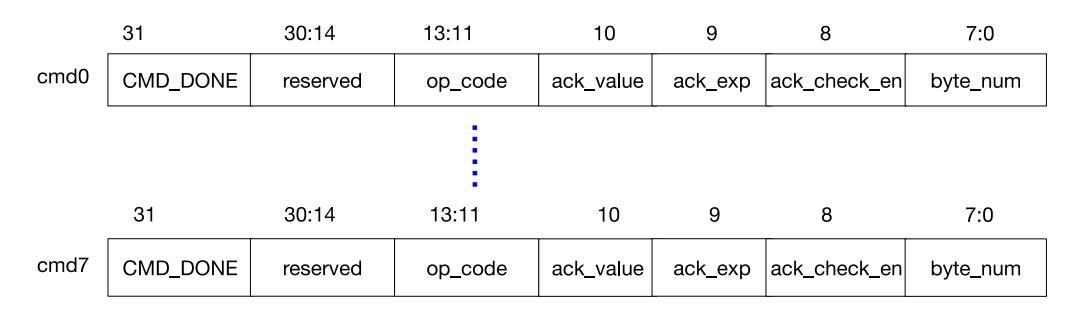

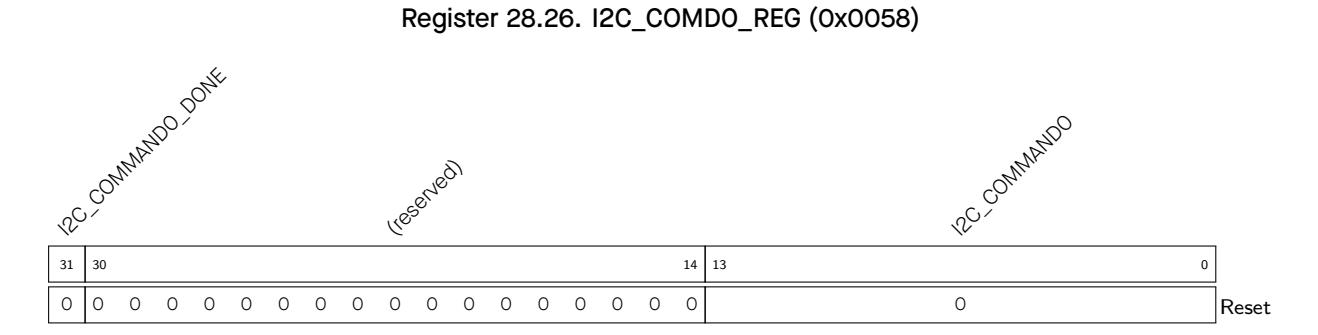

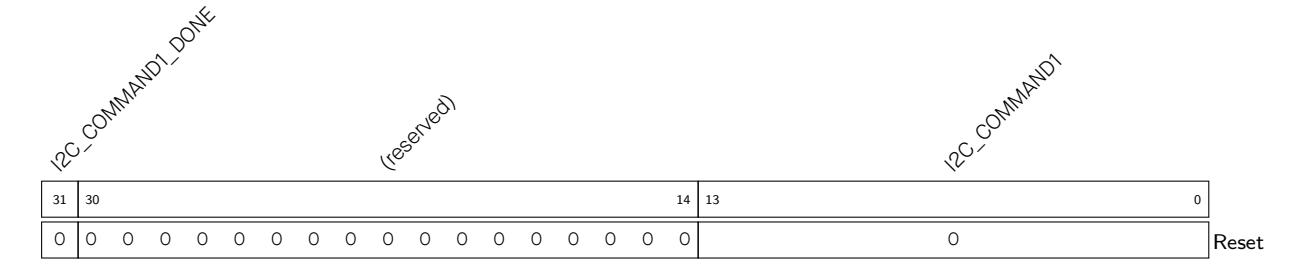

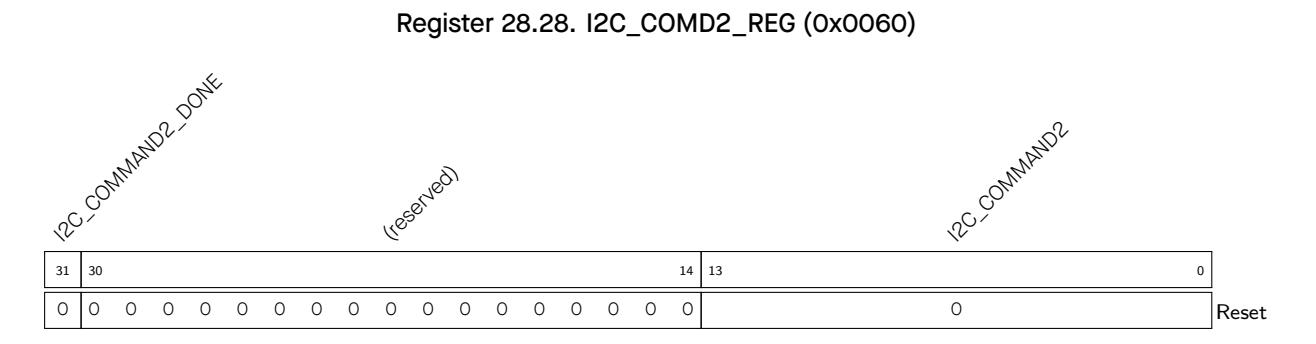

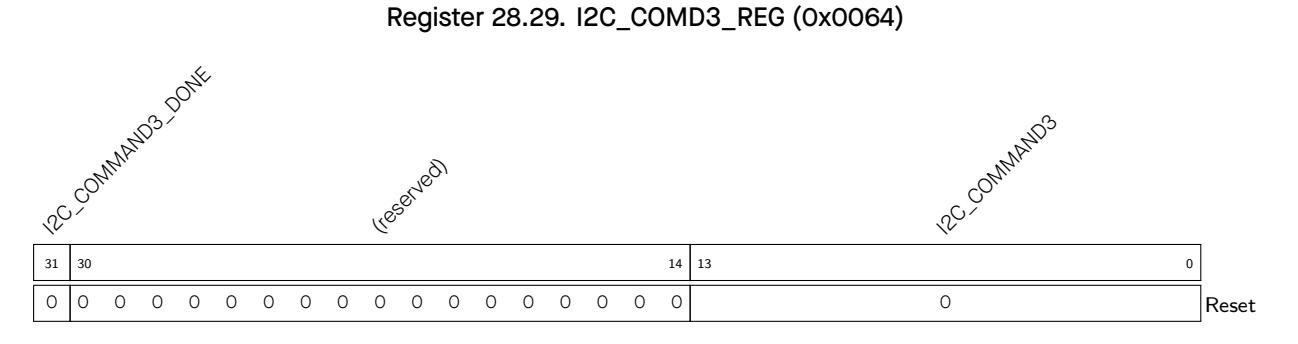

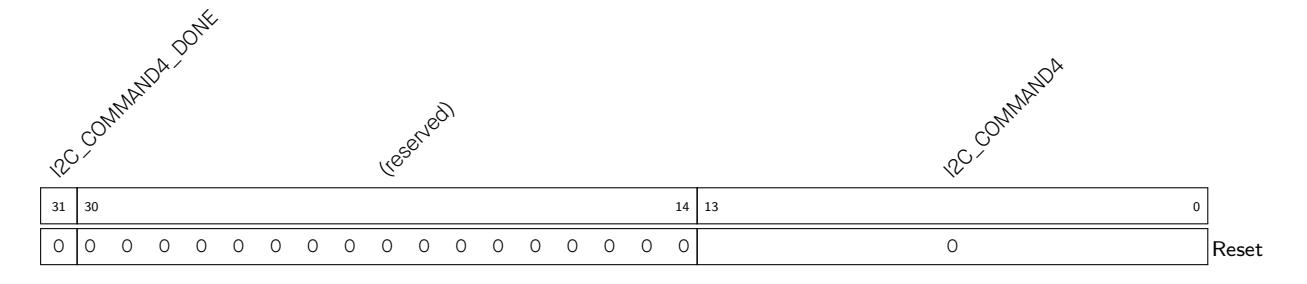

| 28.4.9 Command Configuration | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 28.4.10 TX/RX RAM Data Storage | 685 | ||

| 28.4.11 Data Conversion | 686 | ||

| 28.4.12 Addressing Mode | |||

| 28.4.13 Bit Check in 10-bit Addressing Mode | |||

| 28.4.14 To Start the I2C Controller | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

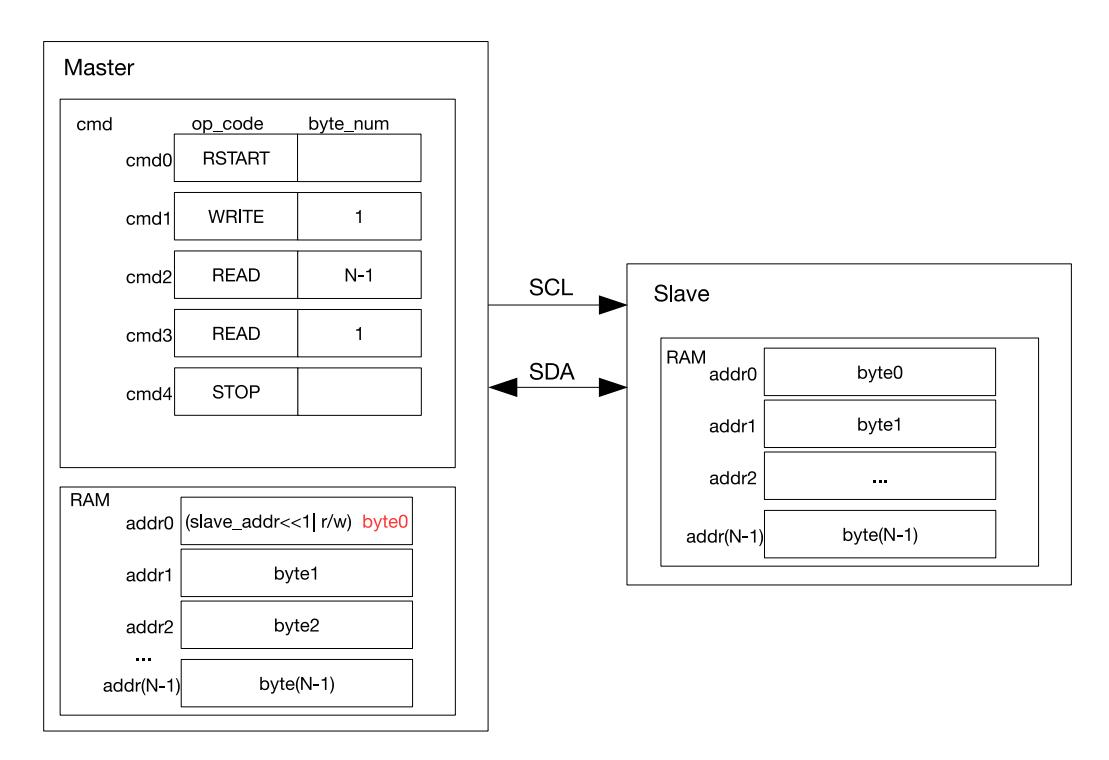

| 28.5 | Programming Example | 687 | |

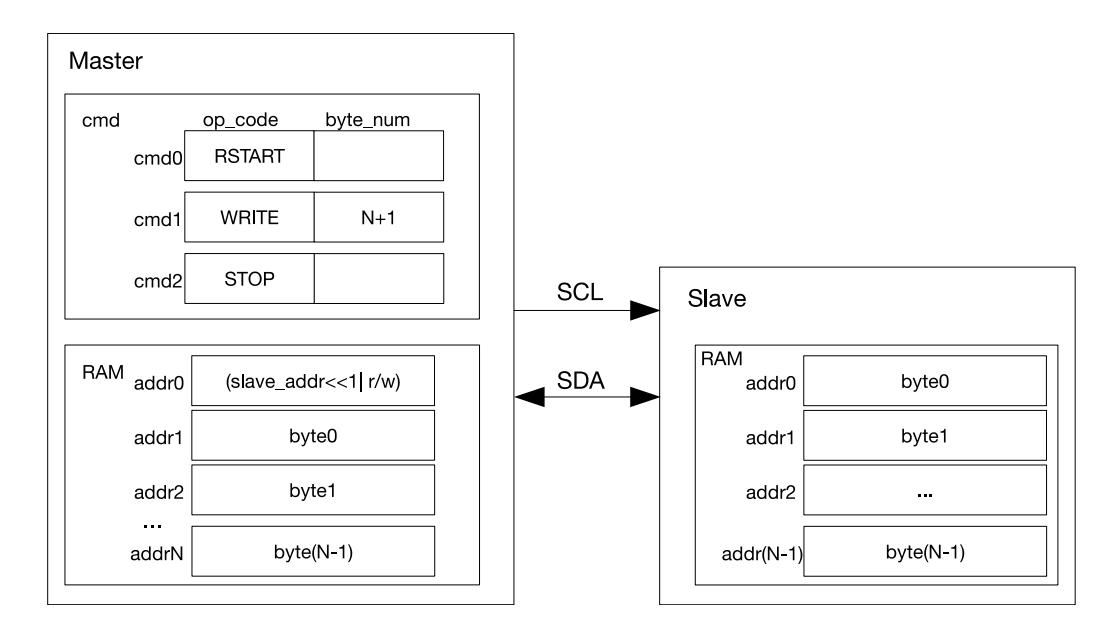

| 28.5.1 I2C master Writes to I2C slave with a 7-bit Address in One Command Sequence | 687 | ||

|

Introduction

28.5.1.1 |

688 | ||

| 28.5.1.2 Configuration Example | 688 | ||

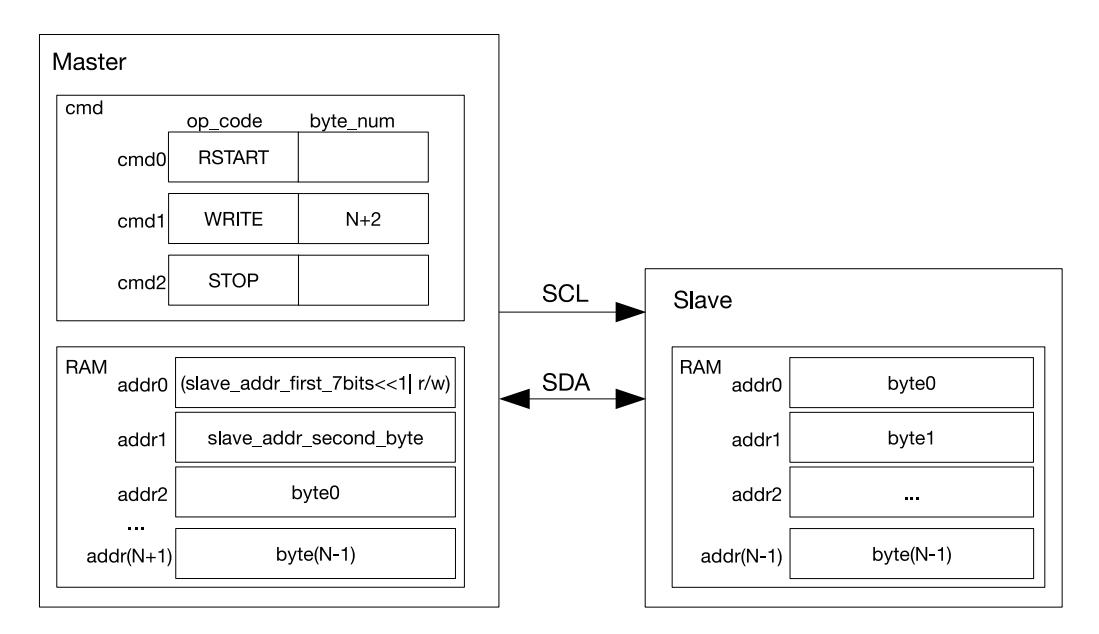

| 28.5.2 I2C master Writes to I2C slave with a 10-bit Address in One Command Sequence | 689 | ||

|

Introduction

28.5.2.1 |

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 28.5.2.2 Configuration Example | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

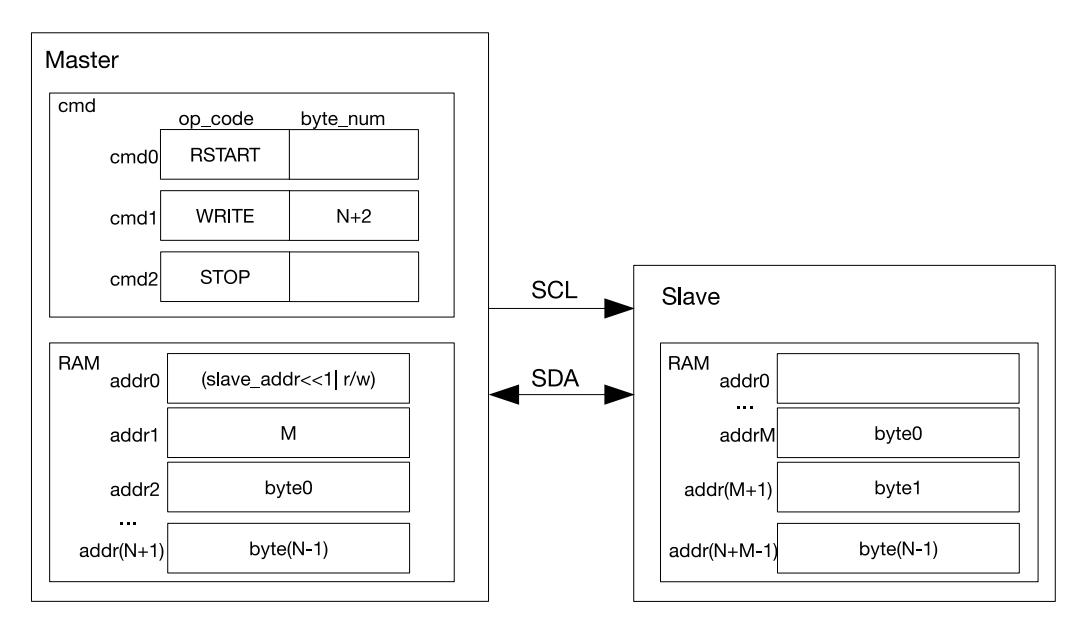

| 28.5.3 I2C master Writes to I2C slave with Two 7-bit Addresses in One Command Sequence | 692 | ||

|

Introduction

28.5.3.1 |

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 28.5.3.2 Configuration Example | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

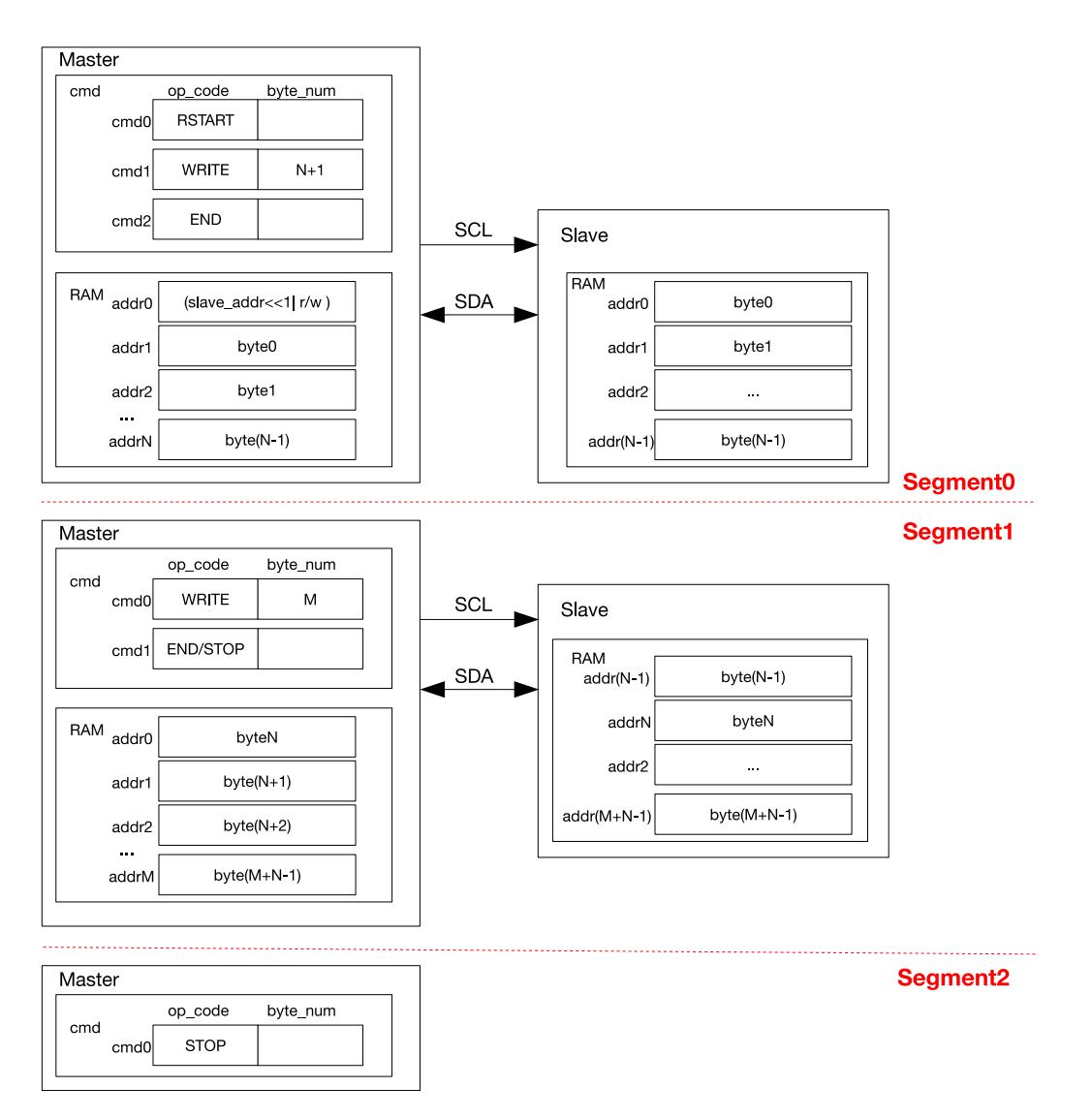

| 28.5.4 I2C master Writes to I2C slave with a 7-bit Address in Multiple Command Sequences | 694 | ||

|

Introduction

28.5.4.1 |

694 | ||

| 28.5.4.2 Configuration Example | 695 | ||

| 28.5.5 Reads with a 7-bit Address in One Command Sequence | 696 | ||

|

Introduction

28.5.5.1 |

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

| 28.5.5.2 Configuration Example | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | ||

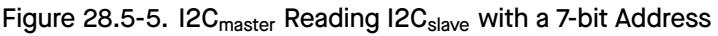

| 28.5.6 I2C master Reads I2C slave with a 10-bit Address in One Command Sequence | 698 | ||

|

28.5.6.1

Introduction |

698 | ||

| 28.5.6.2 Configuration Example | 699 | ||

| Contents | GoBack | |

|

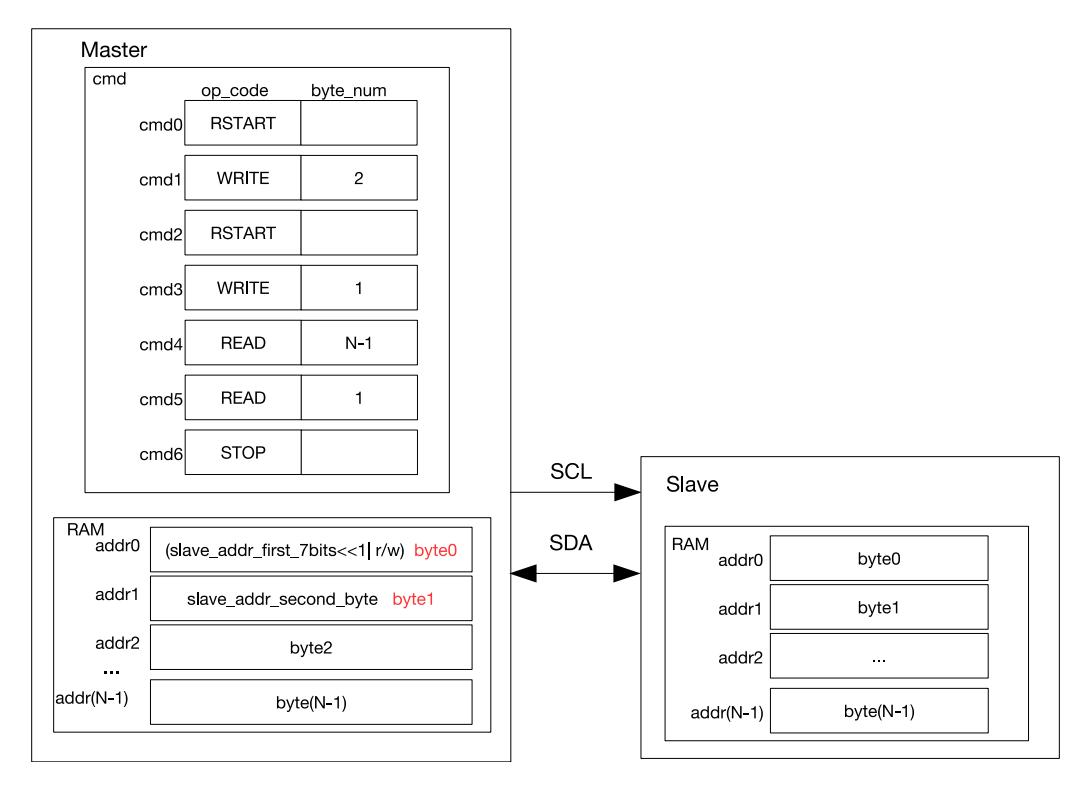

28.5.7

I2Cmaster Reads I2Cslave with Two 7-bit Addresses in One Command Sequence |

700 | |

|

28.5.7.1

Introduction |

701 | |

|

28.5.7.2

Configuration Example |

701 | |

|

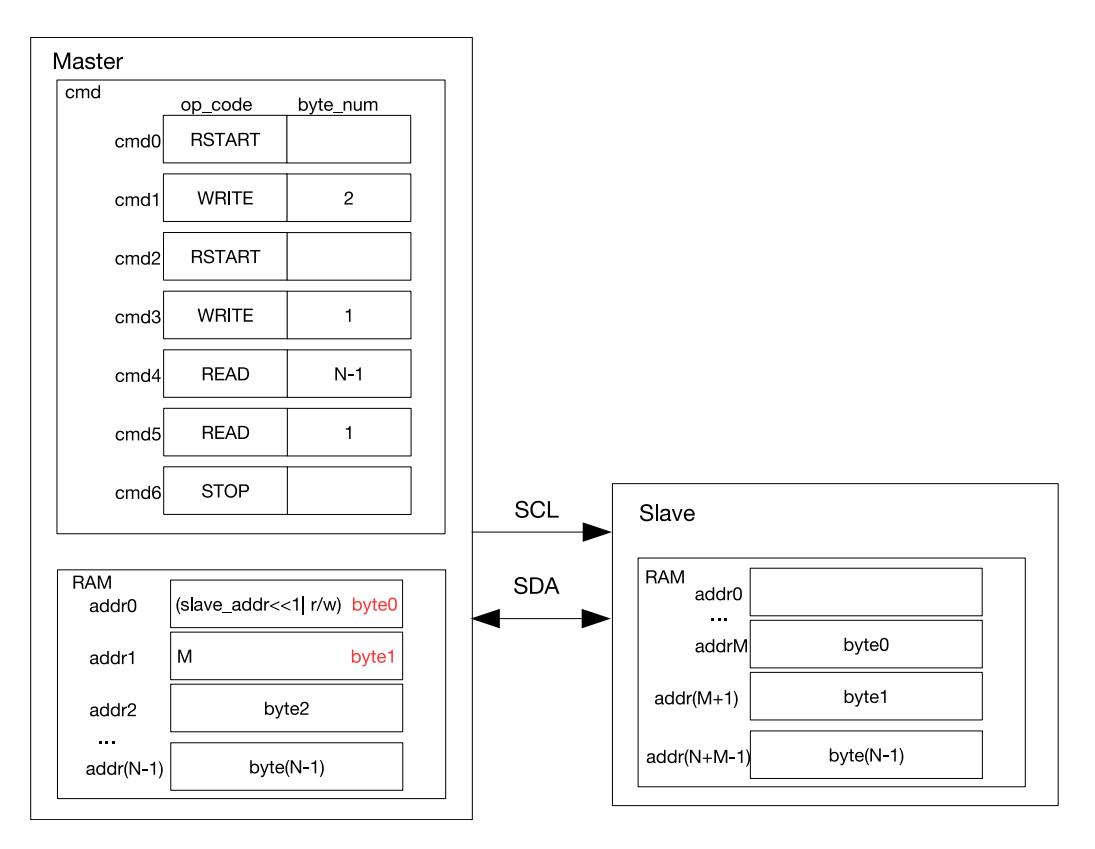

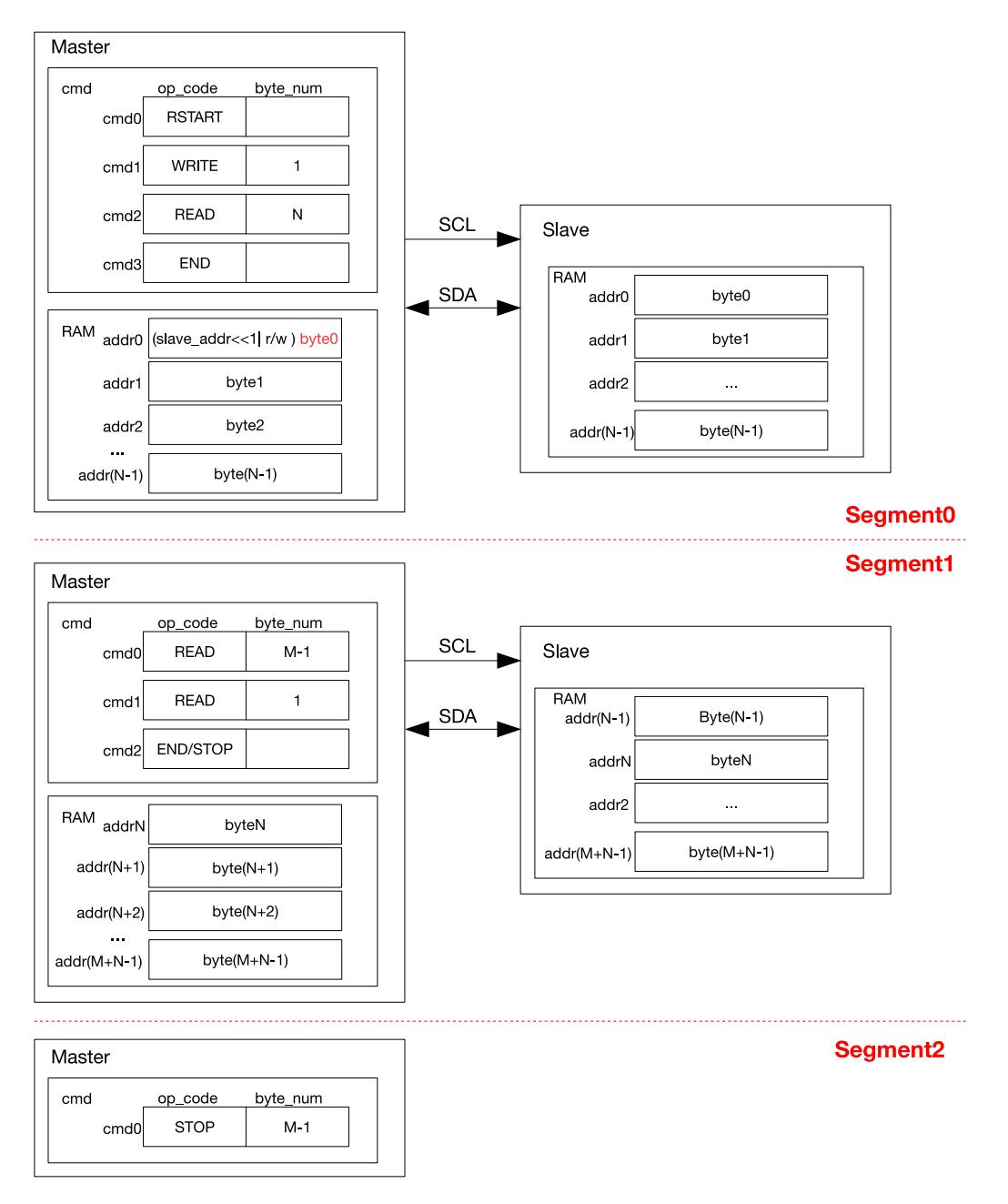

28.5.8

I2Cmaster Reads I2Cslave with a 7-bit Address in Multiple Command Sequences |

704 | |

|

28.5.8.1

Introduction |

704 | |

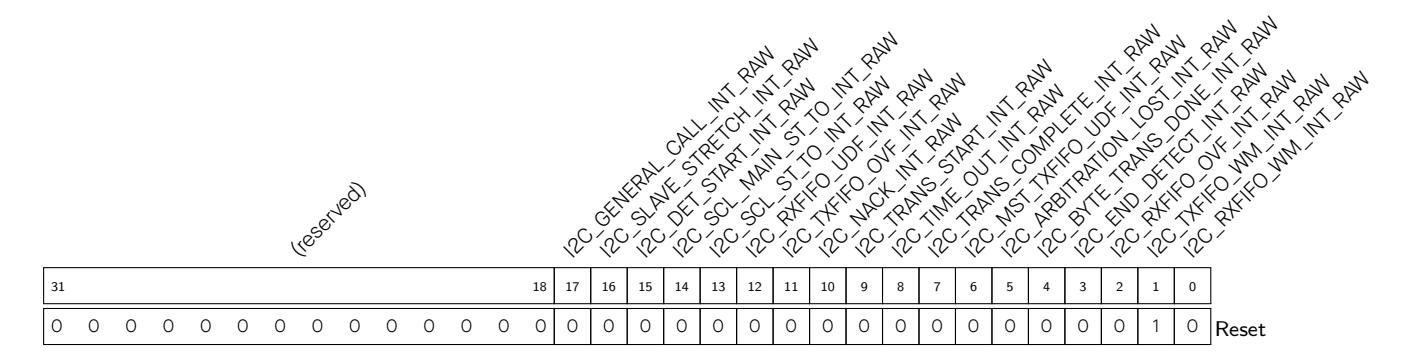

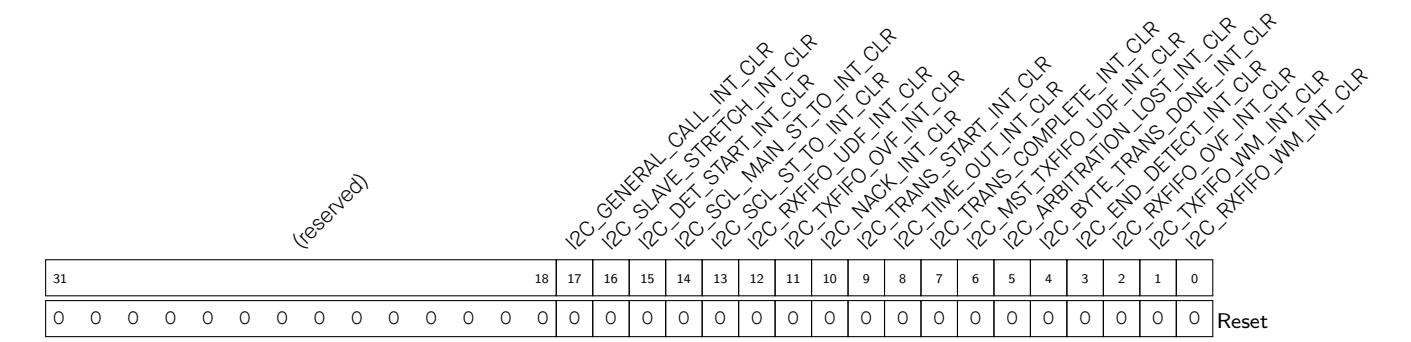

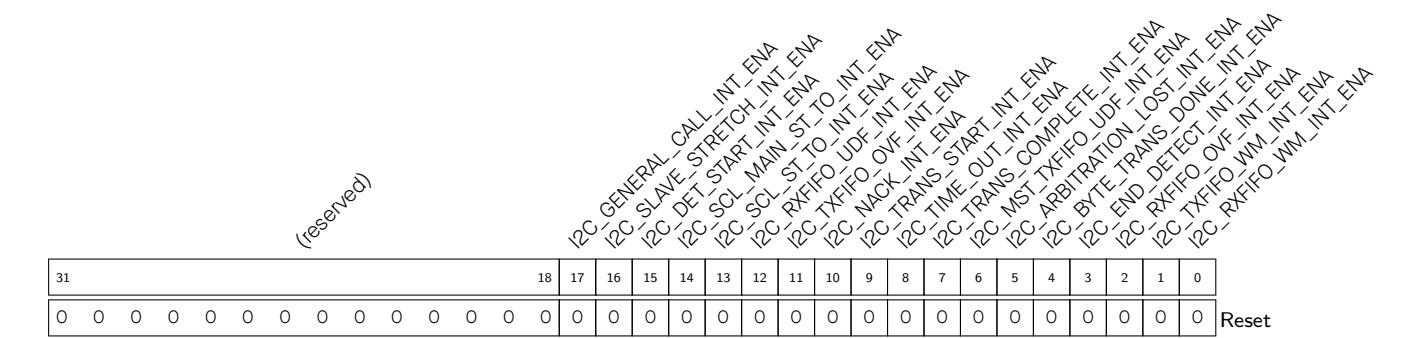

| 28.6 |

28.5.8.2

Configuration Example Interrupts |

705

707 |

| 28.7 | Register Summary | 708 |

| 28.8 | Registers | 710 |

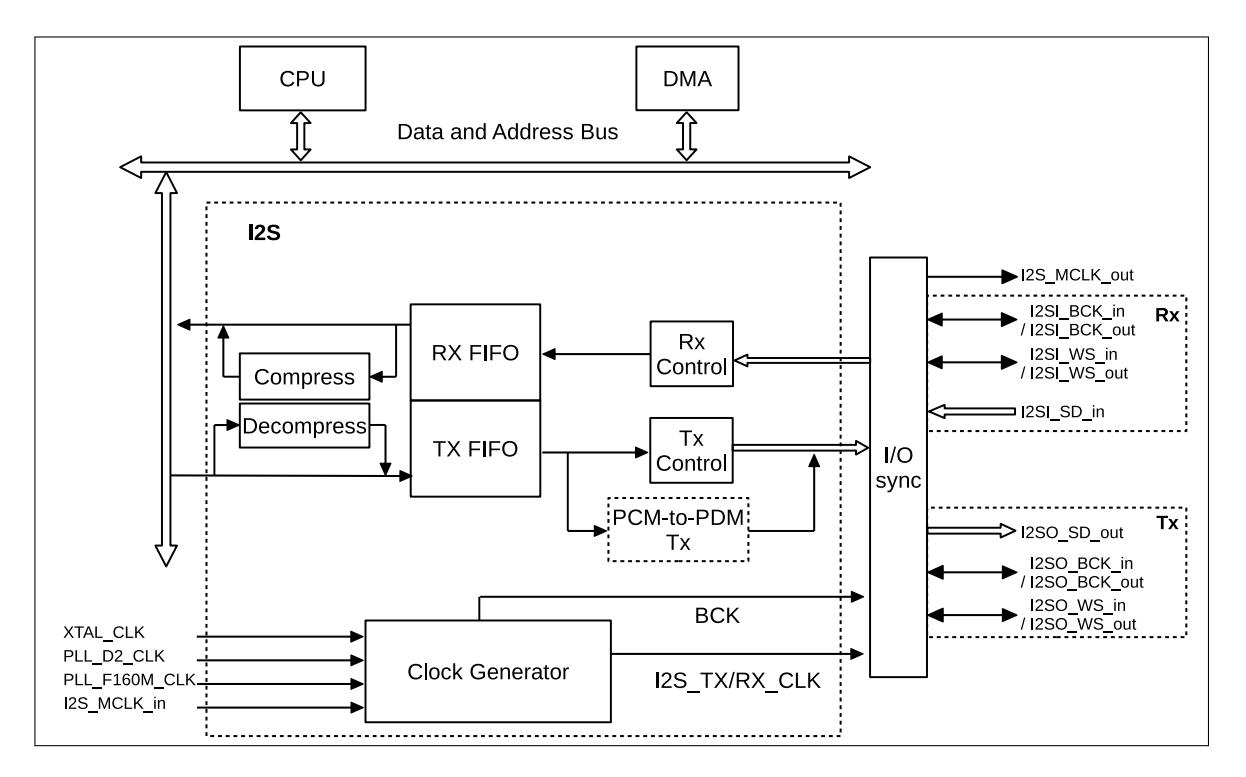

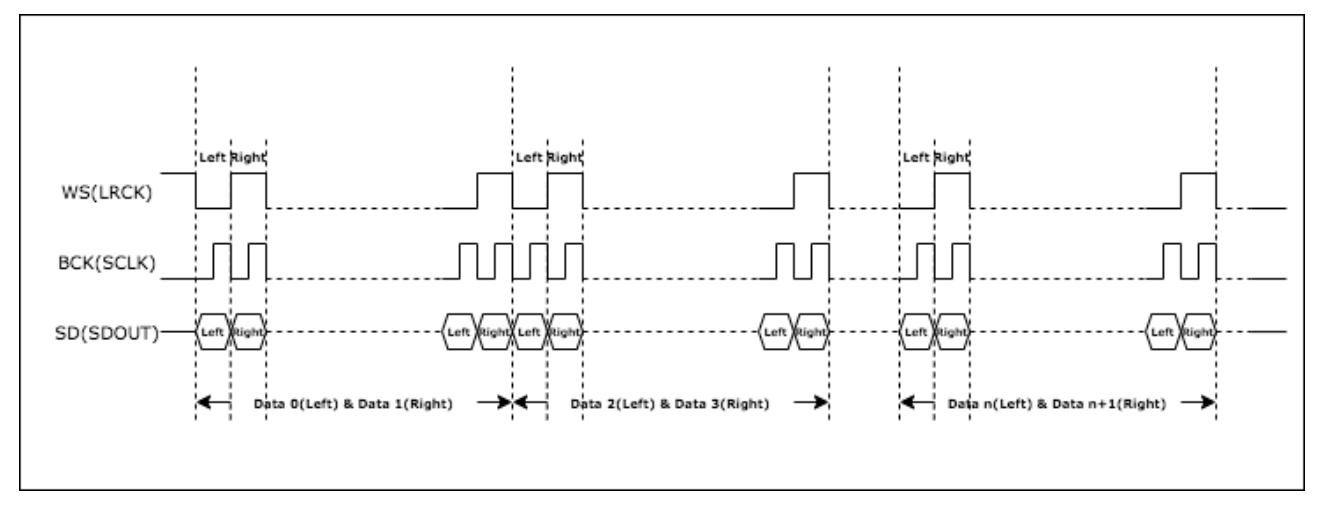

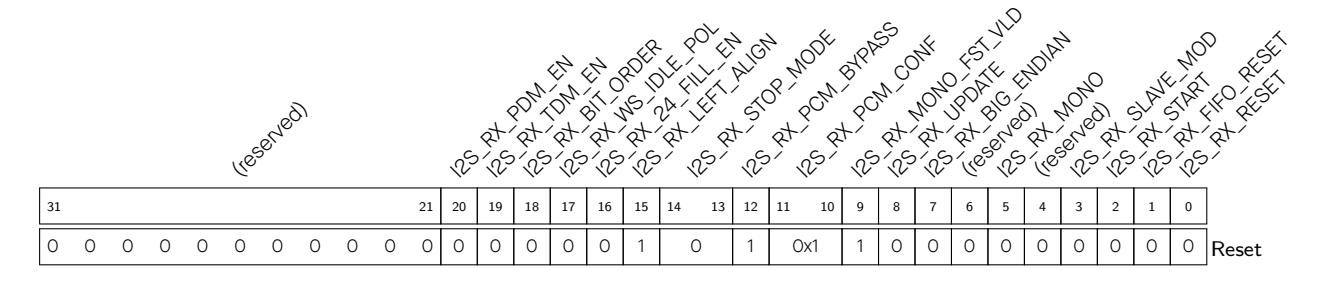

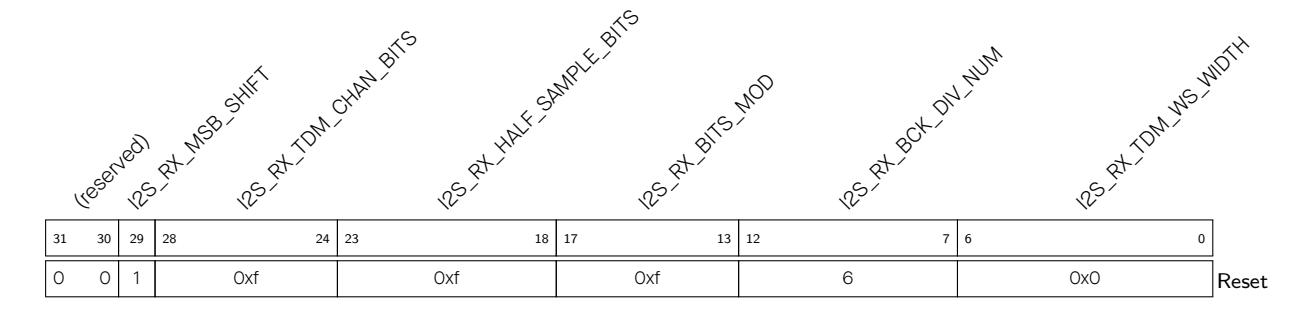

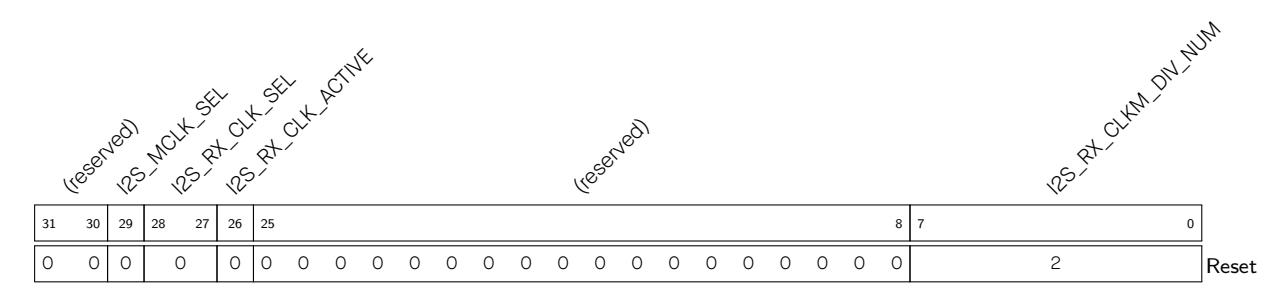

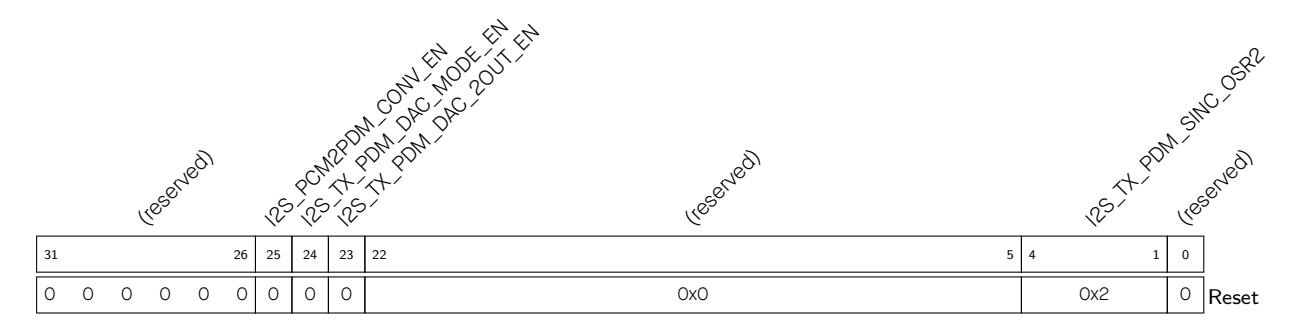

| 29 | I2S Controller (I2S) | |

| 730 | ||

|

29.1

29.2 |

Overview

Terminology |

730

730 |

| 29.3 | Features | 731 |

| 29.4 | System Architecture | 732 |

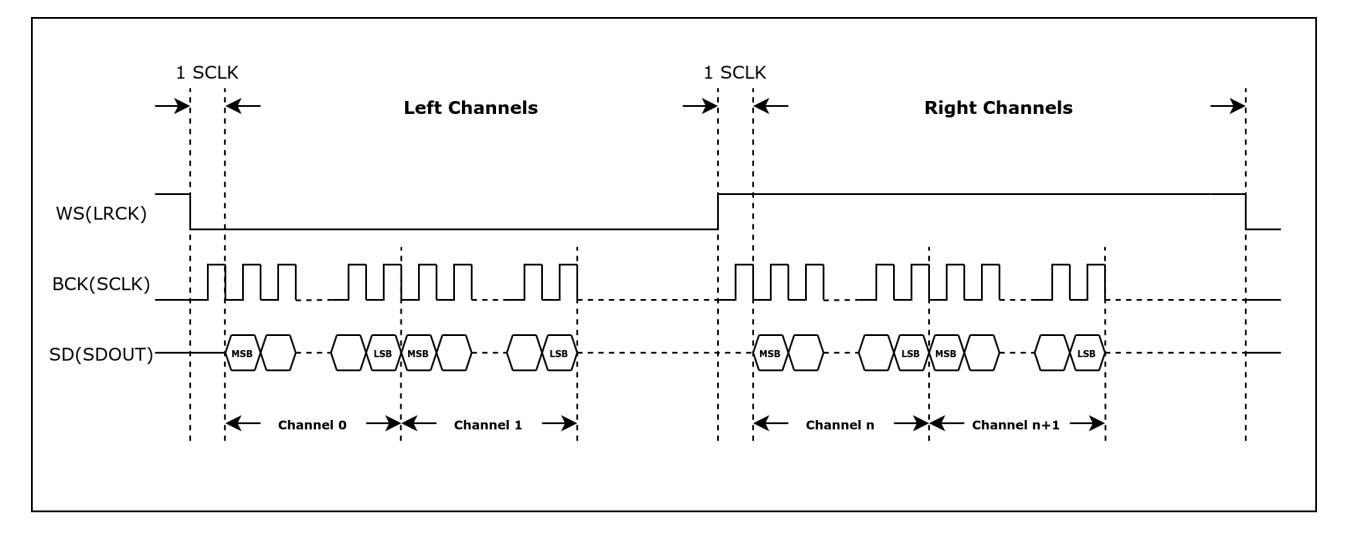

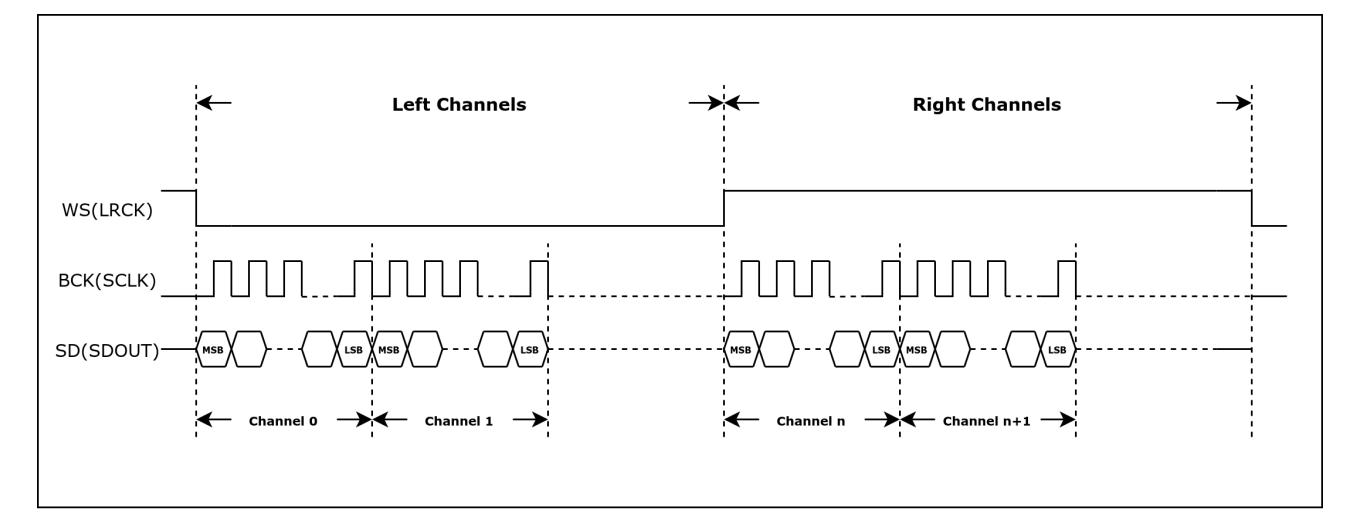

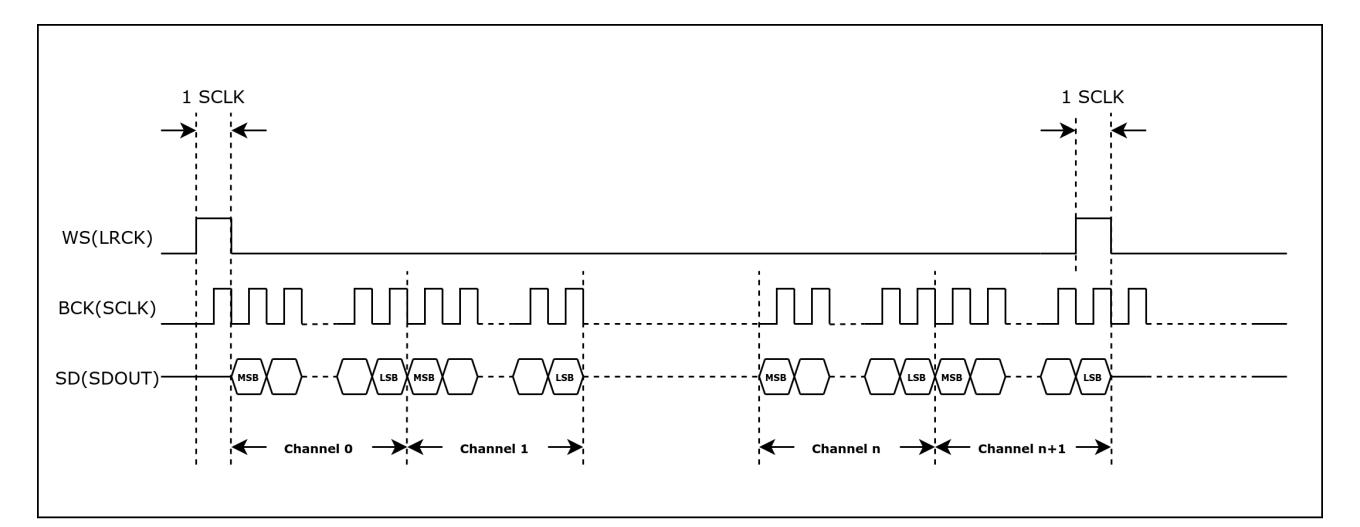

| 29.5 | Supported Audio Standards | 733 |

|

29.5.1

TDM Philips Standard |

734 | |

|

29.5.2

TDM MSB Alignment Standard |

734 | |

|

29.5.3

TDM PCM Standard |

735 | |

|

29.5.4

PDM Standard |

735 | |

| 29.6 | I2S TX/RX Clock | 736 |

| 29.7 | I2S Reset | 738 |

| 29.8 | I2S Master/Slave Mode | 738 |

|

29.8.1

Master/Slave TX Mode |

738 | |

|

29.8.2

Master/Slave RX Mode |

739 | |

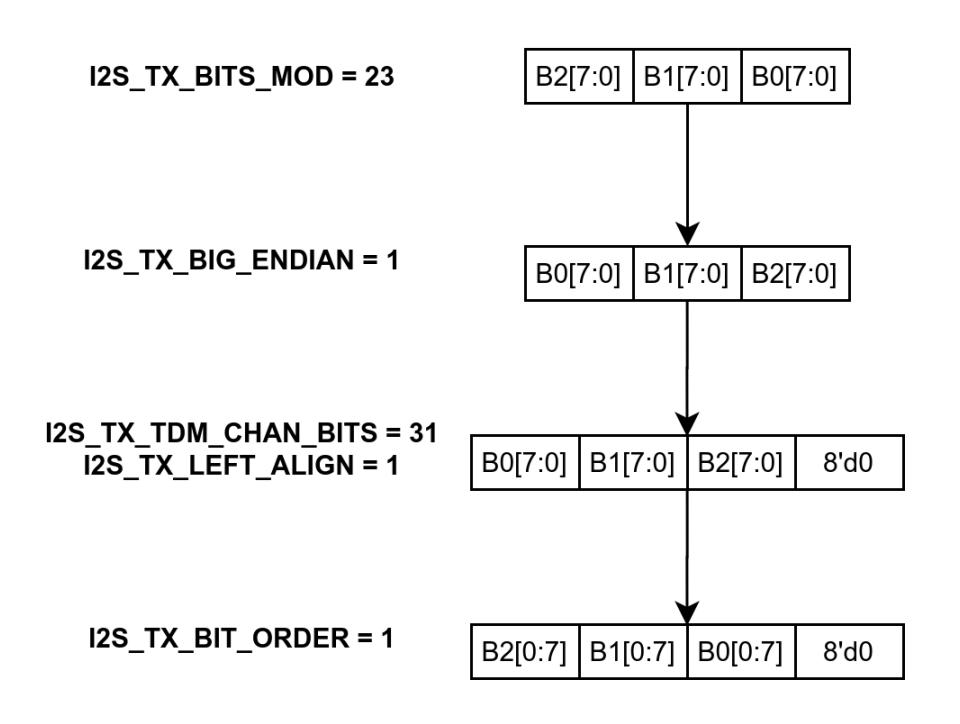

| 29.9 |

Transmitting Data

29.9.1 Data Format Control |

739

739 |

|

29.9.1.1

Bit Width Control of Channel Valid Data |

739 | |

|

29.9.1.2

Endian Control of Channel Valid Data |

740 | |

|

29.9.1.3

A-law/µ-law Compression and Decompression |

740 | |

|

29.9.1.4

Bit Width Control of Channel TX Data |

741 | |

|

29.9.1.5

Bit Order Control of Channel Data |

741 | |

|

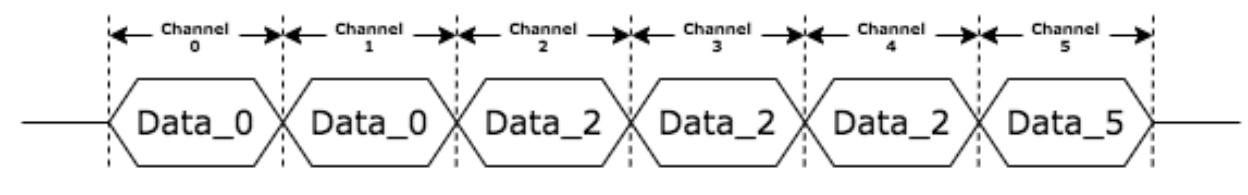

29.9.2

Channel Mode Control |

742 | |

|

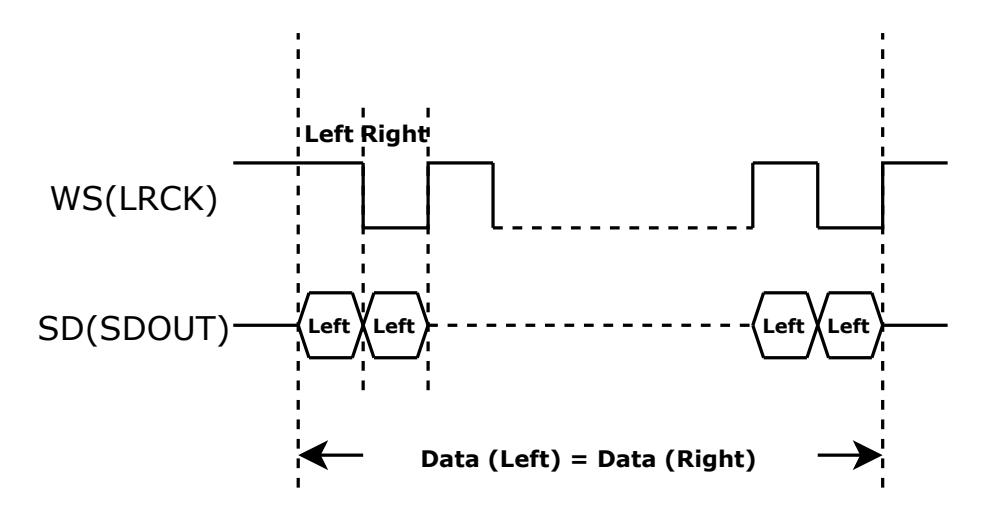

29.9.2.1

I2S Channel Control in TDM TX Mode |

742 | |

|

29.9.2.2

I2S Channel Control in PDM TX Mode |

743 | |

| 29.10 | Receiving Data | 745 |

|

29.10.1

Channel Mode Control |

745 | |

|

29.10.1.1

I2S Channel Control in TDM RX Mode |

746 | |

|

29.10.1.2

I2S Channel Control in PDM RX Mode |

746 | |

| 29.10.2 Data Format Control | 746 | |

|

29.10.2.1

Bit Order Control of Channel Data 29.10.2.2 Bit Width Control of Channel Storage (Valid) Data |

746

747 |

|

| 29.10.2.3 Bit Width Control of Channel RX Data | 747 | |

| 29.10.2.4 Endian Control of Channel Storage Data | 747 | |

| 29.10.2.5 A-law/µ-law Compression and Decompression | 748 | |

| Contents | GoBack | ||

|

29.11.1

Configure I2S as TX Mode |

|||

|

29.11.2

Configure I2S as RX Mode |

|||

|

29.12

29.13 |

I2S Interrupts

Register Summary |

749

749 |

|

| 29.14 | Registers | 751 | |

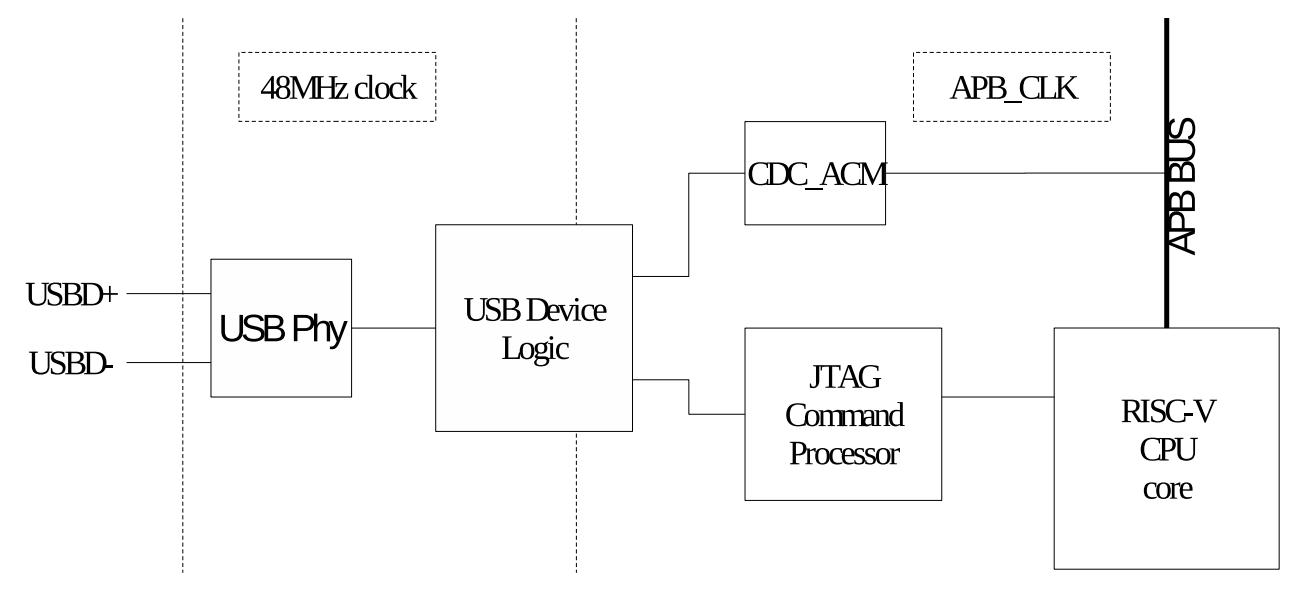

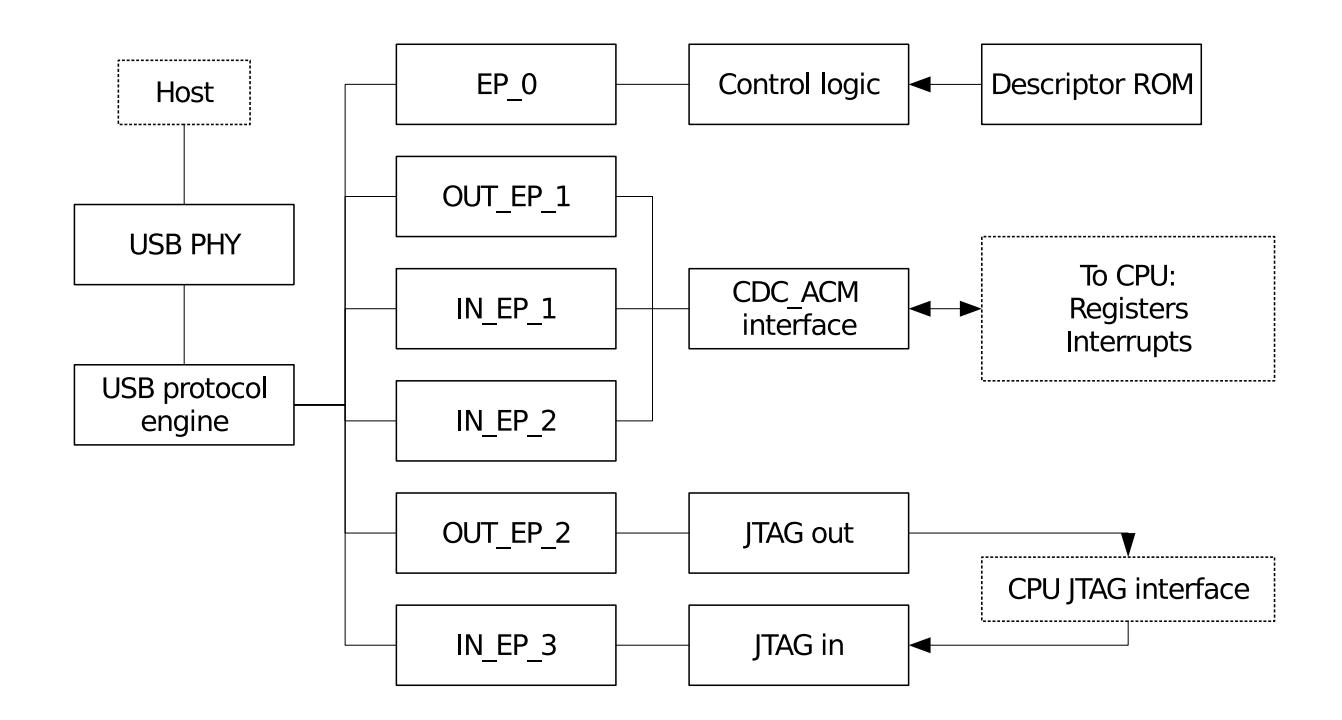

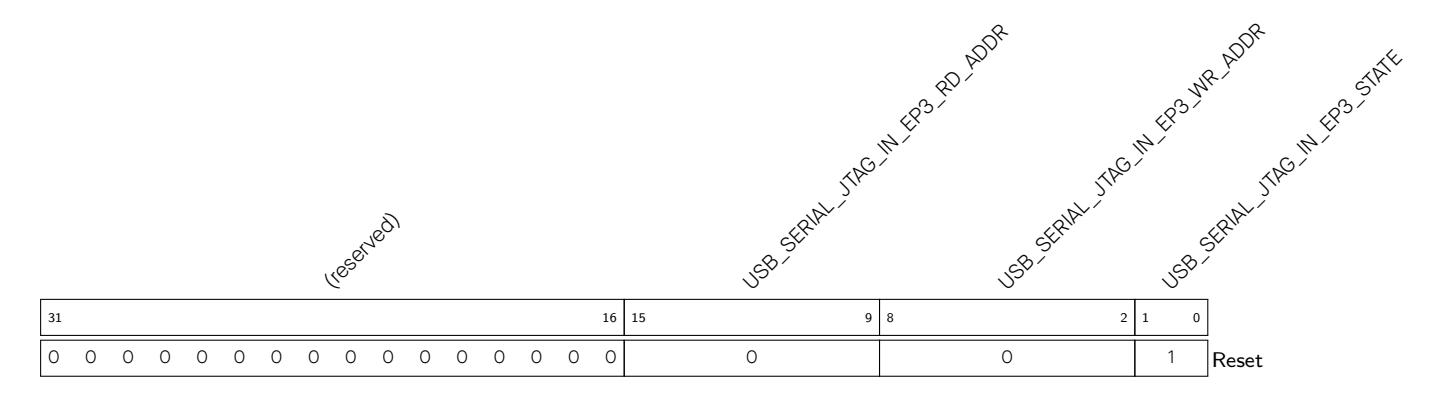

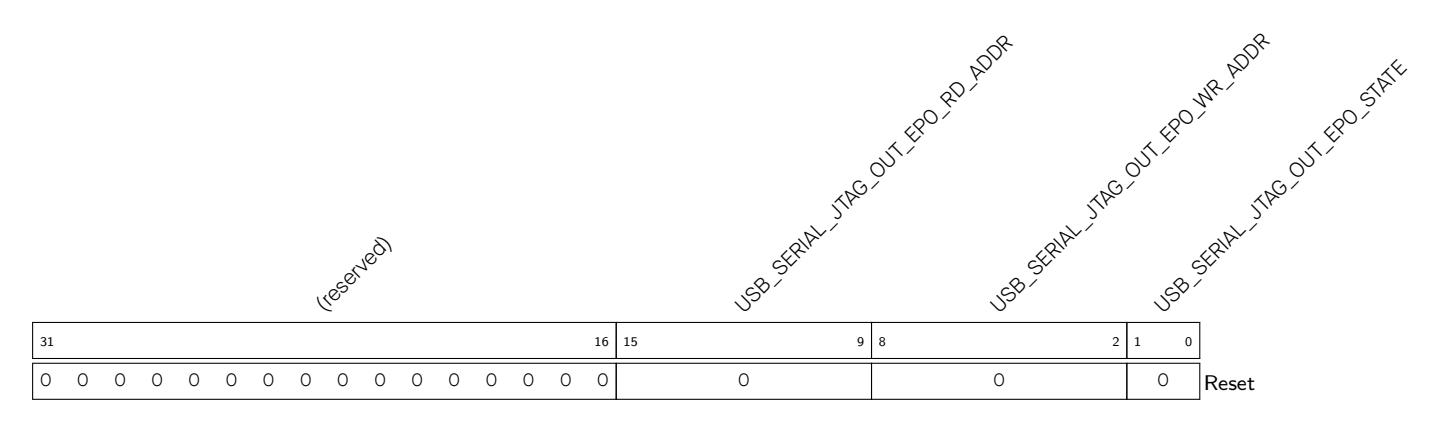

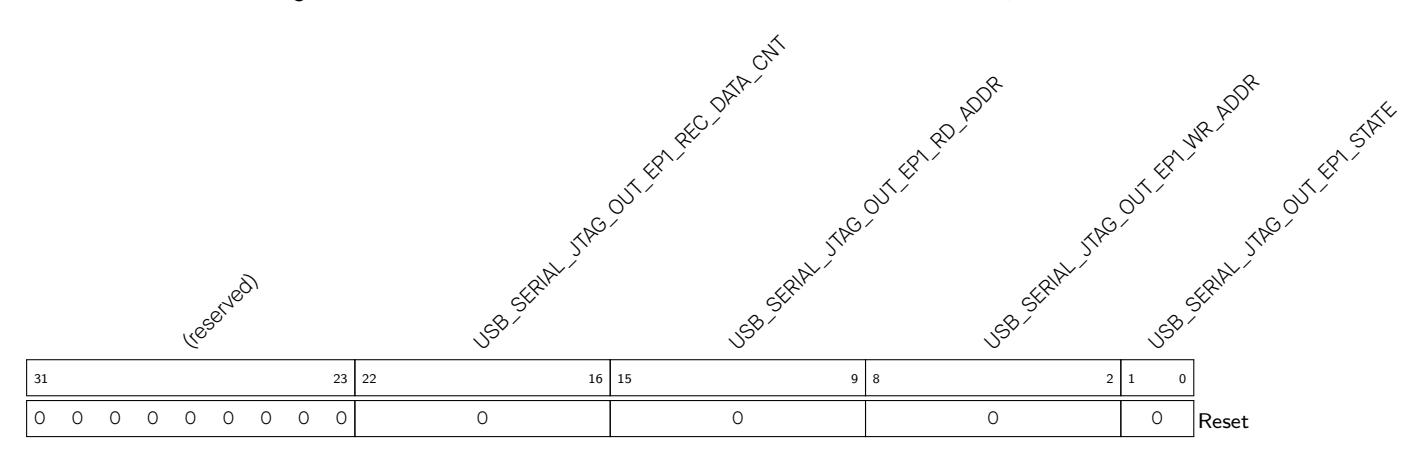

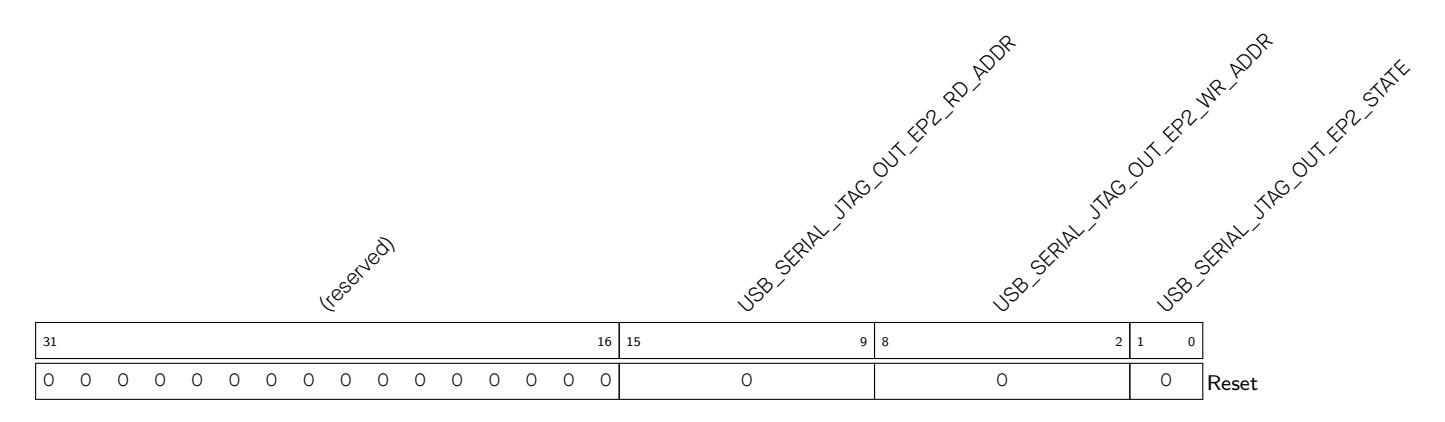

| 30 | USB Serial/JTAG Controller (USB_SERIAL_JTAG) | 764 | |

| 30.1 | Overview | 764 | |

| 30.2 | Features | 764 | |

| 30.3 | Functional Description | 765 | |

|

30.3.1

CDC-ACM USB Interface Functional Description 30.3.2 CDC-ACM Firmware Interface Functional Description |

765

767 |

||

|

30.3.3

USB-to-JTAG Interface |

767 | ||

|

30.3.4

JTAG Command Processor |

767 | ||

|

30.3.5

USB-to-JTAG Interface: CMD_REP usage example |

768 | ||

|

30.3.6

USB-to-JTAG Interface: Response Capture Unit |

769 | ||

|

30.3.7

USB-to-JTAG Interface: Control Transfer Requests |

770 | ||

| 30.4 | Recommended Operation | 770 | |

|

30.5

30.6 |

Register Summary

Registers |

773

774 |

|

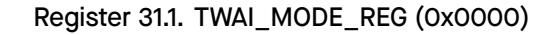

| 31 | Two-wire Automotive Interface (TWAI) | 788 | |

| 31.1 | Features | 788 | |

| 31.2 | Functional Protocol | 789 | |

|

31.2.1

TWAI Properties |

789 | ||

|

31.2.2

TWAI Messages |

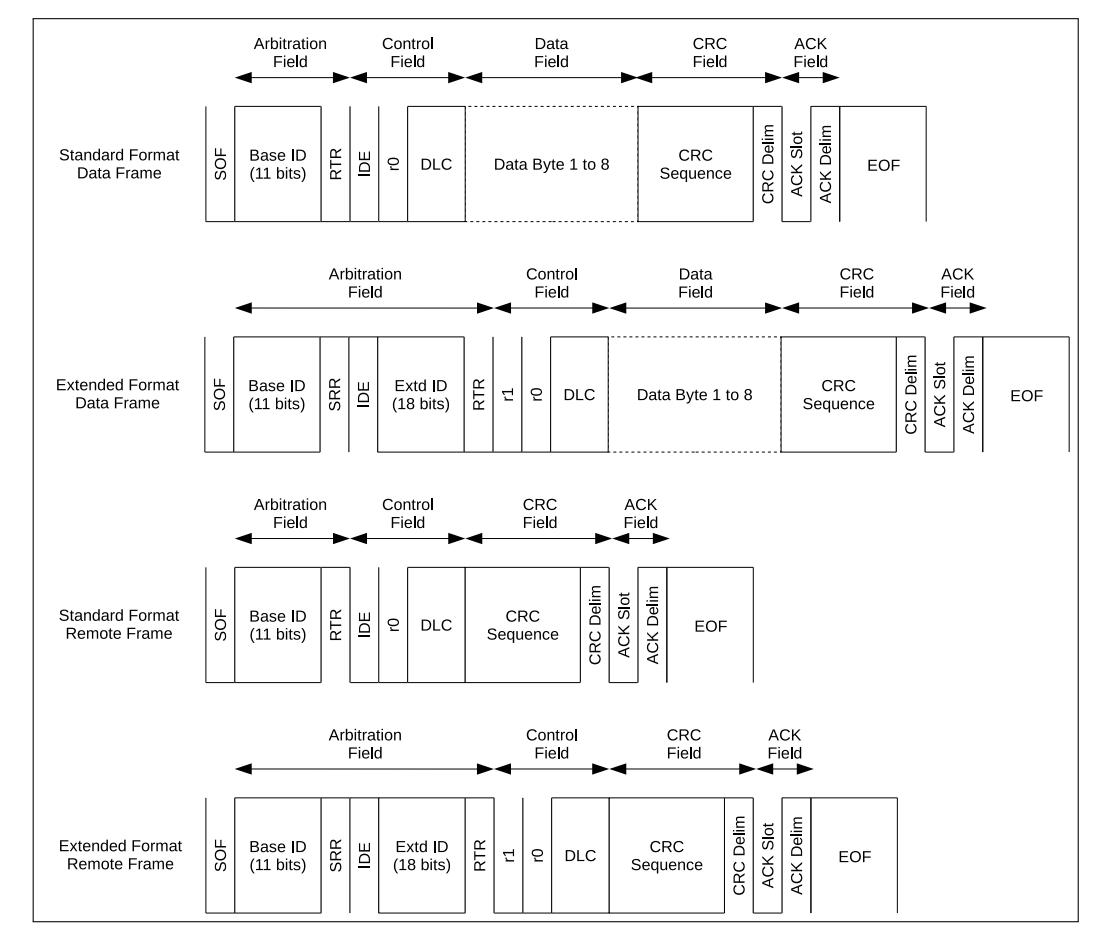

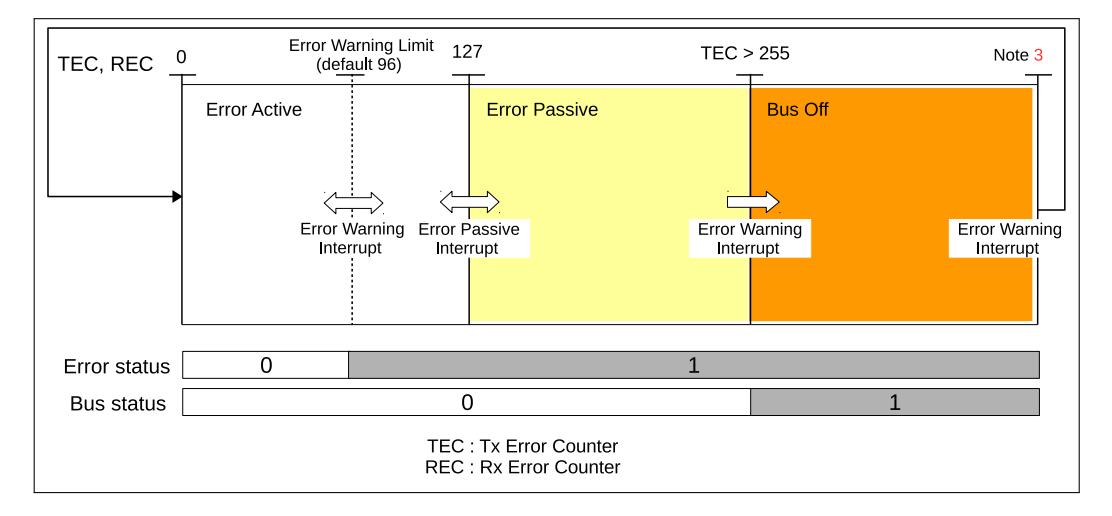

790 | ||

|

31.2.2.1

Data Frames and Remote Frames |

790 | ||

|

31.2.2.2

Error and Overload Frames |

792 | ||

|

31.2.2.3

Interframe Space 31.2.3 TWAI Errors |

794

794 |

||

|

31.2.3.1

Error Types |

794 | ||

|

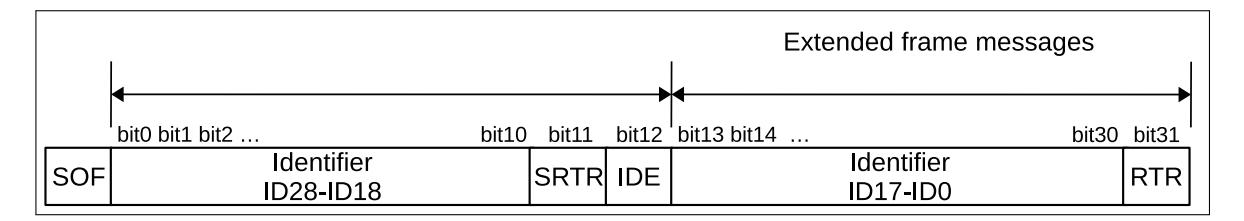

31.2.3.2

Error States |

795 | ||

|

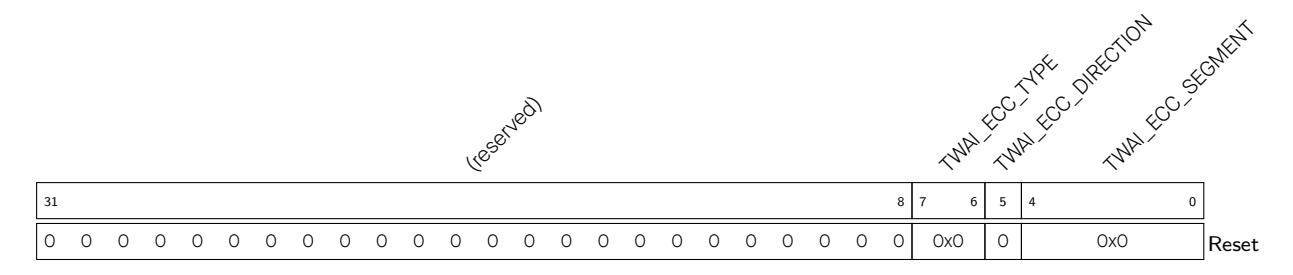

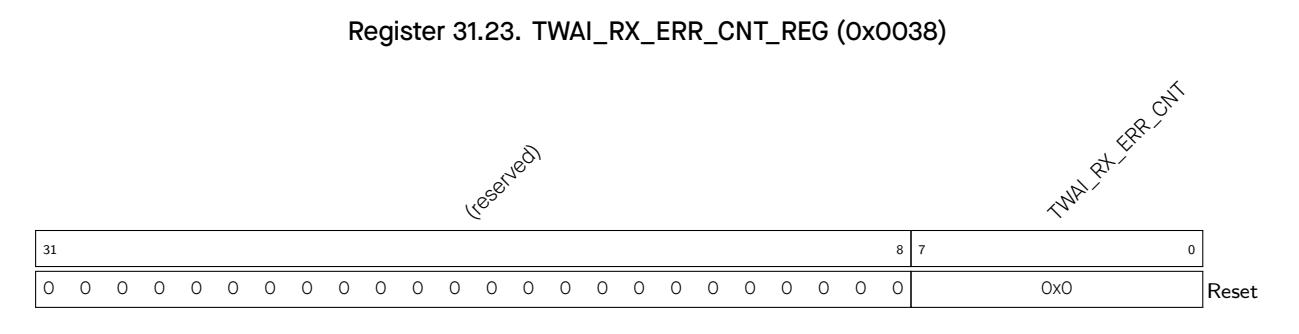

31.2.3.3

Error Counters |

795 | ||

|

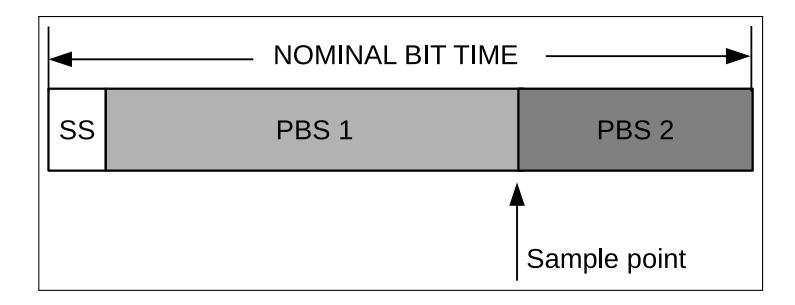

31.2.4

TWAI Bit Timing |

796 | ||

|

31.2.4.1

Nominal Bit |

796 | ||

|

31.2.4.2

Hard Synchronization and Resynchronization |

797 | ||

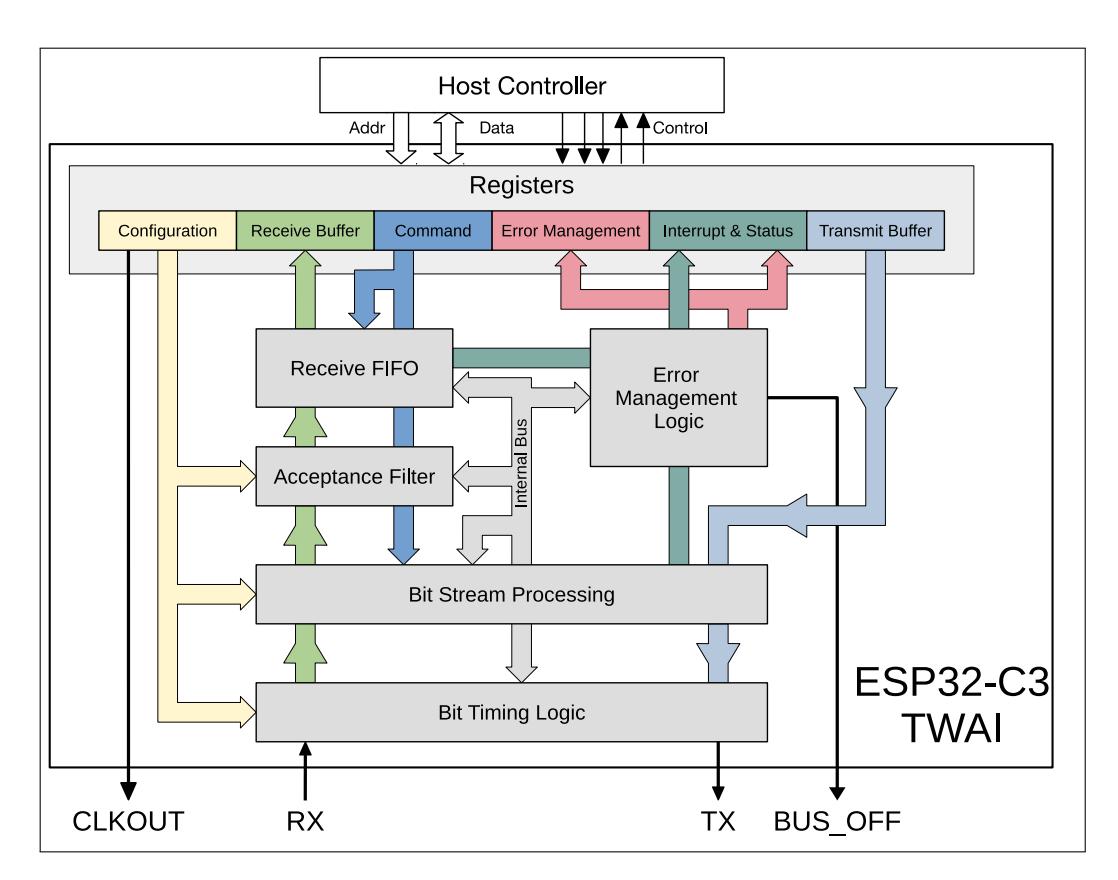

| 31.3 | Architectural Overview | 798 | |

|

31.3.1

Registers Block |

798 | ||

|

31.3.2

Bit Stream Processor |

799 | ||

|

31.3.3

Error Management Logic |

799 | ||

|

31.3.4

Bit Timing Logic |

800 | ||

|

31.3.5

Acceptance Filter 31.3.6 Receive FIFO |

800

800 |

||

| 31.4 | Functional Description | 800 | |

|

31.4.1

Modes |

800 | ||

|

31.4.1.1

Reset Mode |

800 | ||

| Contents | GoBack | |||

| 31.4.1.2 | Operation Mode | 800 | ||

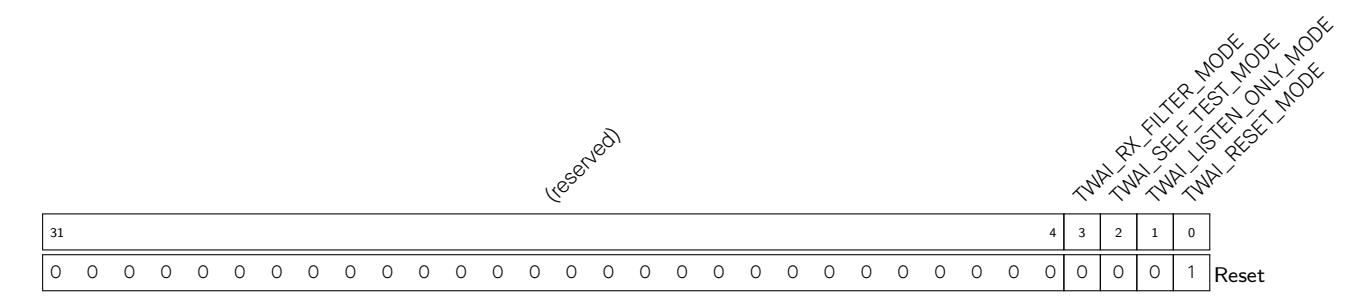

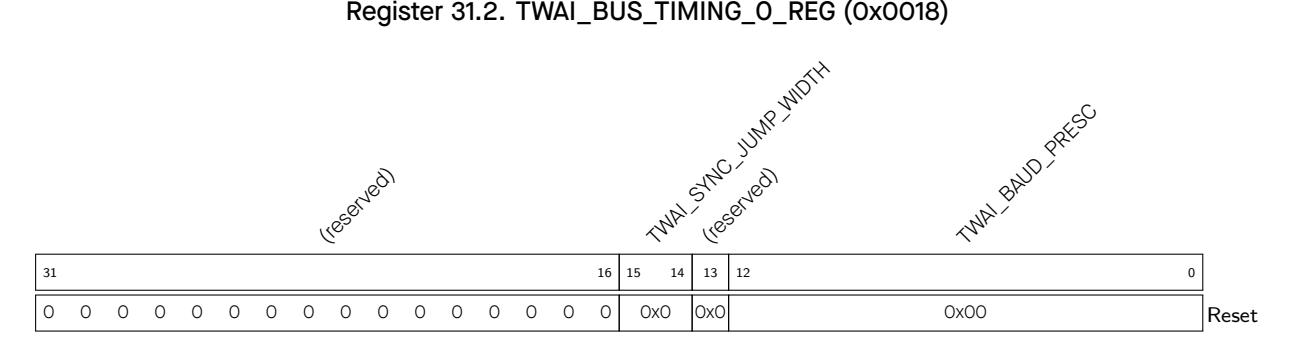

| 31.4.2 | Bit Timing | 801 | ||

| 31.4.3 | Interrupt Management | 802 | ||

| 31.4.3.1 | Receive Interrupt (RXI) | 802 | ||

| 31.4.3.2 | Transmit Interrupt (TXI) | 802 | ||

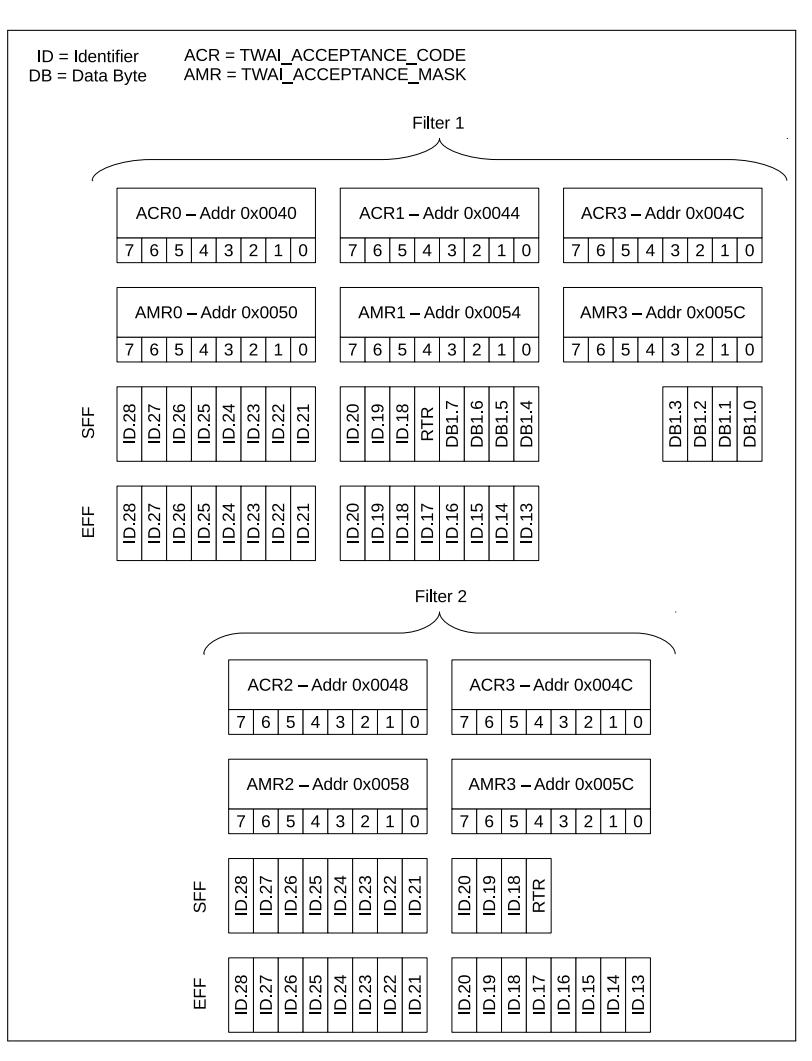

| 31.4.3.3 | Error Warning Interrupt (EWI) | 802 | ||

| 31.4.3.4 | Data Overrun Interrupt (DOI) | 803 | ||

| 31.4.3.5 | Error Passive Interrupt (TXI) | 803 | ||

| 31.4.3.6 | Arbitration Lost Interrupt (ALI) | 803 | ||

|

31.4.3.7

31.4.3.8 |

Bus Error Interrupt (BEI)

Bus Status Interrupt (BSI) |

803

804 |

||

| 31.4.4 | Transmit and Receive Buffers | 804 | ||

| 31.4.4.1 | Overview of Buffers | 804 | ||

| 31.4.4.2 | Frame Information | 805 | ||

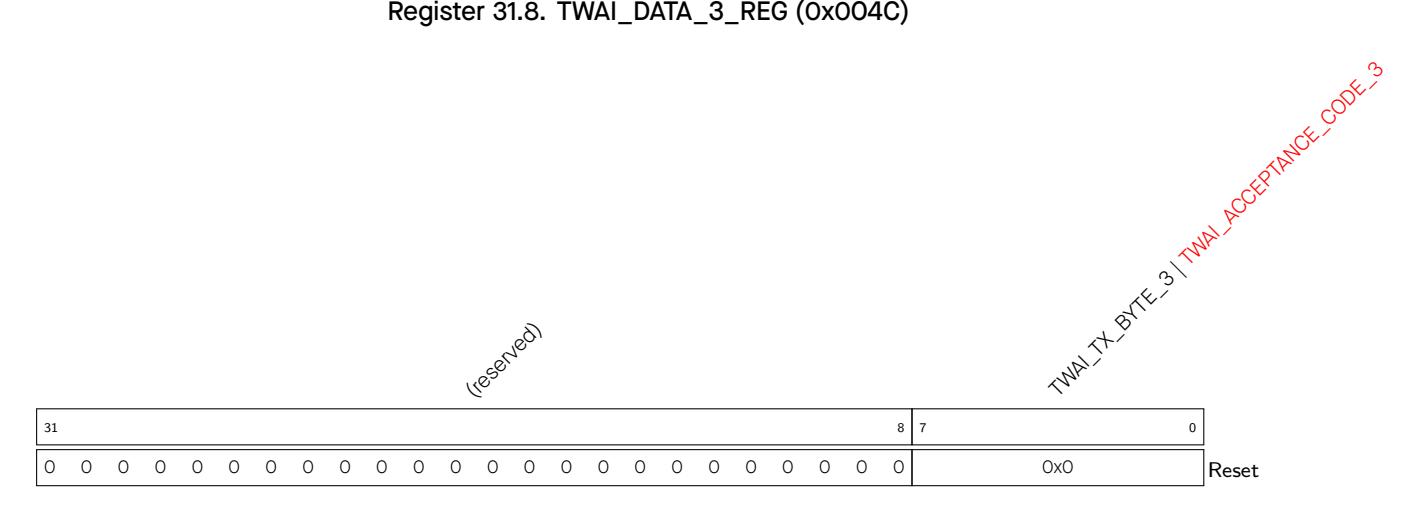

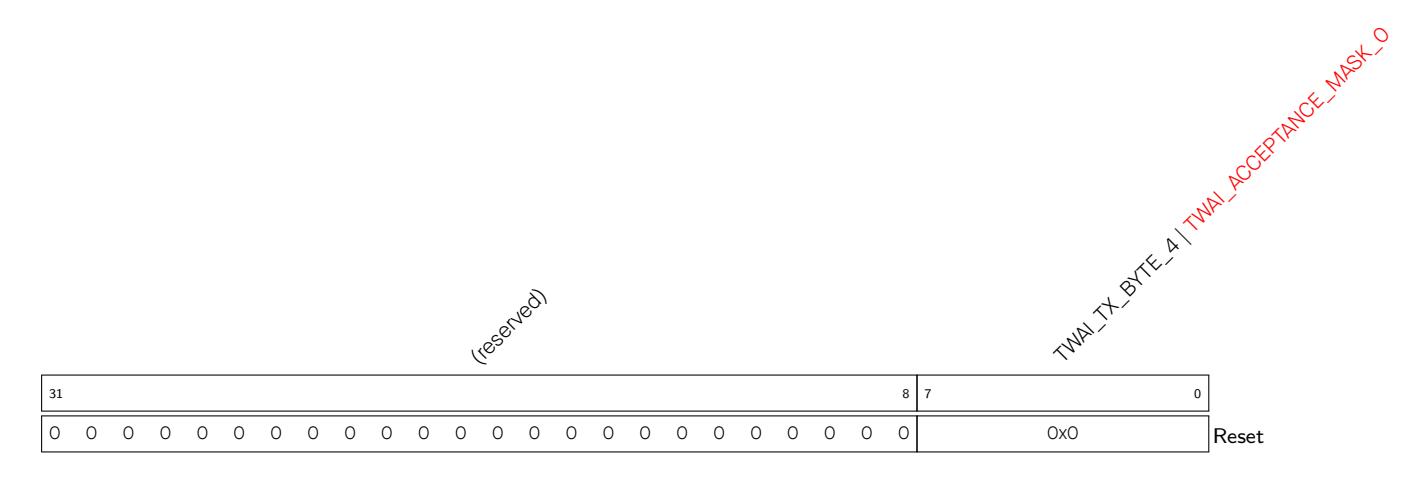

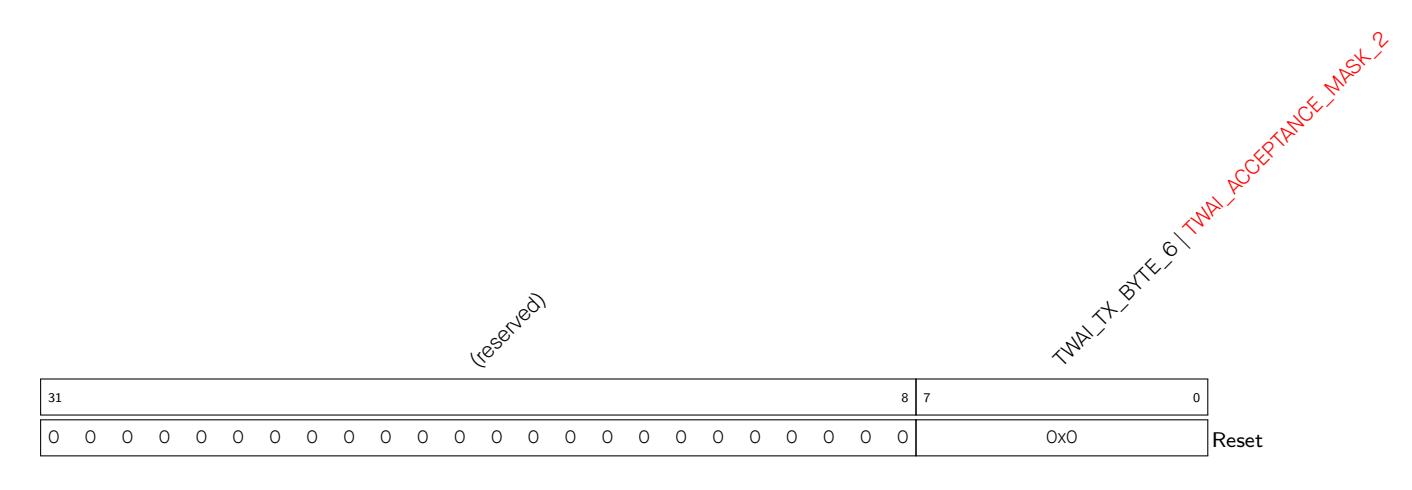

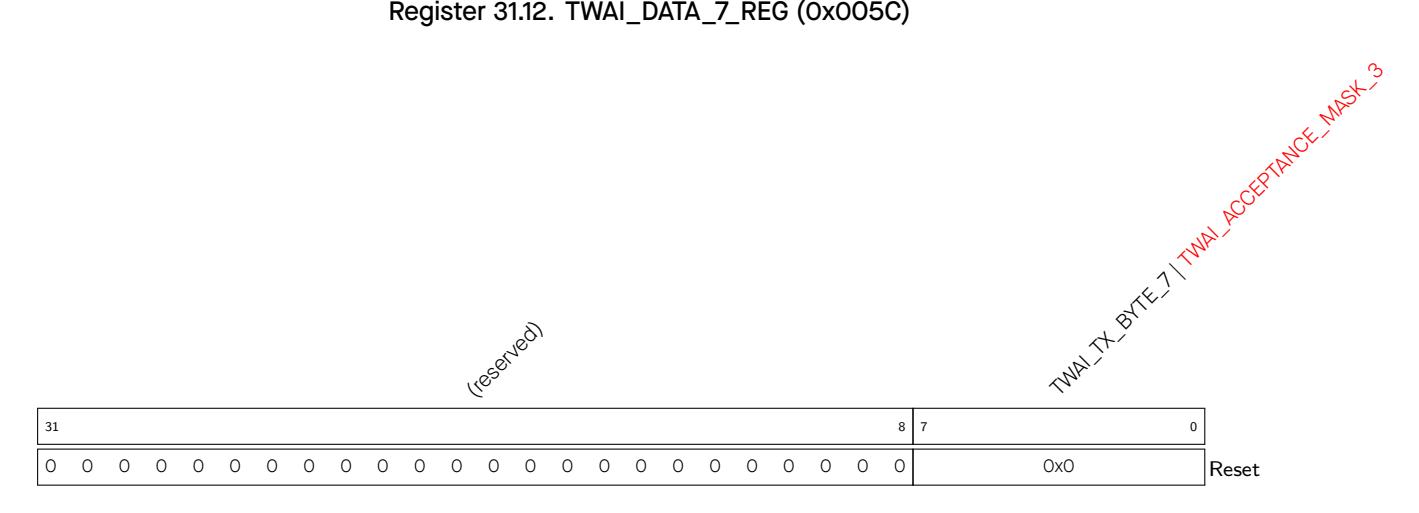

| 31.4.4.3 | Frame Identifier | 805 | ||

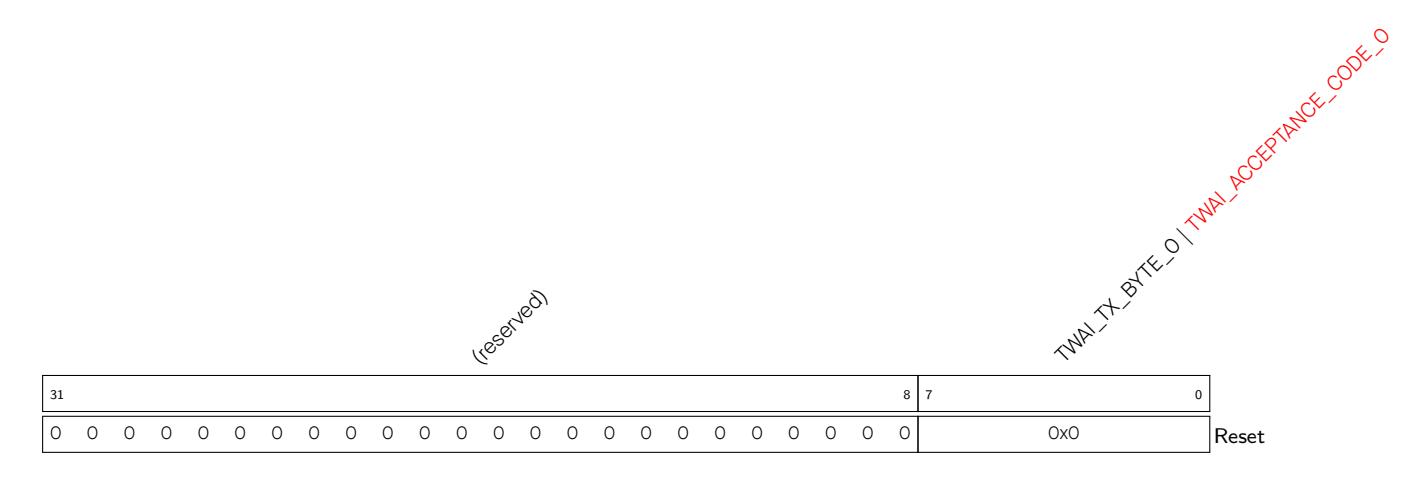

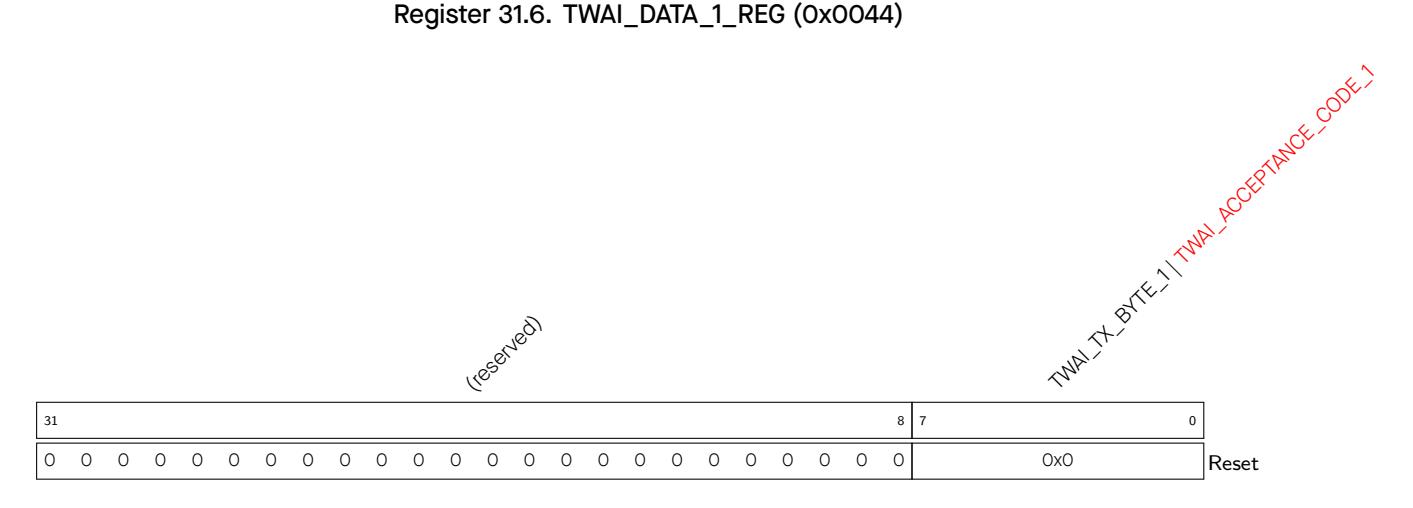

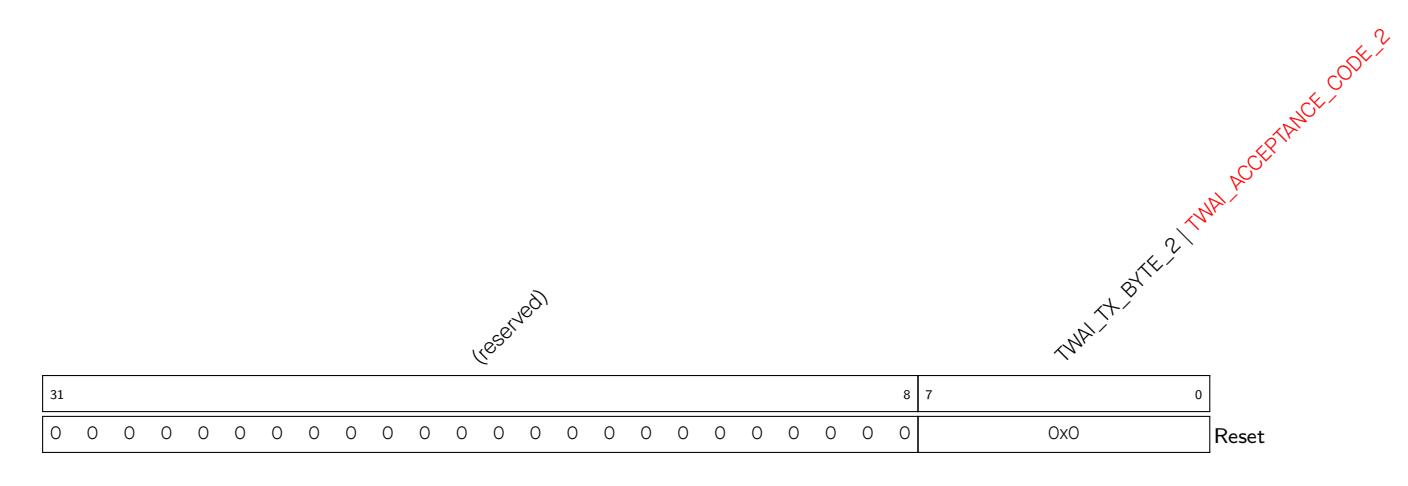

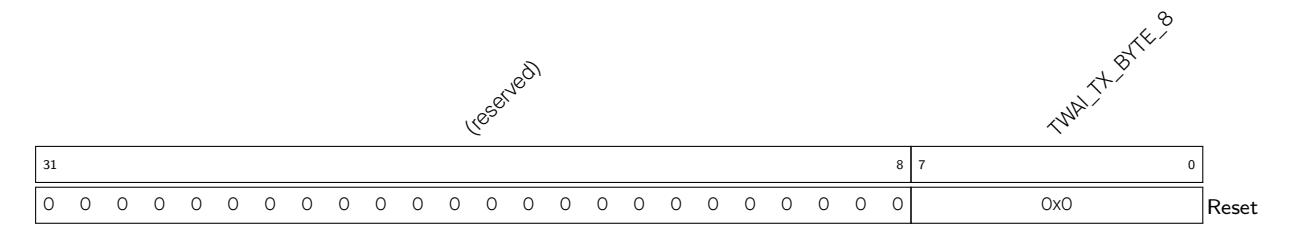

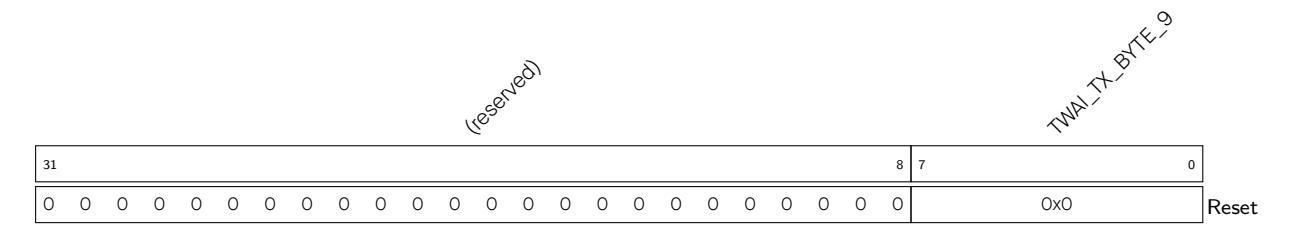

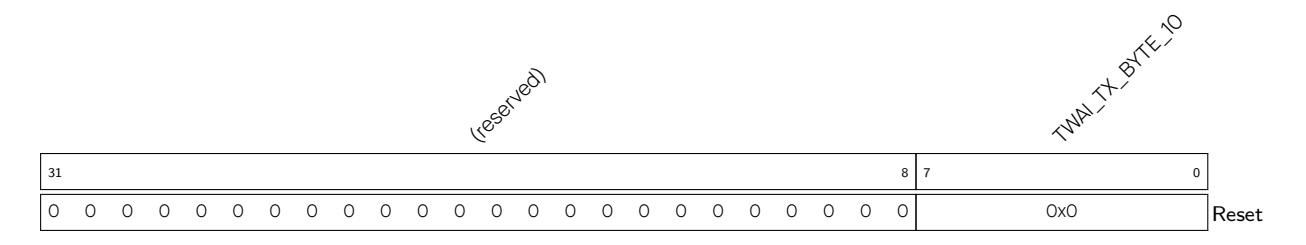

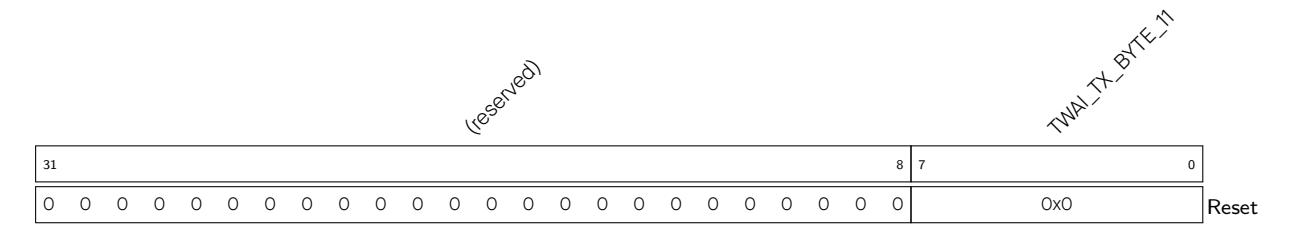

| 31.4.4.4 | Frame Data | 806 | ||

| 31.4.5 | Receive FIFO and Data Overruns | 806 | ||

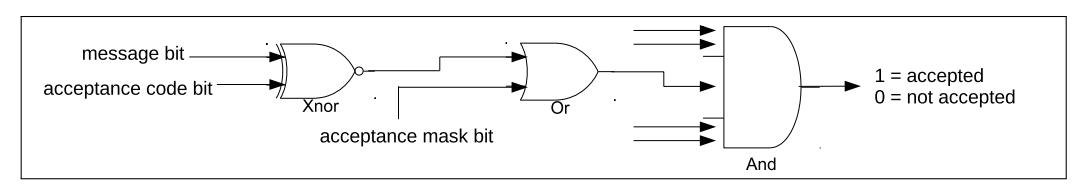

| 31.4.6 | Acceptance Filter | 807 | ||

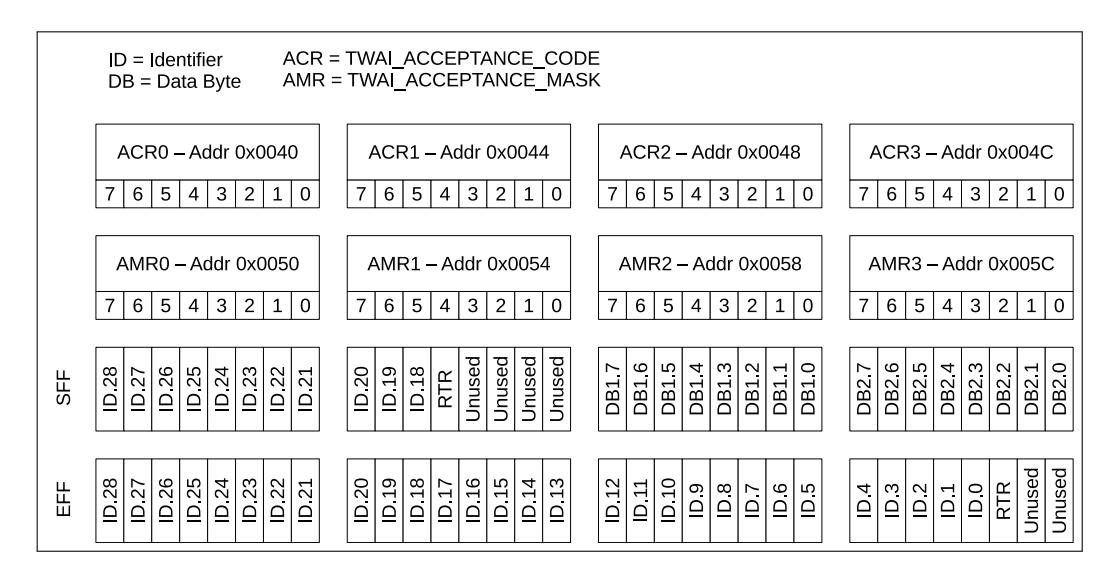

| 31.4.6.1 | Single Filter Mode | 808 | ||

| 31.4.6.2 | Dual Filter Mode | 808 | ||

| 31.4.7 | Error Management | 809 | ||

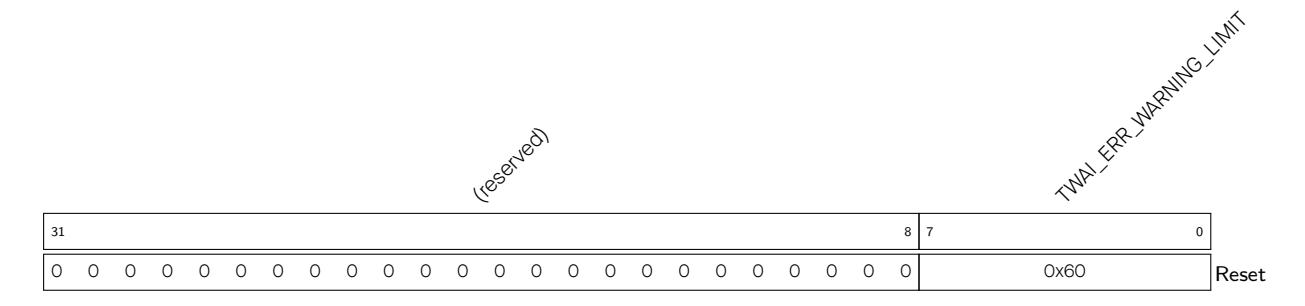

| 31.4.7.1 | Error Warning Limit | 810 | ||

| 31.4.7.2 | Error Passive | 810 | ||

| 31.4.7.3 | Bus-Off and Bus-Off Recovery | 810 | ||

| 31.4.8 | Error Code Capture | |||

| 31.5 | 31.4.9 | Register Summary | Arbitration Lost Capture |

812

813 |

| 31.6 | Registers | 814 | ||

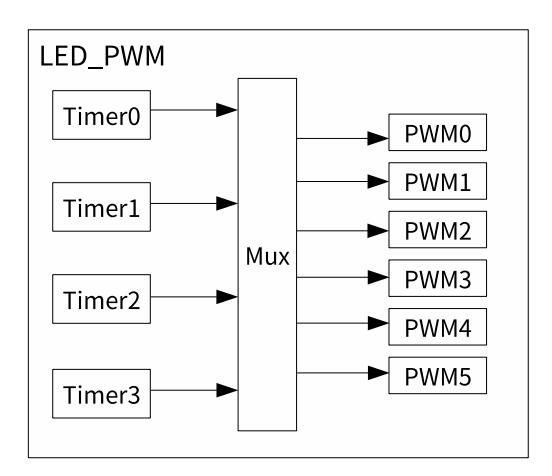

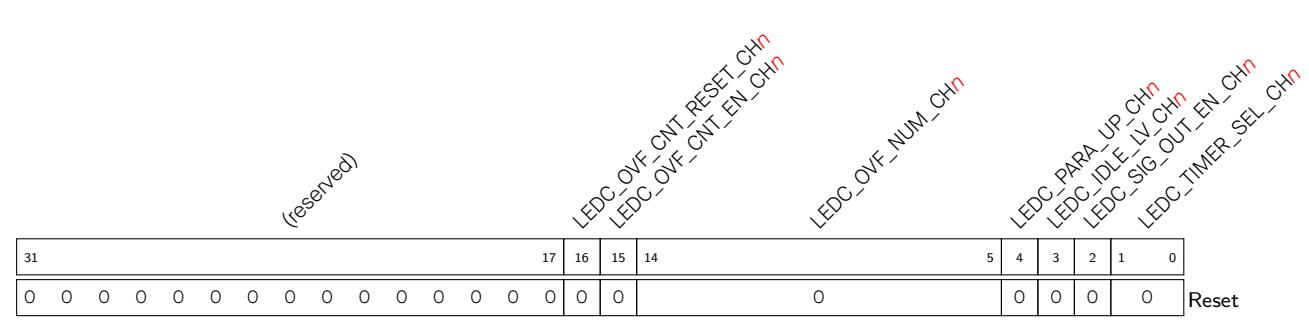

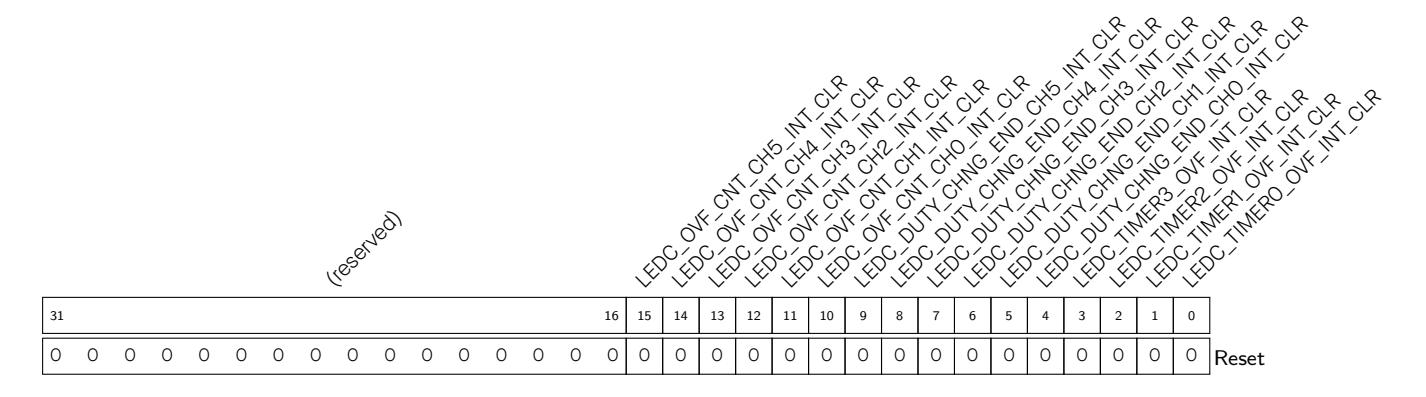

| 32 | LED PWM Controller (LEDC) | 827 | ||

| 32.1 | Overview | 827 | ||

| 32.2 | Features | 827 | ||

| 32.3 | Functional Description | 828 | ||

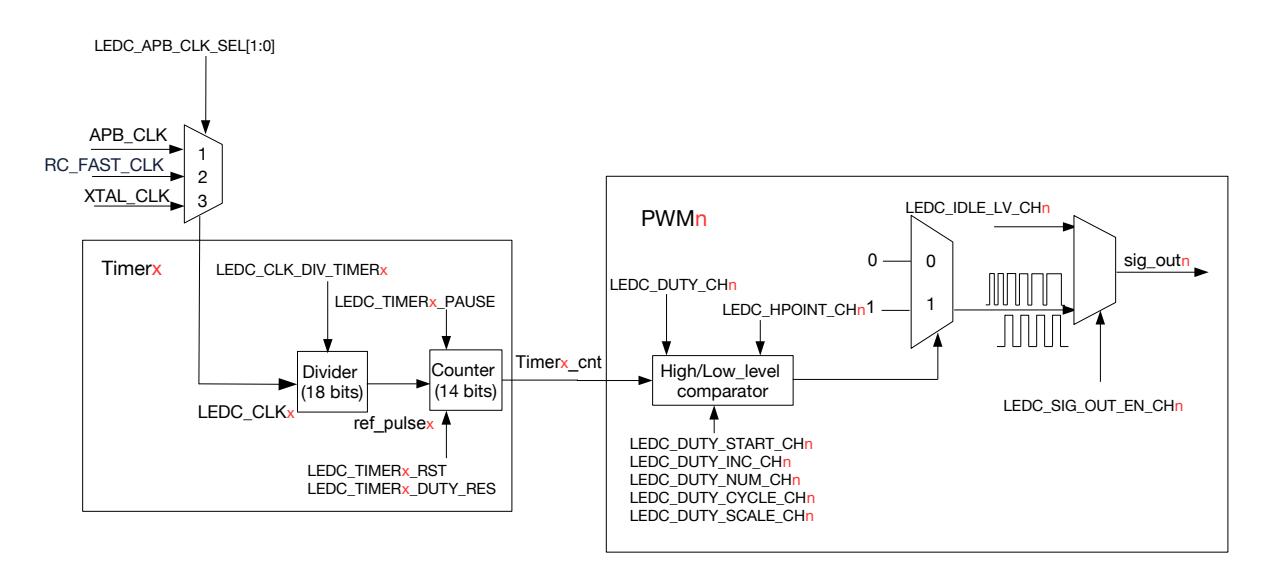

| 32.3.1 | Architecture | 828 | ||

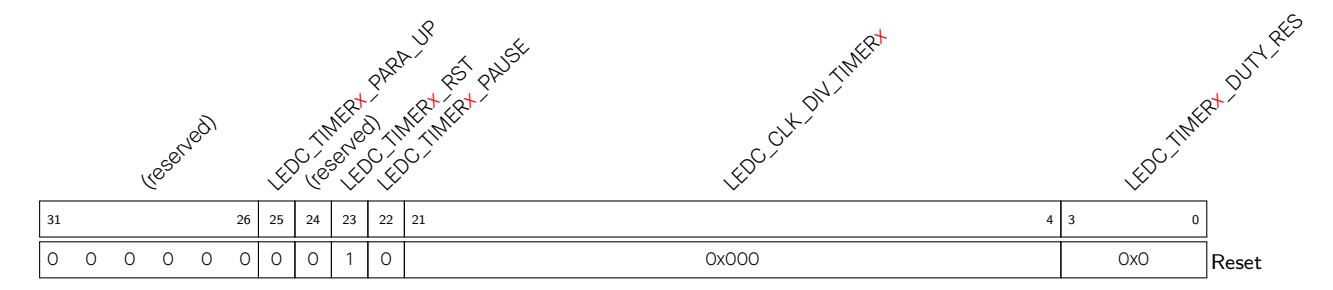

| 32.3.2 | Timers | 828 | ||

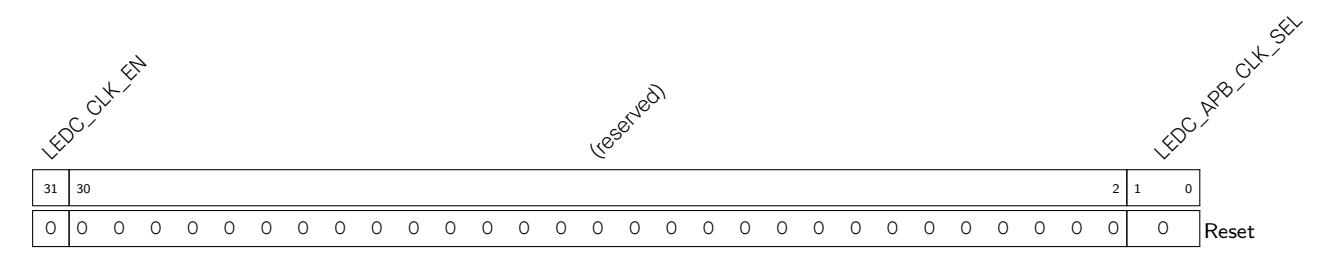

| 32.3.2.1 | Clock Source | 828 | ||

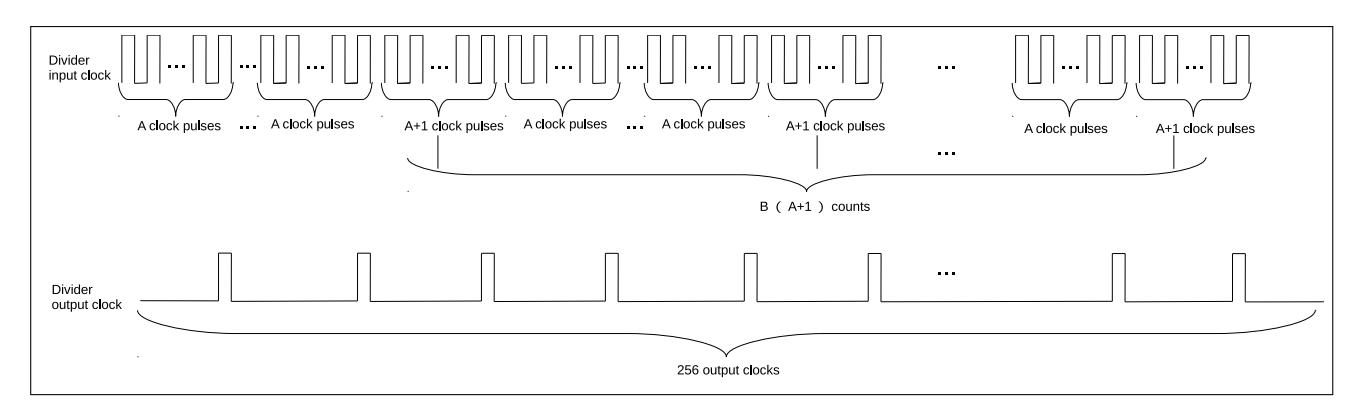

| 32.3.2.2 | Clock Divider Configuration | 829 | ||

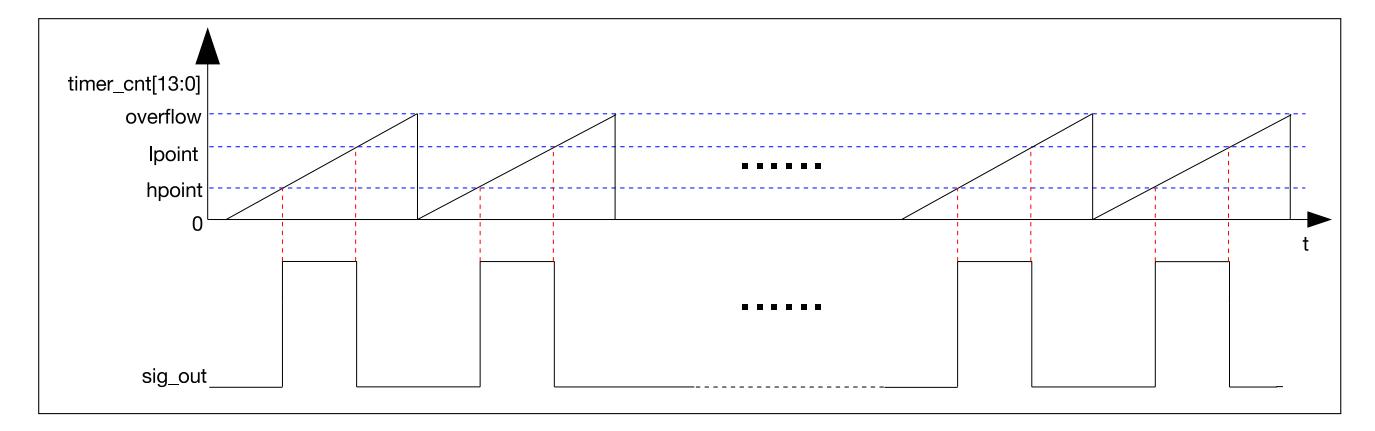

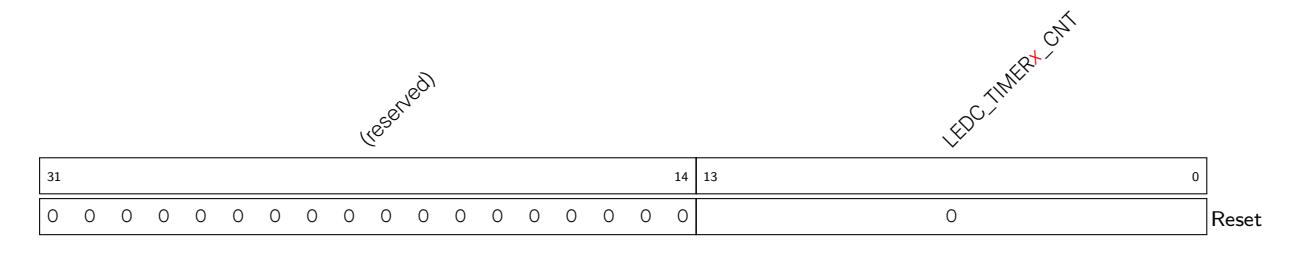

| 32.3.2.3 | 14-bit Counter | 830 | ||

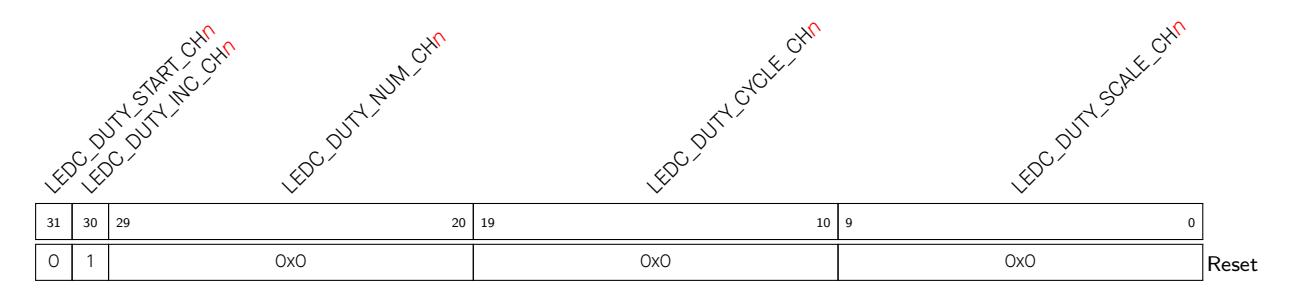

| 32.3.3 | PWM Generators | 831 | ||

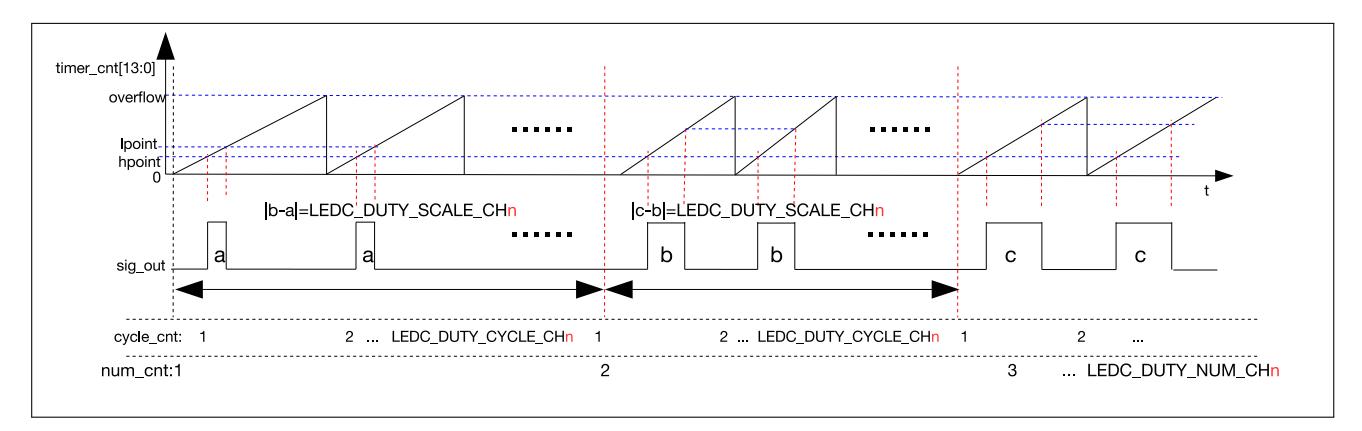

| 32.3.4 | Duty Cycle Fading | 832 | ||

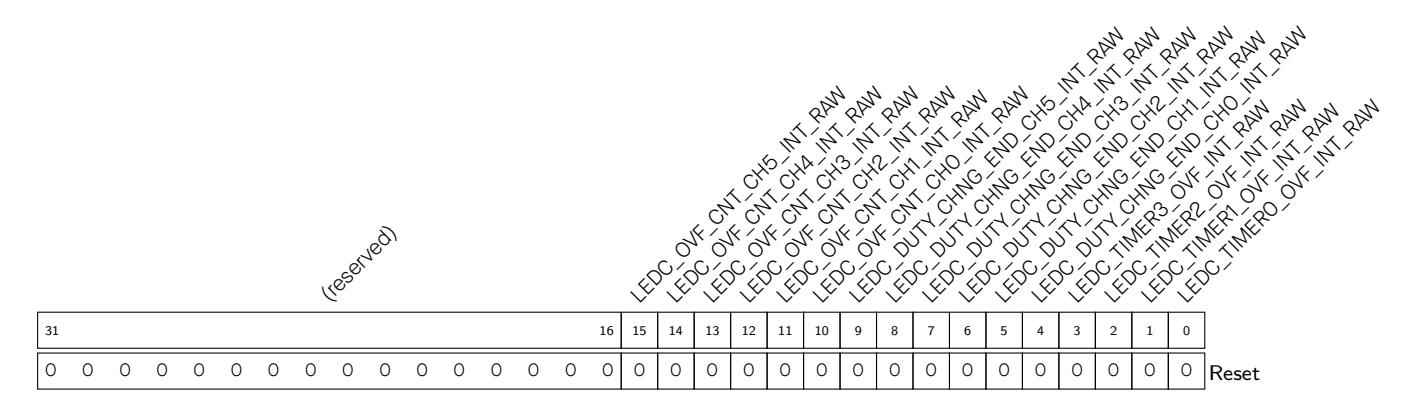

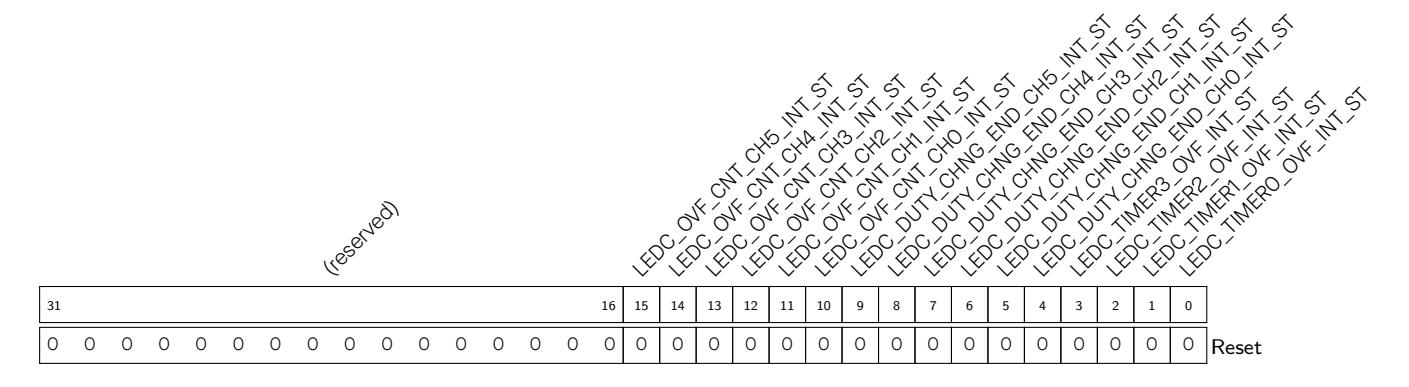

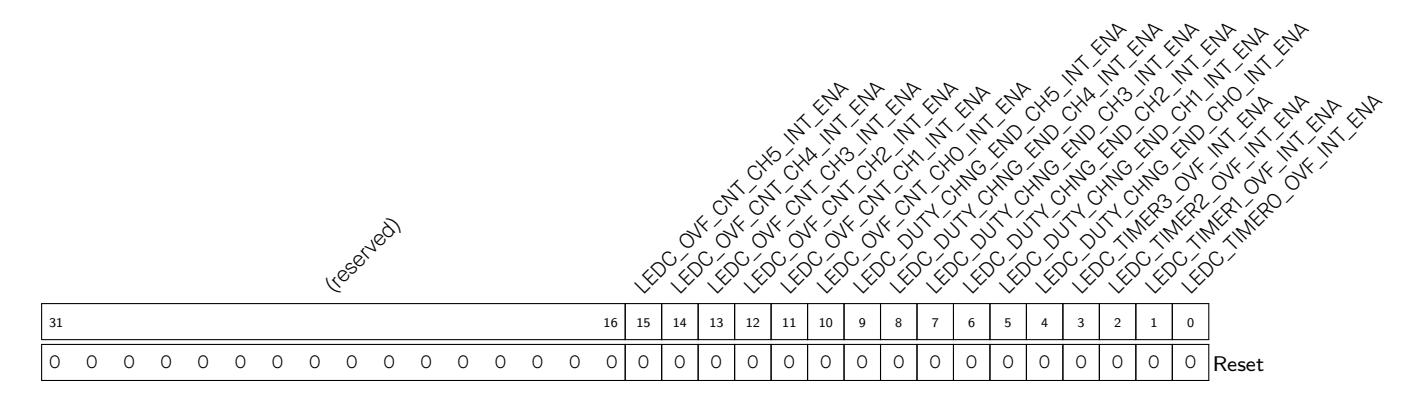

| 32.3.5 | Interrupts | 833 | ||

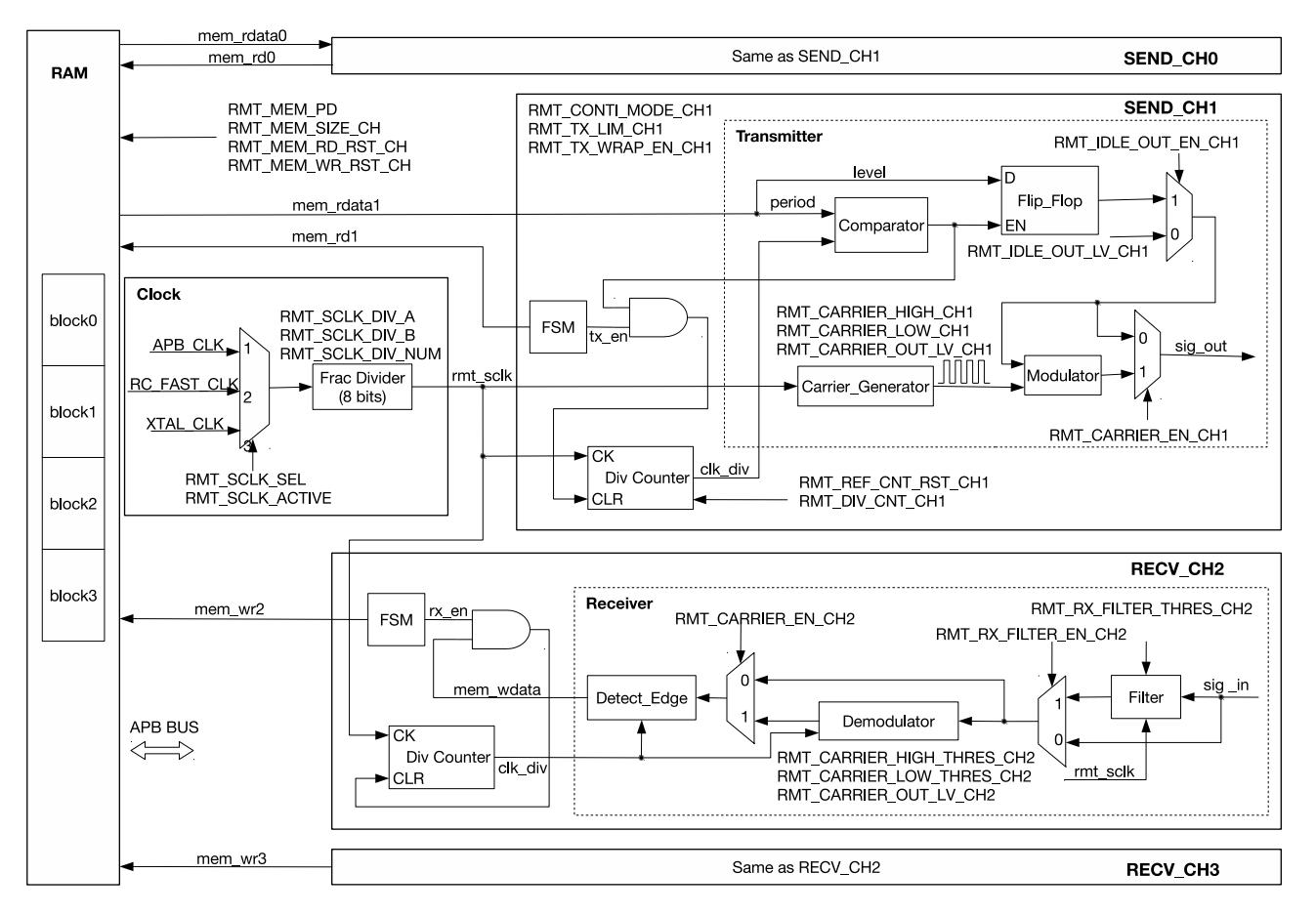

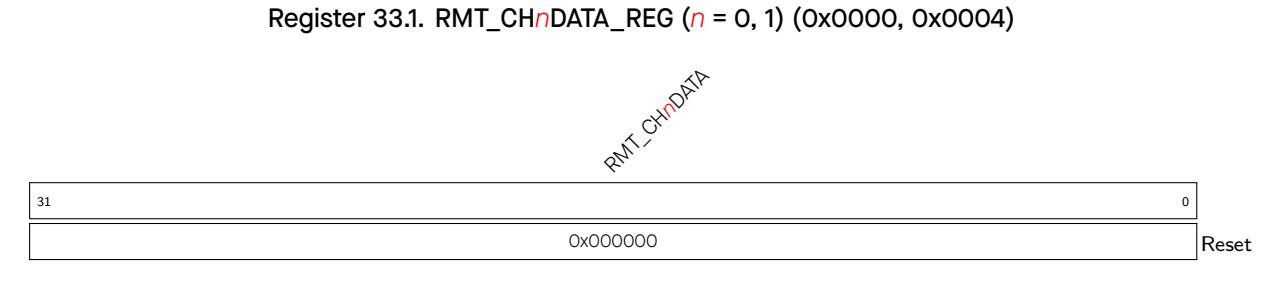

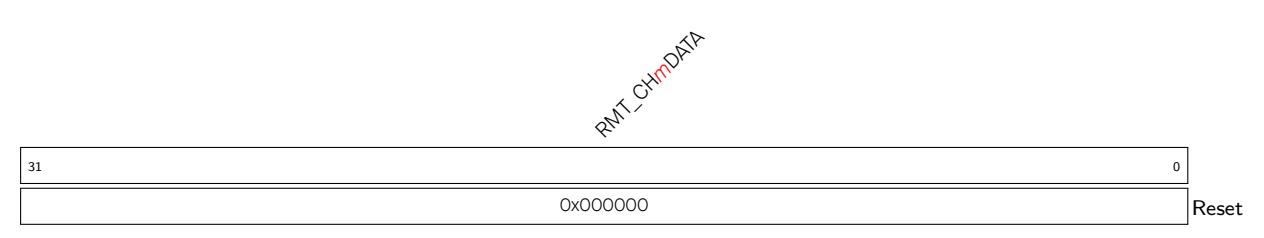

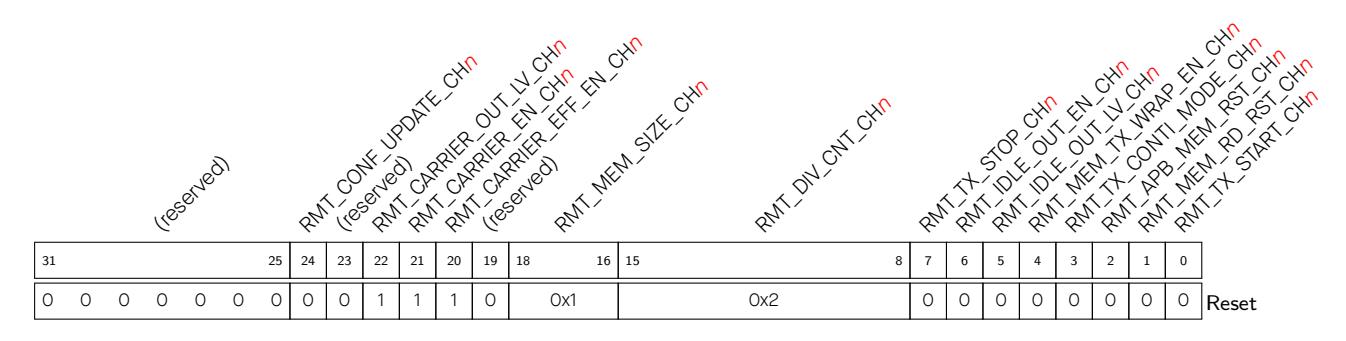

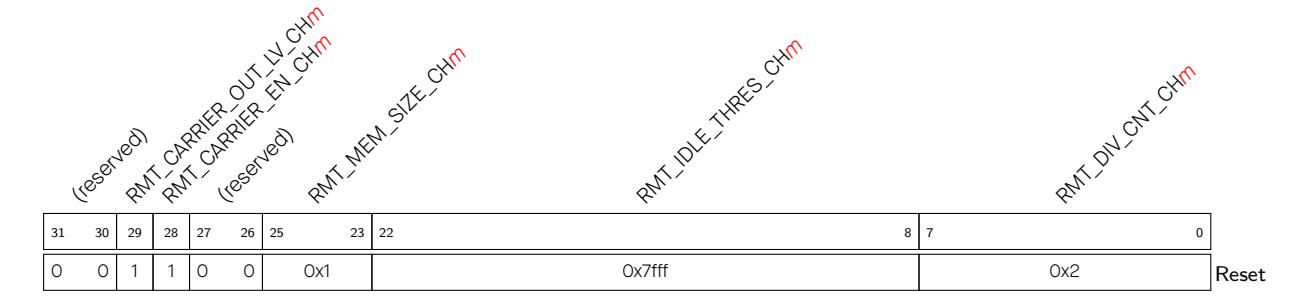

33 Remote Co ntrol Peripheral (RMT) 843

33.1 Overview 843

32.5 Registers 836

| 33.2 | ||

|---|---|---|

| Features | 843 | |

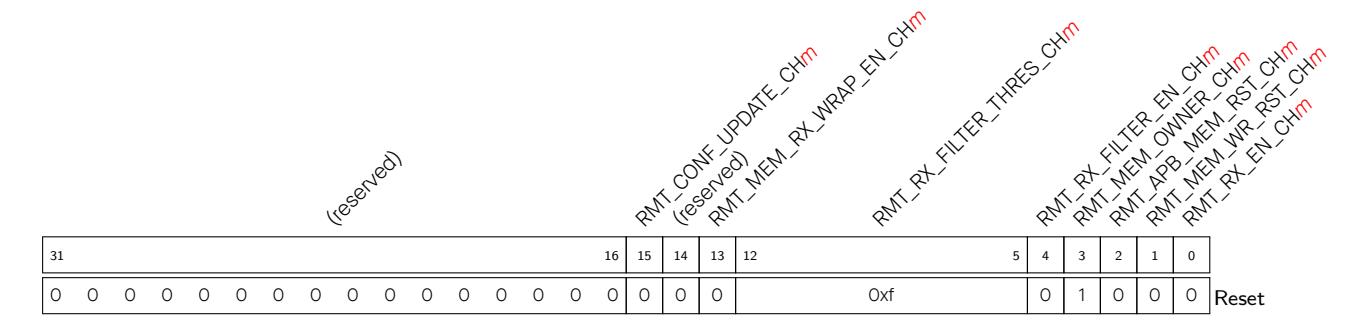

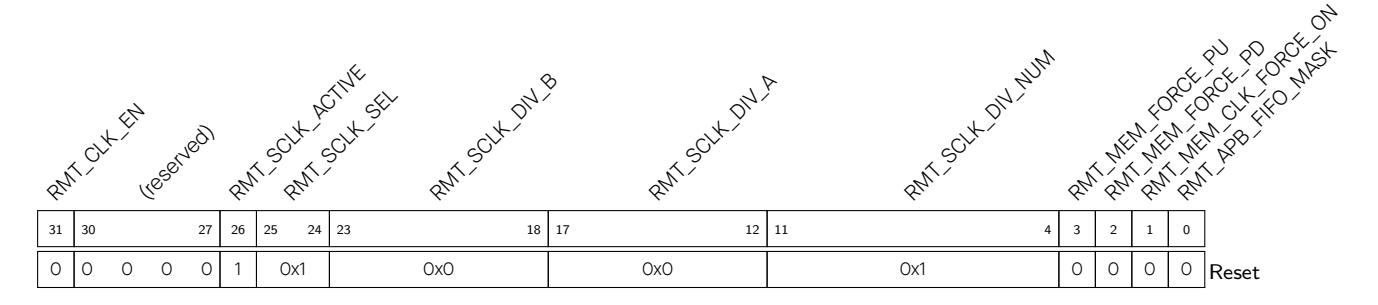

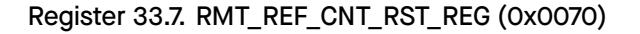

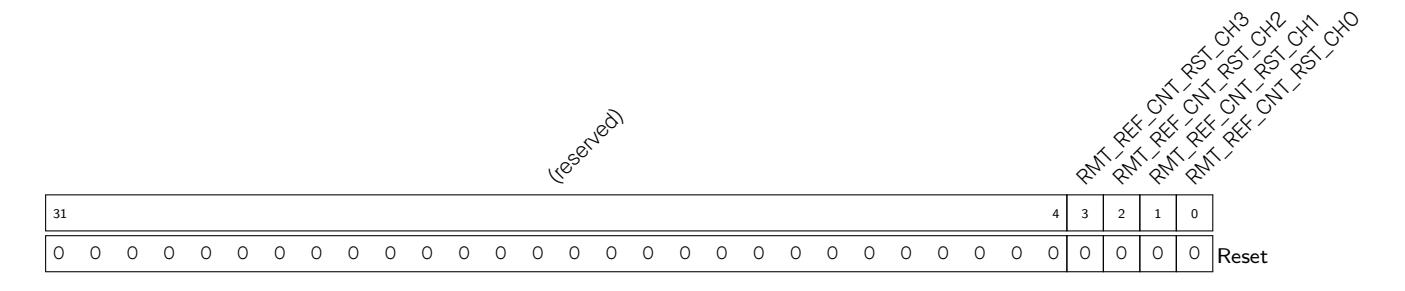

| 33.3 | Functional Description | 843 |

|

RMT Architecture

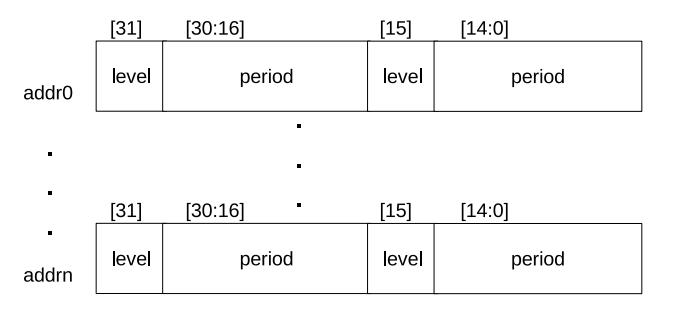

33.3.1 |

844 | |

| 33.3.2 RMT RAM | 844 | |

| 33.3.3 Clock | 845 | |

| 33.3.4 Transmitter | 846 | |

|

Normal TX Mode

33.3.4.1 |

846 | |

| 33.3.4.2 Wrap TX Mode | 846 | |

| 33.3.4.3 TX Modulation | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | |

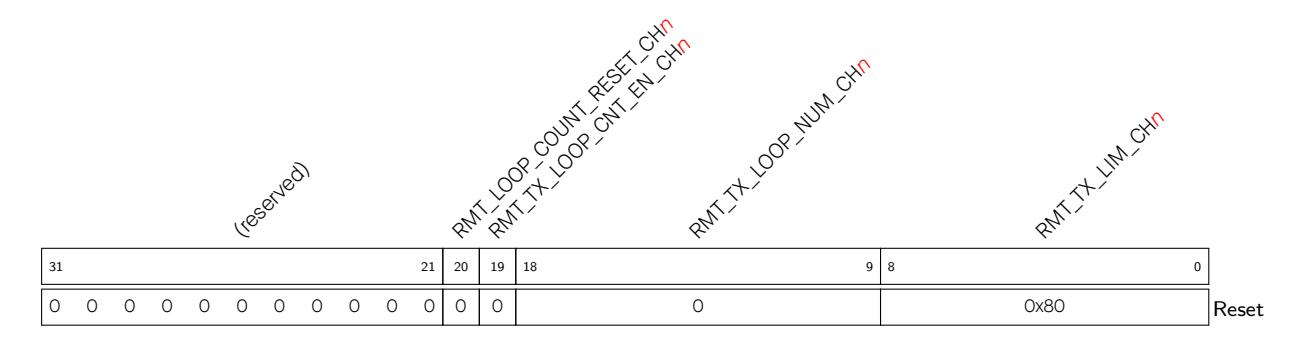

| 33.3.4.4 Continuous TX Mode | 847 | |

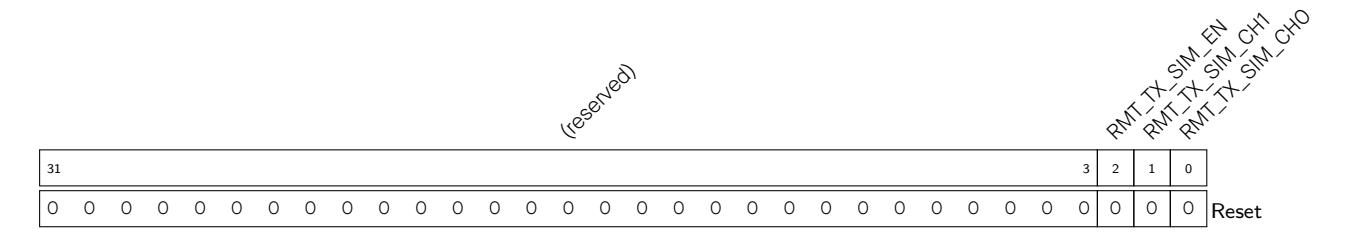

| 33.3.4.5 Simultaneous TX Mode | 847 | |

| 33.3.5 Receiver | 847 | |

| 33.3.5.1 Normal RX Mode | 848 | |

| 33.3.5.2 Wrap RX Mode | 848 | |

| 33.3.5.3 RX Filtering | 848 | |

| 33.3.5.4 RX Demodulation | 849 | |

| 33.3.6 Configuration Update | 849 | |

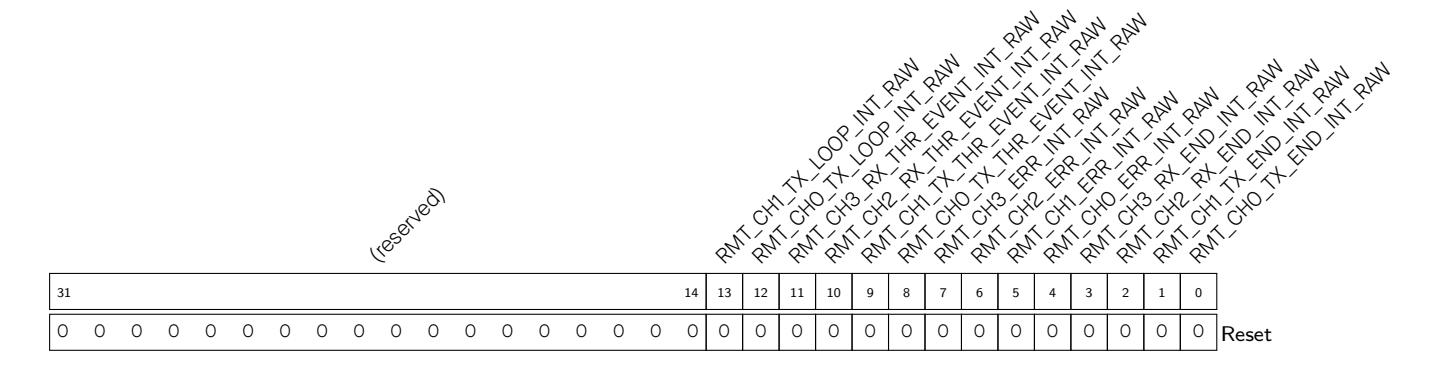

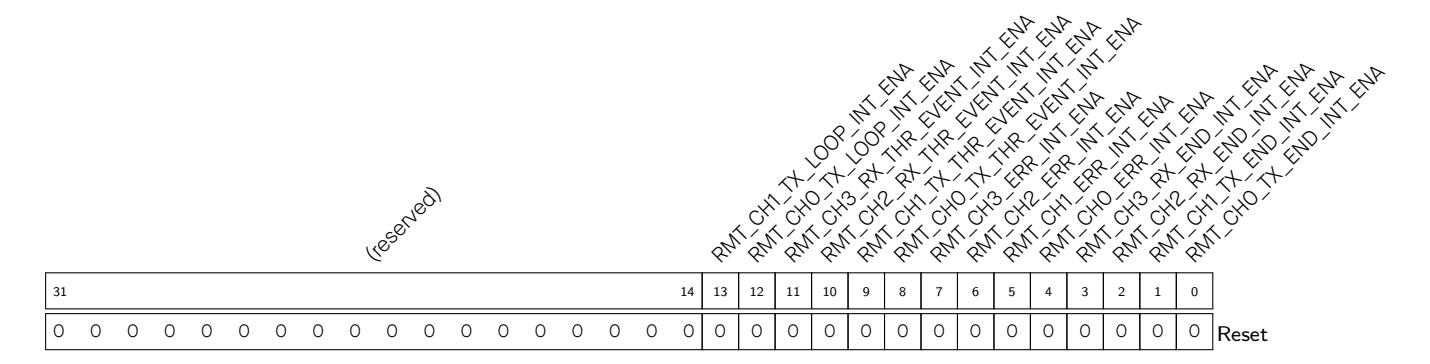

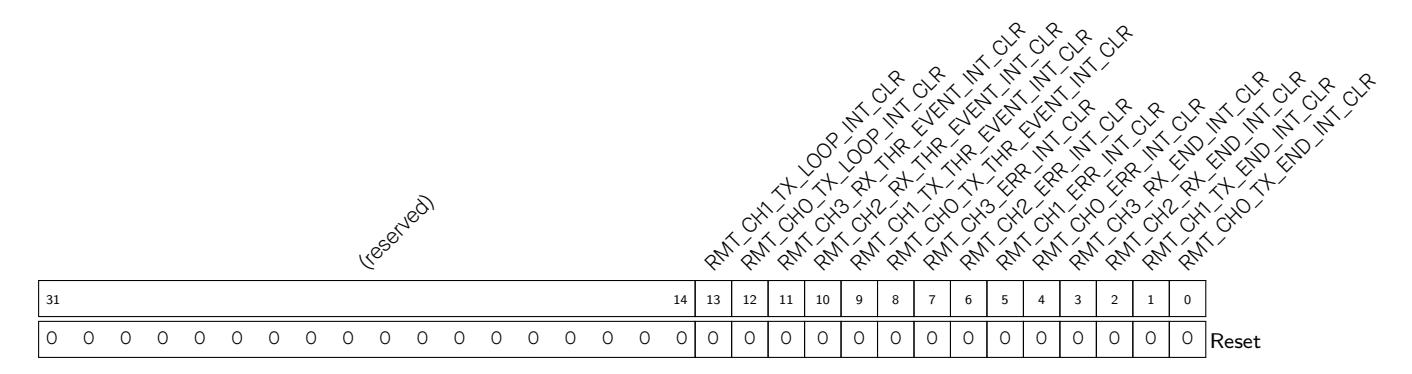

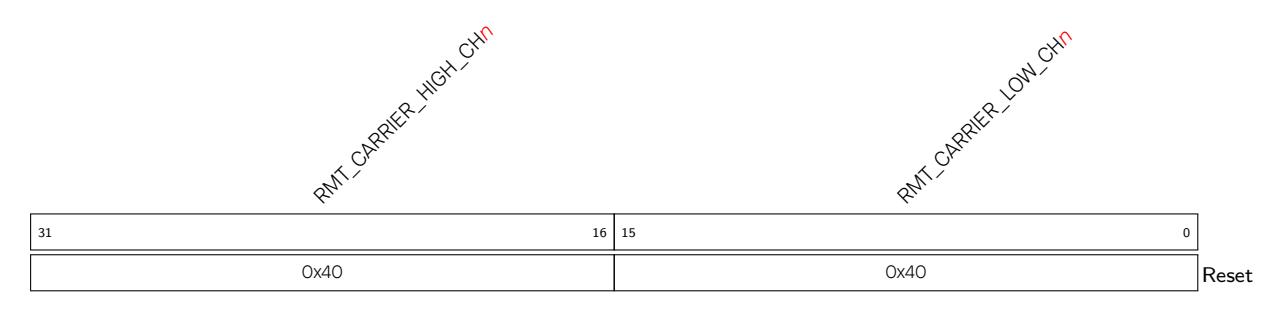

| 33.3.7 Interrupts | 850 | |

| 33.4 | Register Summary | 851 |

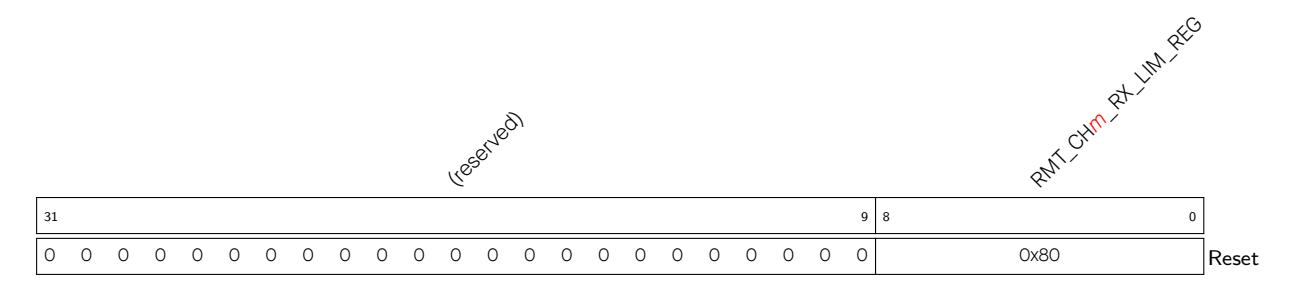

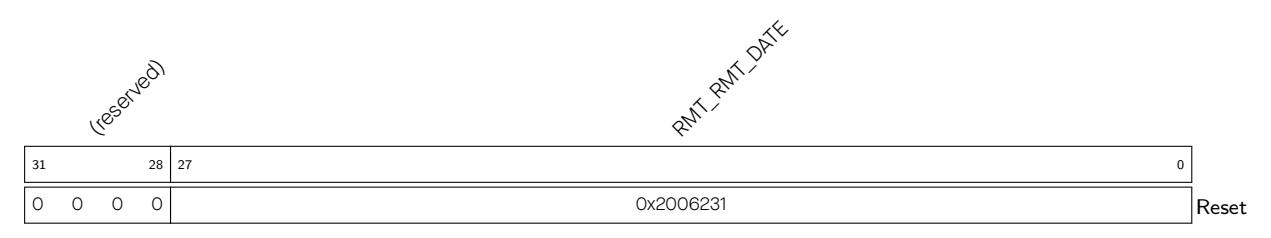

| 33.5 | Registers | 852 |

| VI | Analog Signal Processing | 867 |

| 34 | On-Chip Sensor and Analog Signal Processing | 868 |

| 34.1 | Overview | |

| 868 | ||

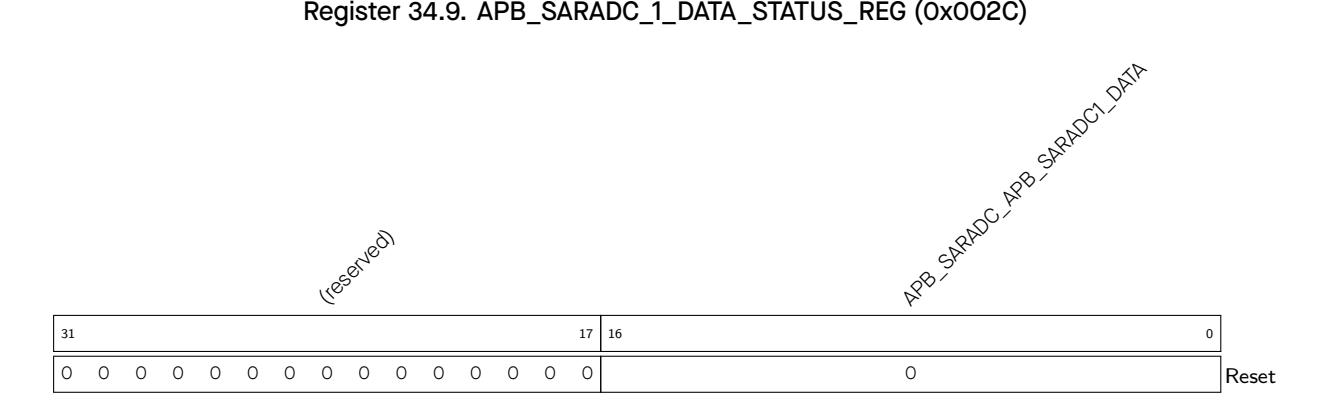

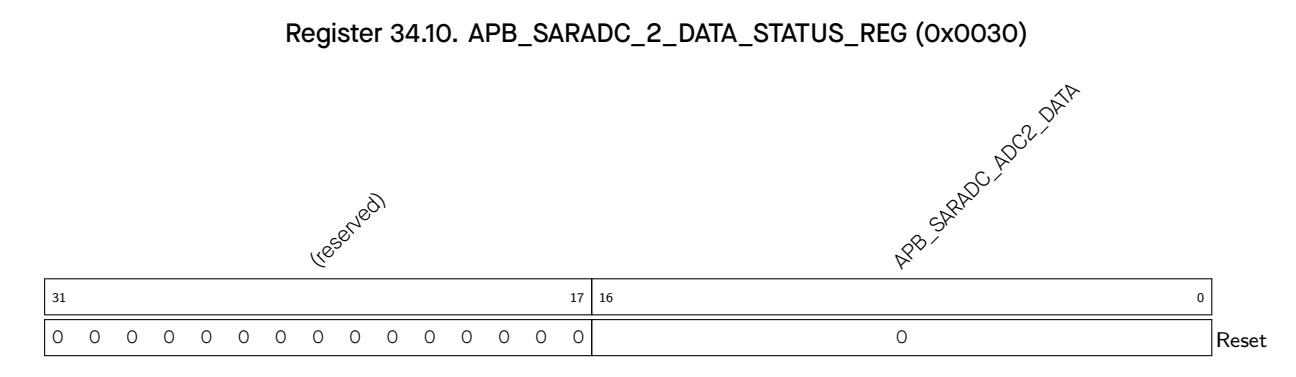

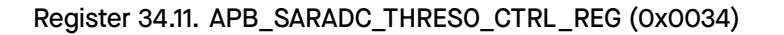

| 34.2 | SAR ADCs | 868 |

| 34.2.1 Overview | 868 | |

| 34.2.2 Features | 868 | |

| 34.2.3 Functional Description | 869 | |

|

34.2.3.1

Input Signals |

870 | |

| 34.2.3.2 ADC Conversion and Attenuation | 870 | |

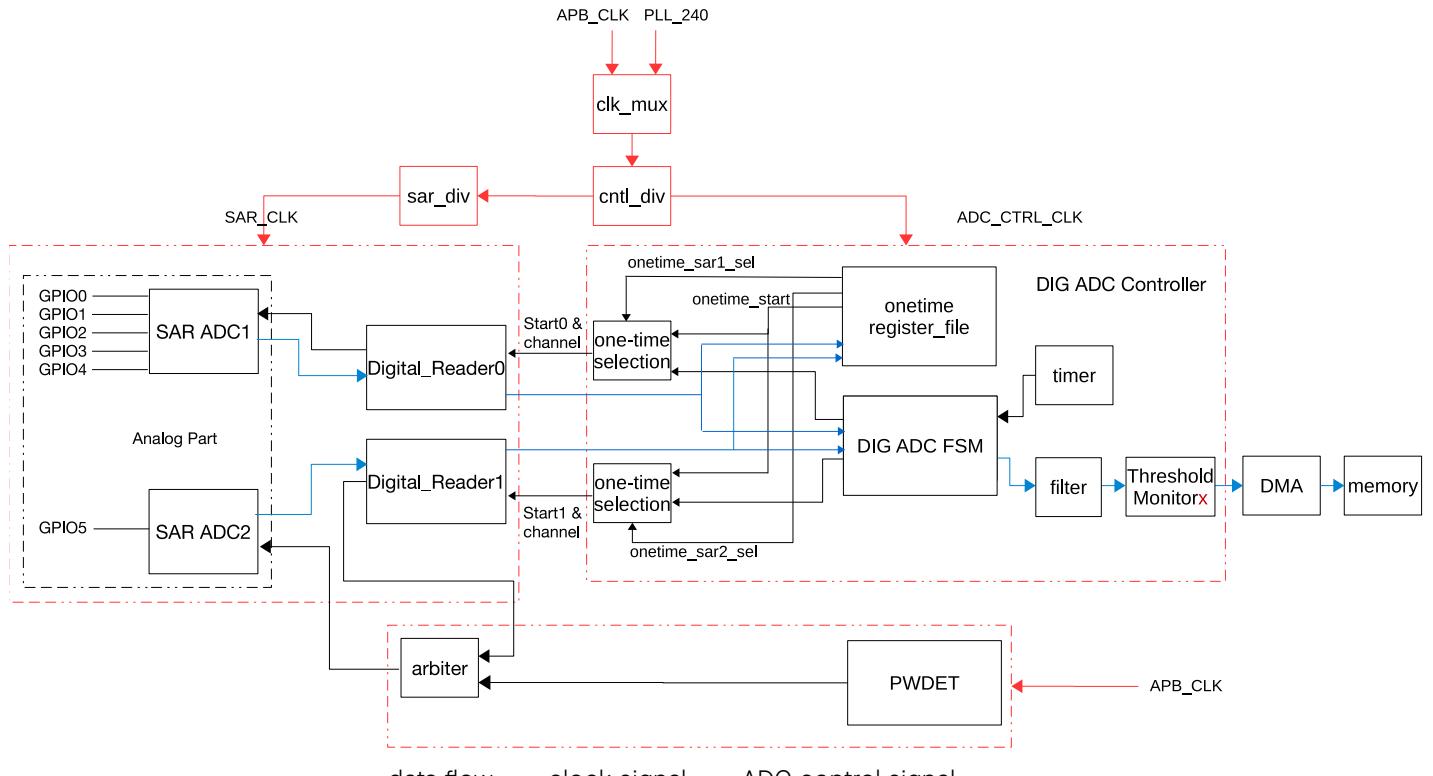

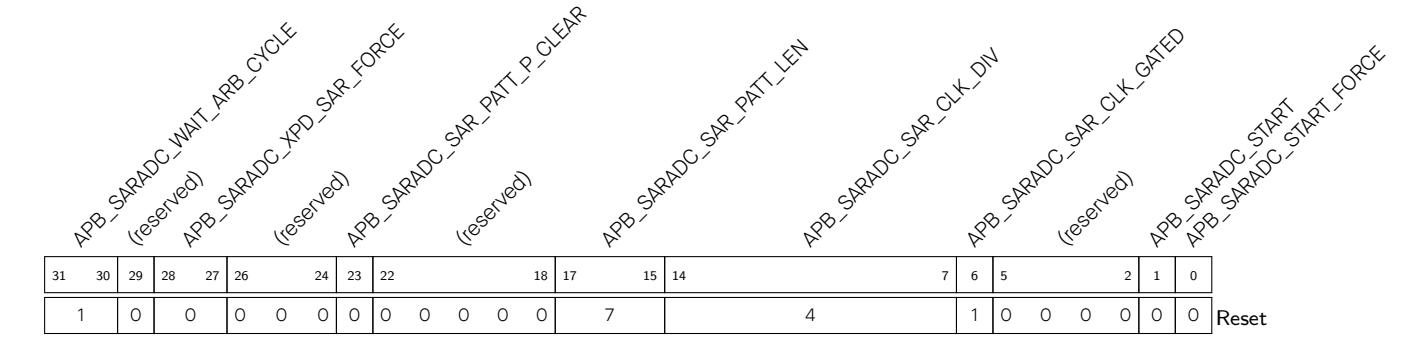

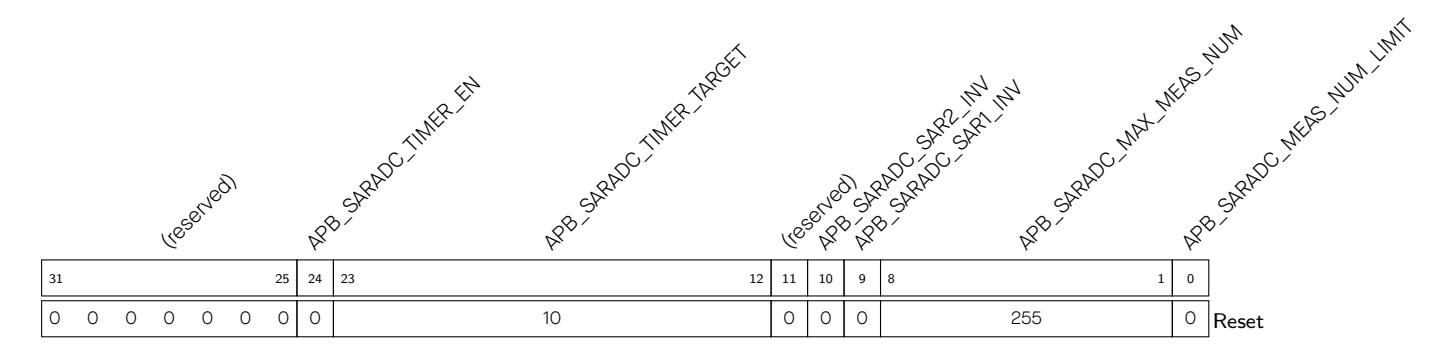

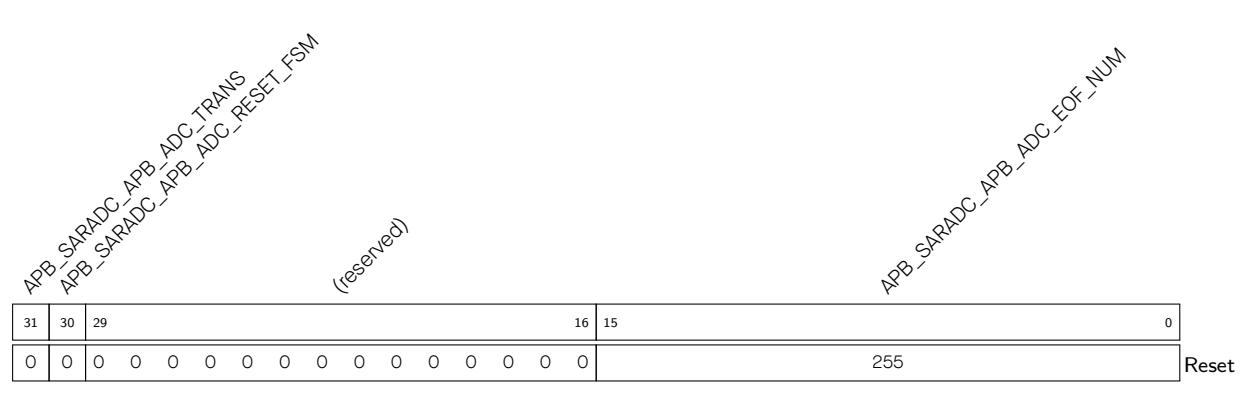

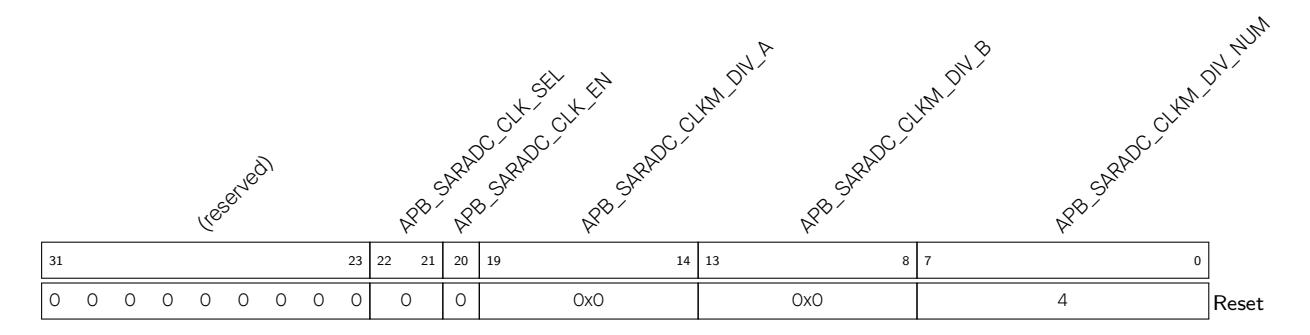

| 34.2.3.3 DIG ADC Controller | 870 | |

| 34.2.3.4 DIG ADC Clock | 871 | |

| 34.2.3.5 DMA Support | 872 | |

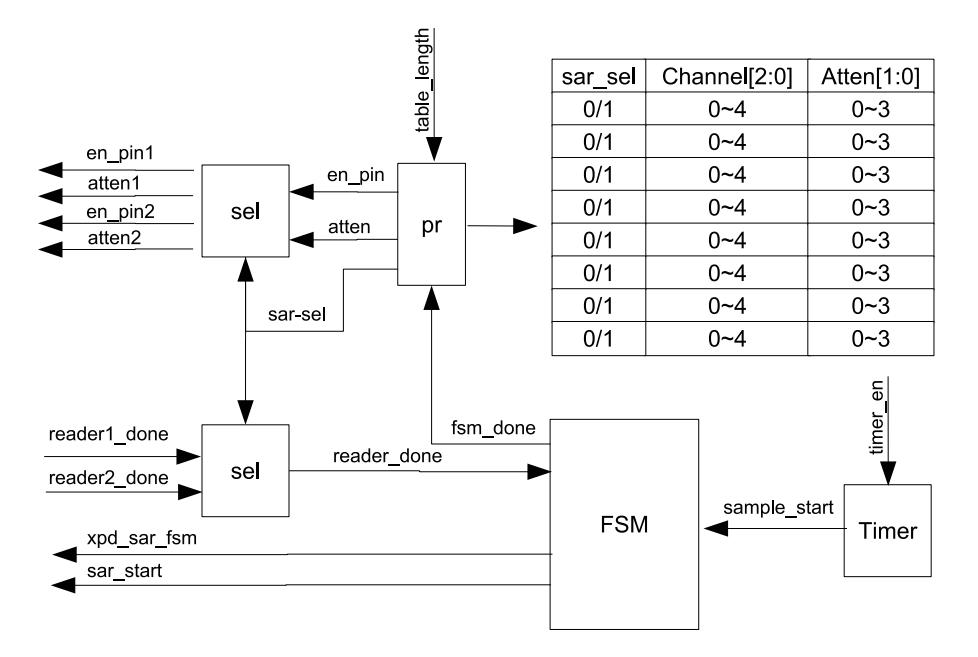

| 34.2.3.6 DIG ADC FSM | 872 | |

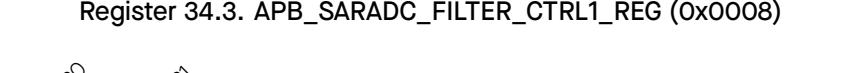

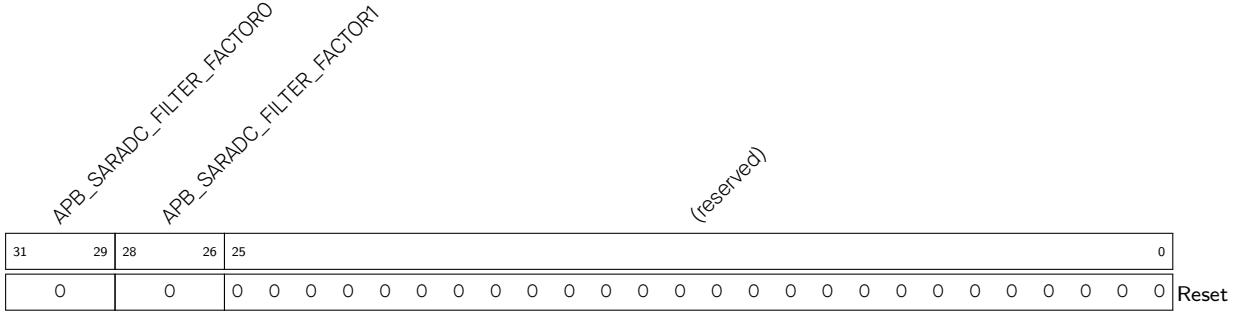

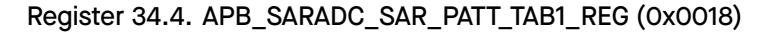

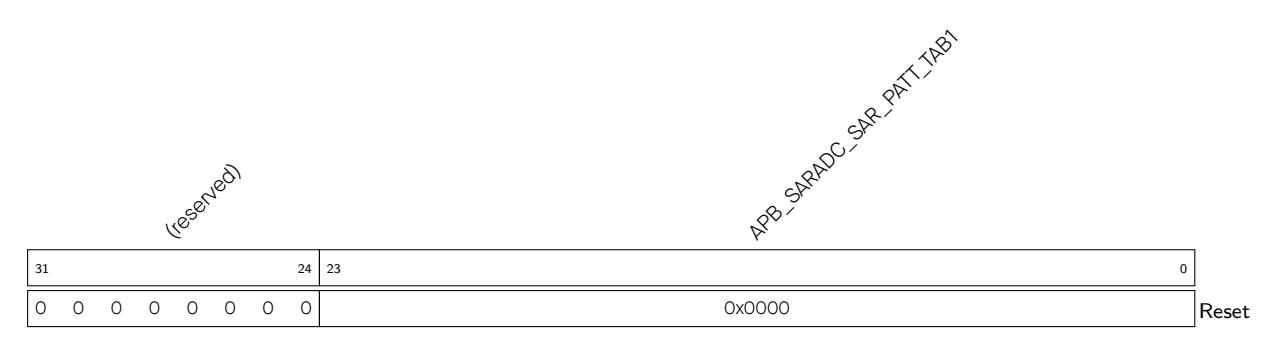

| 34.2.3.7 ADC Filters | 875 | |

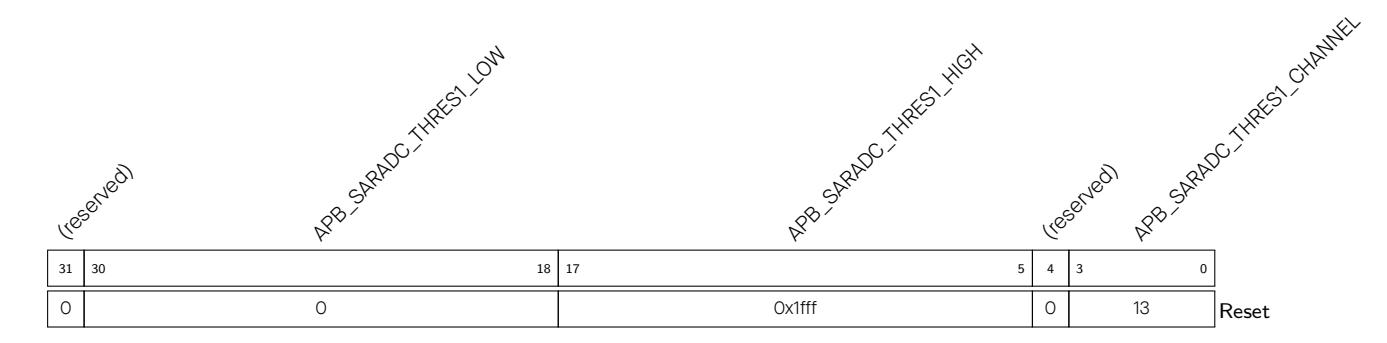

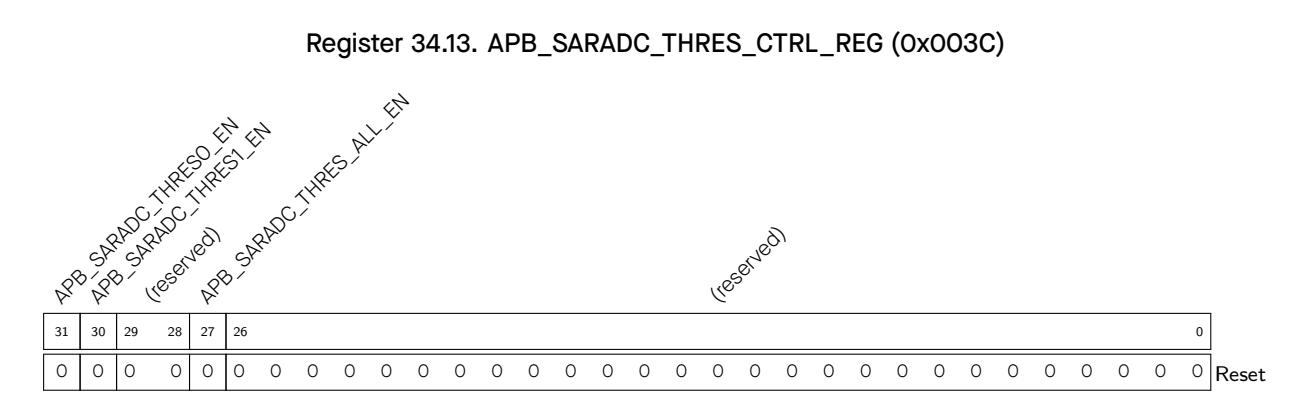

| 34.2.3.8 Threshold Monitoring | 875 | |

| 34.2.3.9 SAR ADC2 Arbiter | 875 | |

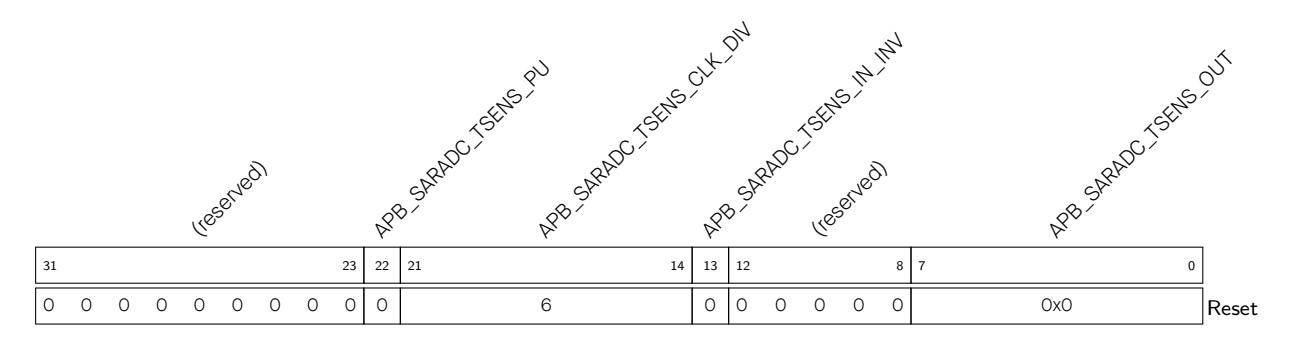

| 34.3 | Temperature Sensor | 876 |

| 34.3.1 Overview | 876 | |

| 34.3.2 Features | 876 | |

| 34.3.3 Functional Description | 876 | |

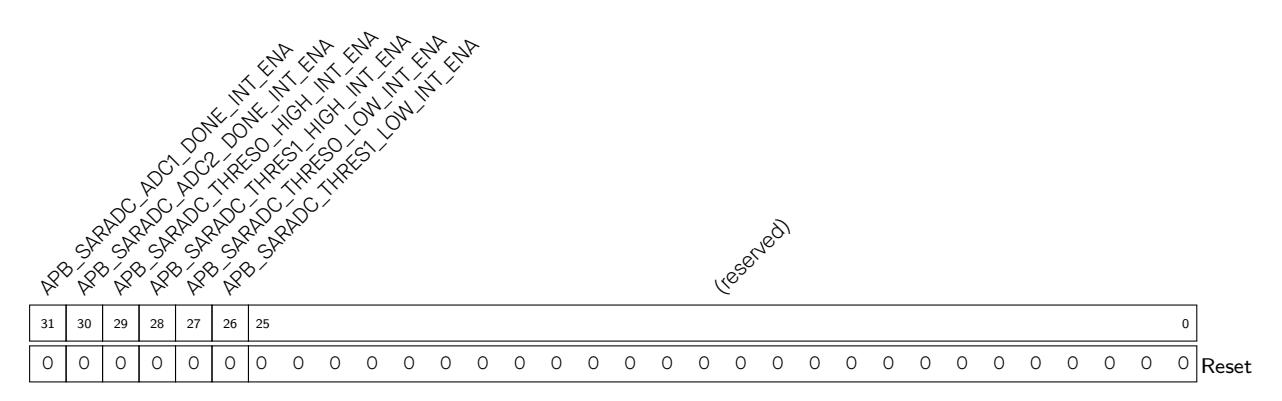

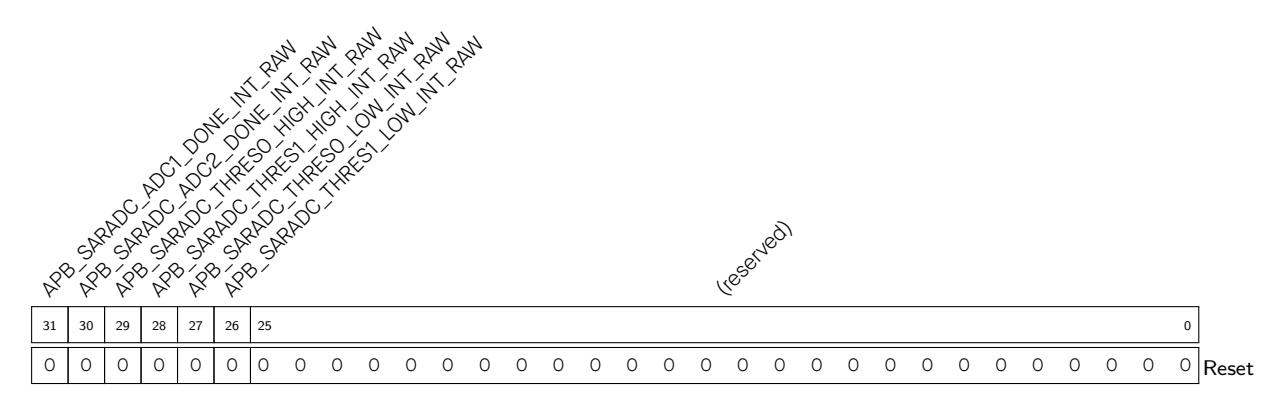

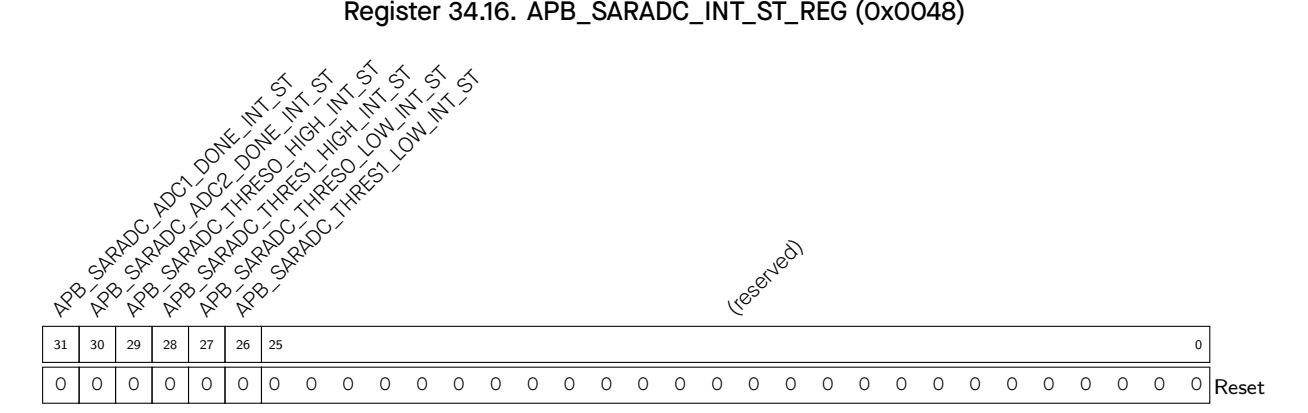

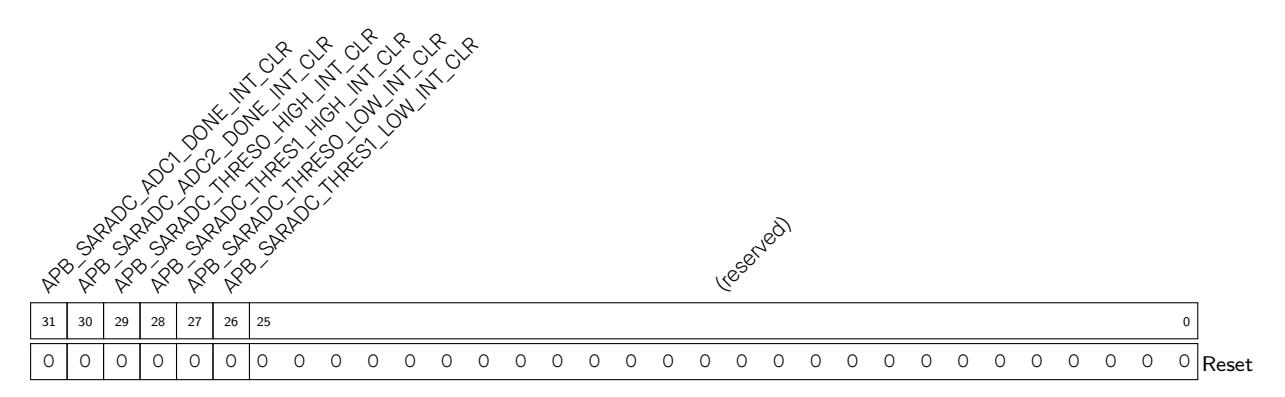

| 34.4 | Interrupts | 877 |

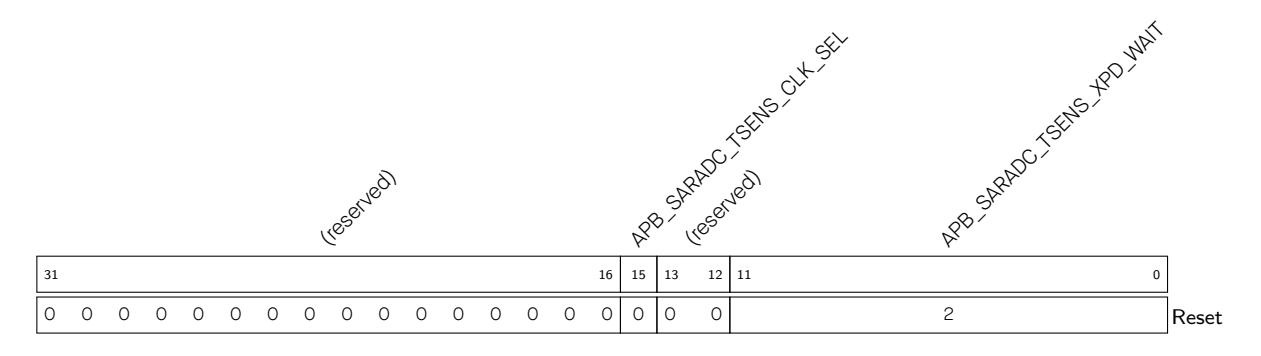

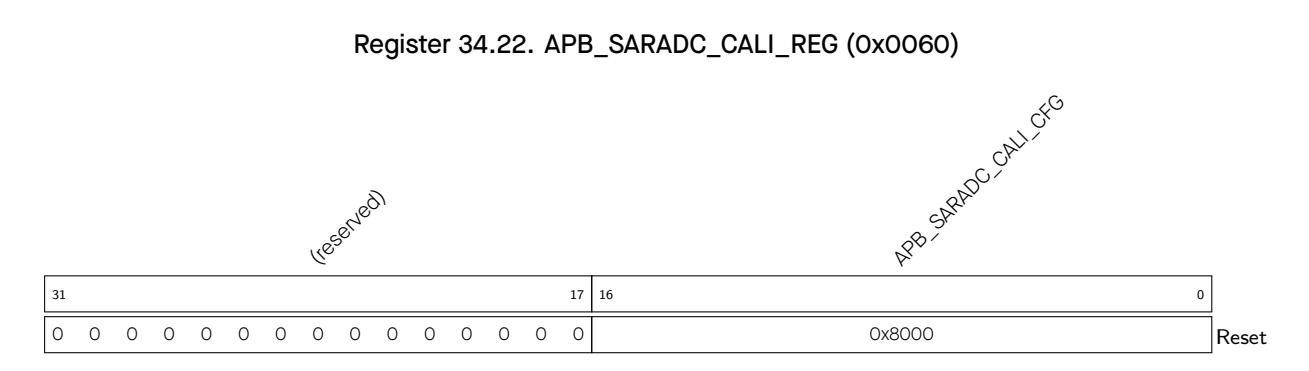

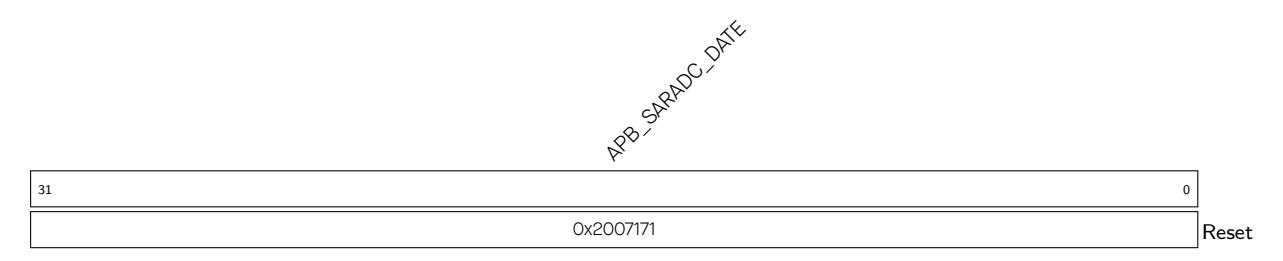

|

34.5

34.6 |

Register Summary

Register |

877

878 |

| GoBack | |

|---|---|

| Contents | |

|

VII

Appendix Related Documentation and Resources Glossary |

890

891 892 |

|

Abbreviations for Peripherals

Abbreviations Related to Registers Access Types for Registers Programming Reserved Register Field |

892

892 892 895 |

|

Introduction

Programming Reserved Register Field |

895

895 |

| Interrupt Configuration Registers | 896 |

| List of Tables | ||

|

1.3-1

1.5-1 |

CPU Address Map

ID wise map of Interrupt Trap-Vector Addresses |

|

| 1.7-1 | NAPOT encoding for maddress | |

| 2.4-1 | Selecting Peripherals via Register Configuration | |

| 2.4-2 | Descriptor Field Alignment Requirements | |

| 3.3-1 | Internal Memory Address Mapping | |

| 3.3-2 | External Memory Address Mapping | |

| 3.3-3 | Module/Peripheral Address Mapping | |

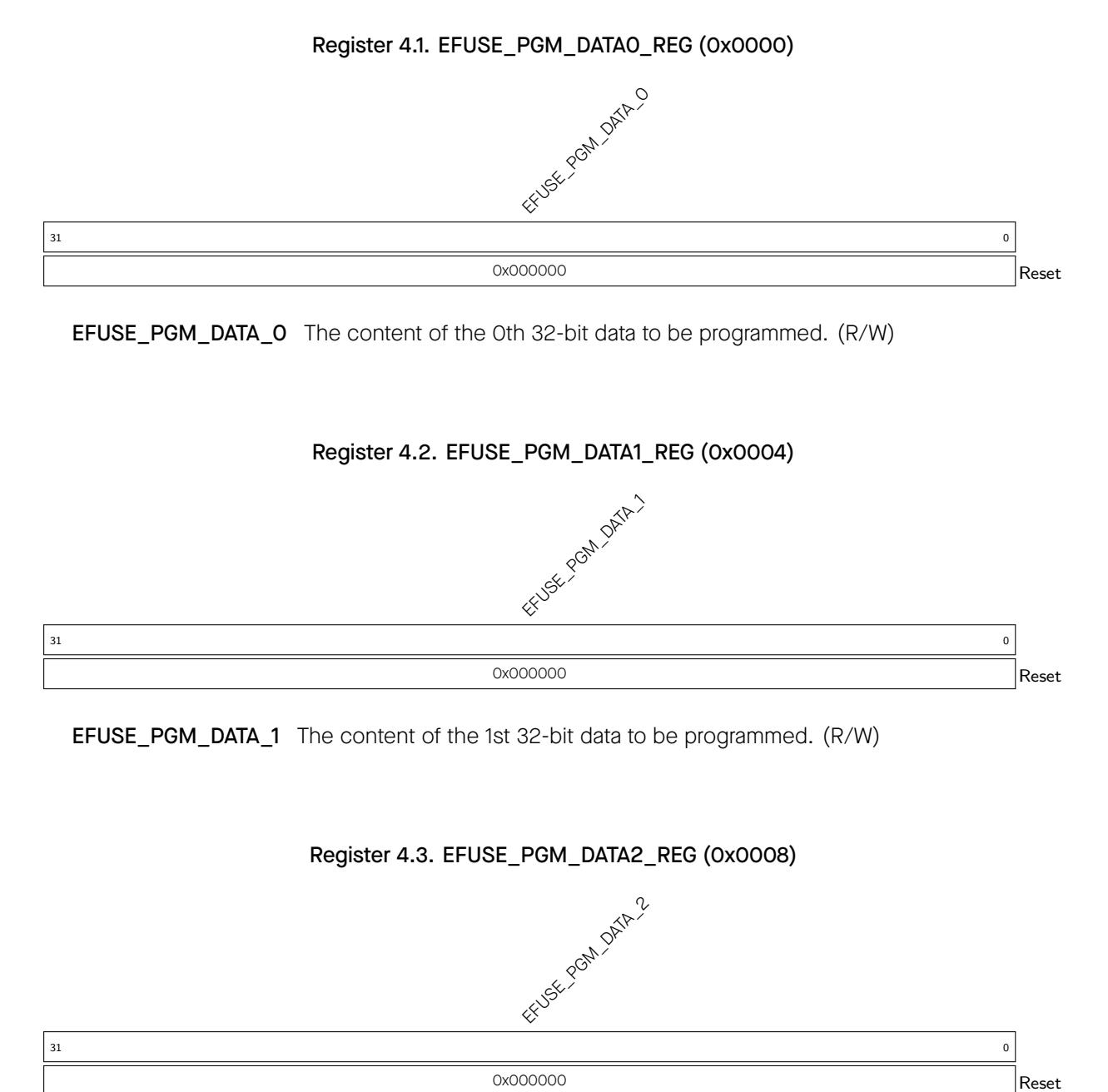

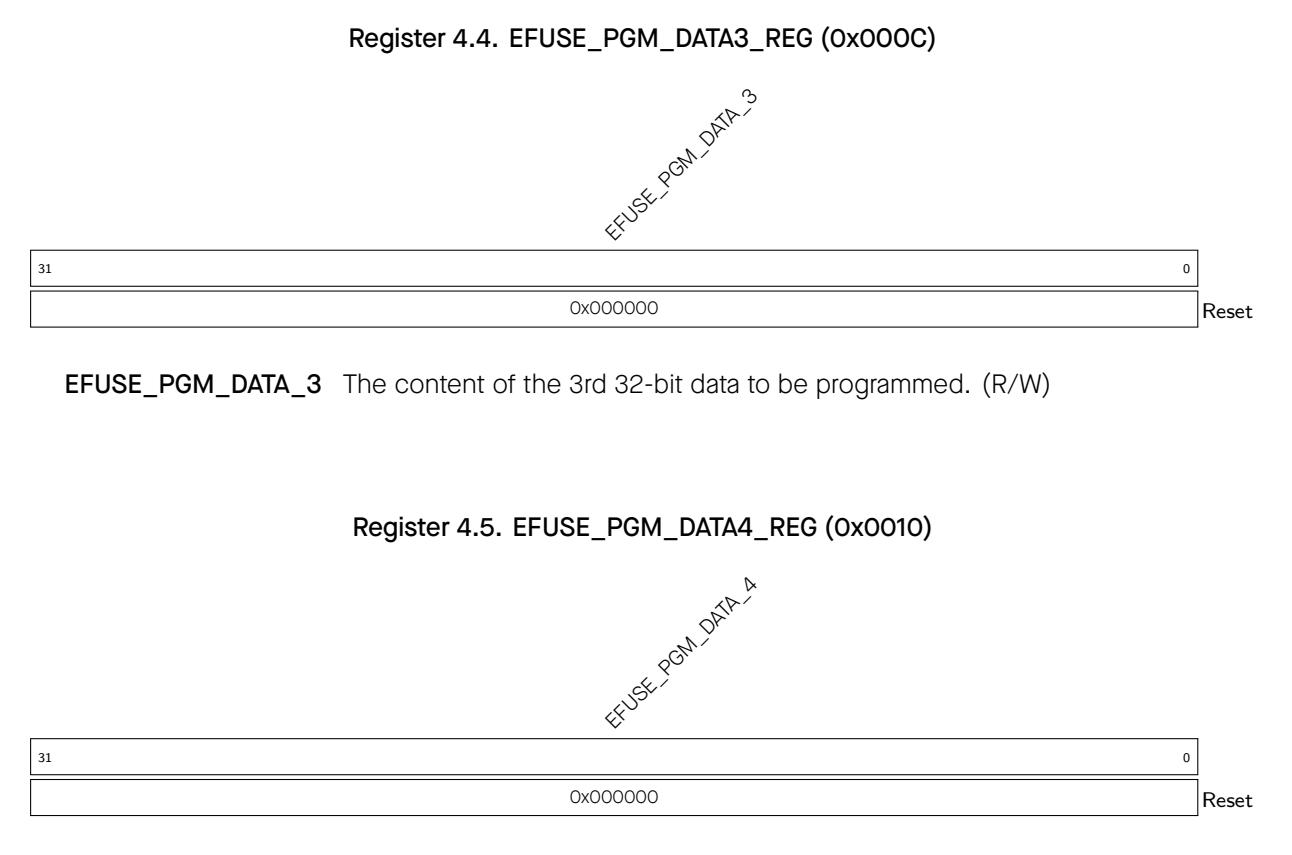

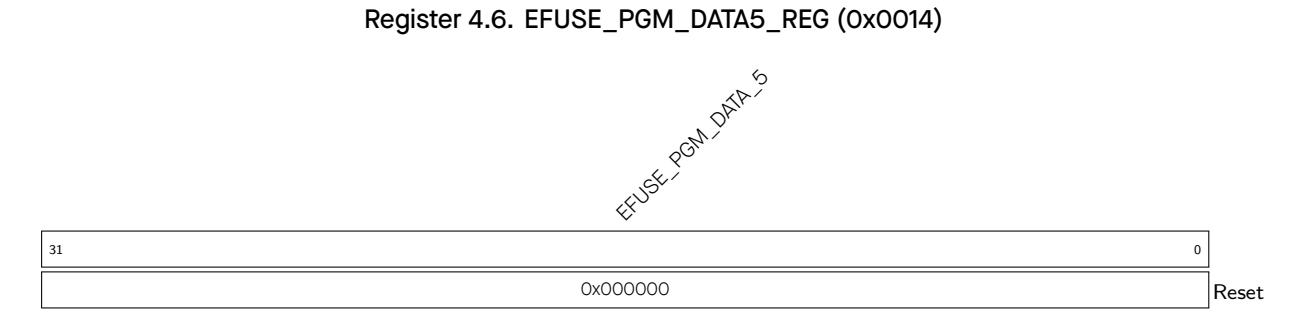

| 4.3-1 | Parameters in eFuse BLOCK0 | 101 |

| 4.3-2 | Secure Key Purpose Values | 104 |

| 4.3-3 | Parameters in BLOCK1 to BLOCK10 | 105 |

|

4.3-4

4.3-5 |

Registers Information

Configuration of Default VDDQ Timing Parameters |

109 |

| 5.8-1 | Bits Used to Control IO MUX Functions in Light-sleep Mode | 167 |

| 5.11-1 | Peripheral Signals via GPIO Matrix | 169 |

|

5.12-1

5.12-2 |

IO MUX Pin Functions

Power-Up Glitches on Pins |

174

175 |

| 5.13-1 | Analog Functions of IO MUX Pins | 175 |

| 6.1-1 | Reset Sources | 193 |

| 6.2-1 | CPU Clock Source | 195 |

| 6.2-2 | CPU Clock Frequency | 195 |

|

6.2-3

6.2-4 |

Peripheral Clocks

APB_CLK Clock Frequency |

196

197 |

| 6.2-5 | CRYPTO_CLK Frequency | 197 |

| 7.1-1 | Default Configuration of Strapping Pins | 198 |

| 7.2-1 | Boot Mode Control | 199 |

| 7.3-1 | ROM Message Printing Control | 200 |

| 8.3-1 | CPU Peripheral Interrupt Configuration/Status Registers and Peripheral Interrupt Sources | 204 |

| 9.3-1 | Low-power Clocks | 223 |

| 9.3-2 | The Triggering Conditions for the RTC Timer | 223 |

|

9.4-1

9.4-2 |

Predefined Power Modes

Wakeup Source |

227

228 |

| 10.4-1 | UNITn Configuration Bits | 272 |

|

10.4-2

10.4-3 |

Trigger Point

Synchronization Operation |

273

273 |

| 11.2-1 | Alarm Generation When Up-Down Counter Increments | 290 |

| 11.2-2 | Alarm Generation When Up-Down Counter Decrements | 290 |

| List of Tables | GoBack | |

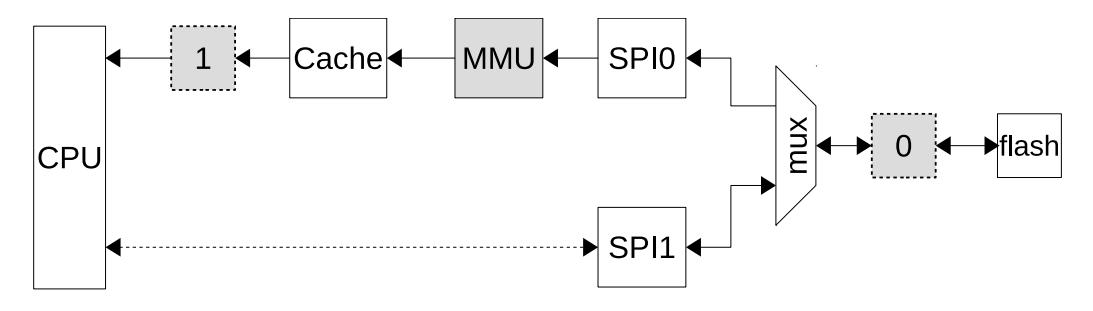

| 14.4-1 | ROM Address | 317 |

| 14.4-2 | Access Configuration to ROM (ROM0 and ROM1) | 318 |

| 14.4-3 | SRAM Address | 318 |

| 14.4-4 | Access Configuration to Internal SRAM0 | 319 |

| 14.4-5 | Internal SRAM1 Split Regions | 320 |

| 14.4-6 | Access Configuration to the Instruction Region of Internal SRAM1 | 322 |

| 14.4-7 | Access Configuration to the Data Region of Internal SRAM1 | 322 |

| 14.4-8 | RTC FAST Memory Address | 322 |

| 14.4-9 | Split RTC FAST Memory into the Higher Region and the Lower Region | 323 |

|

14.4-10

14.5-1 |

Access Configuration to the RTC FAST Memory

Access Configuration of the Peripherals |

323

324 |

| 14.5-2 | Access Configuration of Peri Regions | 325 |

| 14.6-1 | Split the External Memory into Split Regions | 326 |

| 14.6-2 | Access Configuration of Flash Regions | 326 |

| 14.6-3 | Cache Virtual Address Region | 327 |

| 14.6-4 | Split IBUS Cache Virtual Address into 4 Regions | 327 |

| 14.6-5 | Split DBUS Cache Virtual Address into 4 Regions | 327 |

| 14.6-6 | Access Configuration of IBUS to Split Regions | 328 |

| 14.6-7 | Access Configuration of DBUS to Split Regions | 328 |

| 14.7-1 | Interrupt Registers for Unauthorized IBUS Access | 329 |

| 14.7-2 | Interrupt Registers for Unauthorized DBUS Access | 329 |

| 14.7-3 | Interrupt Registers for Unauthorized Access to External Memory | 330 |

| 14.7-4 | Interrupt Registers for Unauthorized Access to Internal Memory via GDMA | 330 |

| 14.7-5 | Interrupt Registers for Unauthorized PIF Access | 331 |

|

14.7-6

14.7-7 |

All Possible Access Alignment and their Results

Interrupt Registers for Unauthorized Access Alignment |

331

332 |

| 14.8-1 | Lock Registers and Related Permission Control Registers | 332 |

| 16.3-1 | Memory Controlling Bit | 428 |

| 16.3-2 | Clock Gating and Reset Bits | 430 |

| 17.4-1 | CPU Packet Format | 450 |

| 17.4-2 | DMA Packet Format | 450 |

| 17.4-3 | DMA Source | 450 |

| 17.4-4 | Written Data Format | 451 |

| 18.3-1 | AES Accelerator Working Mode | 474 |

| 18.3-2 | Key Length and Encryption/Decryption | 474 |

| 18.4-1 | Working Status under Typical AES Working Mode | 475 |

| 18.4-2 | Text Endianness Type for Typical AES | 475 |

| 18.4-3 | Key Endianness Type for AES-128 Encryption and Decryption | 476 |

| 18.4-4 | Key Endianness Type for AES-256 Encryption and Decryption | 476 |

| 18.5-1 | Block Cipher Mode | 477 |

|

18.5-2

18.5-3 |

Working Status under DMA-AES Working mode

TEXT-PADDING |

478

478 |

| List of Tables | GoBack | |

| 19.2-1 | HMAC Purposes and Configuration Value | 488 |

| 20.3-1 | Acceleration Performance | 506 |

| 20.4-1 | RSA Accelerator Memory Blocks | 507 |

|

21.3-1

21.3-2 |

SHA Accelerator Working Mode

SHA Hash Algorithm Selection |

513

514 |

| 21.4-1 | The Storage and Length of Message Digest from Different Algorithms | 518 |

| 23.4-1 | Key generated based on KeyA | 536 |

| 23.4-2 | Mapping Between Offsets and Registers | 537 |

| 26.5-1 | UARTn Synchronous Registers | 563 |

| 26.5-2 | UARTn Static Registers | 564 |

| 27.5-1 | Data Modes Supported by GP-SPI2 | 611 |

| 27.5-2 | Mapping of FSPI Bus Signals | 611 |

| 27.5-3 | Functional Description of FSPI Bus Signals | 611 |

| 27.5-4 | Signals Used in Various SPI Modes | 613 |

| 27.5-5 | Bit Order Control in GP-SPI2 Master and Slave Modes | 614 |

| 27.5-6 | Supported Transfers in Master and Slave Modes | 614 |

| 27.5-7 | Registers Used for State Control in 1/2/4-bit Modes | 623 |

| 27.5-7 | Registers Used for State Control in 1/2/4-bit Modes | 624 |

| 27.5-8 | GP-SPI2 Master BM Table for CONF State | 631 |

| 27.5-9 | An Example of CONF bufferi in Segmenti | 632 |

| 27.5-10 | BM Bit Value v.s. Register to Be Updated in This Example | 632 |

| 27.5-11 | Supported CMD Values in SPI Mode | 635 |

| 27.5-11 | Supported CMD Values in SPI Mode | 636 |

| 27.5-12 | Supported CMD Values in QPI Mode | 636 |

| 27.7-1 | Clock Phase and Polarity Configuration in Master Mode | 642 |

| 27.7-2 | Clock Phase and Polarity Configuration in Slave Mode | 642 |

|

27.9-1

27.9-1 |

GP-SPI2 Master Mode Interrupts

GP-SPI2 Master Mode Interrupts |

645

646 |

| 27.9-2 | GP-SPI2 Slave Mode Interrupts | 646 |

| 28.4-1 | I2C Synchronous Registers | 681 |

| 29.4-1 | I2S Signal Description | 733 |

| 29.9-1 | Bit Width of Channel Valid Data | 740 |

| 29.9-2 | Endian of Channel Valid Data | 740 |

| 29.9-3 | Data-Fetching Control in PDM TX Mode | 743 |

| 29.9-4 | I2S Channel Control in Normal PDM TX Mode | 744 |

| 29.9-5 | PCM-to-PDM TX Mode | 744 |

|

29.10-1

29.10-2 |

Channel Storage Data Width

Channel Storage Data Endian |

747

747 |

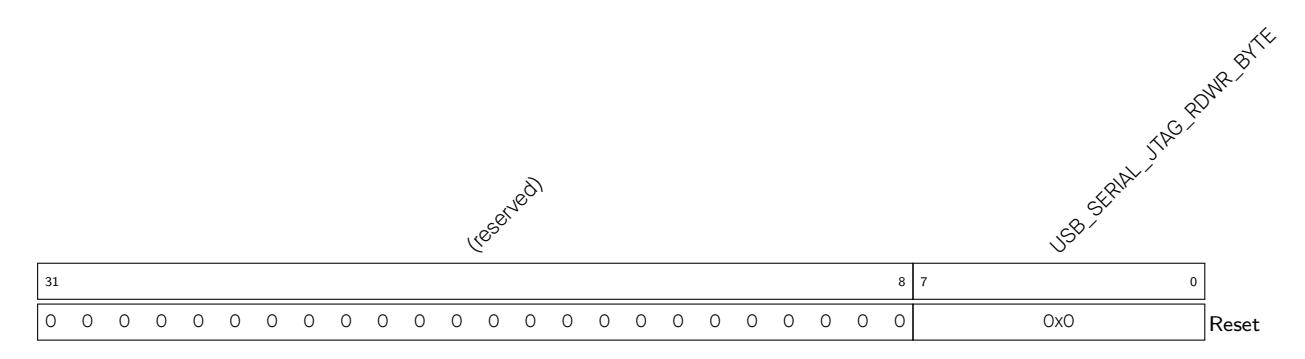

| 30.3-1 | Standard CDC-ACM Control Requests | 766 |

| 30.3-2 | CDC-ACM Settings with RTS and DTR | 766 |

| List of Tables | GoBack | |

| 30.3-4 | USB-to-JTAG Control Requests | 770 |

|

30.3-5

30.4-1 |

JTAG Capabilities Descriptor

Reset SoC into Download Mode |

770

771 |

| 30.4-2 | Reset SoC into Booting | 772 |

| 31.2-1 | Data Frames and Remote Frames in SFF and EFF | 791 |

| 31.2-2 | Error Frame | 793 |

| 31.2-3 | Overload Frame | 793 |

| 31.2-4 | Interframe Space | 794 |

|

31.2-5

31.4-1 |

Segments of a Nominal Bit Time

Bit Information of TWAI_BUS_TIMING_0_REG (0x18) |

797

801 |

| 31.4-2 | Bit Information of TWAI_BUS_TIMING_1_REG (0x1c) | 801 |

| 31.4-3 | Buffer Layout for Standard Frame Format and Extended Frame Format | 804 |

| 31.4-4 | TX/RX Frame Information (SFF/EFF); TWAI Address 0x40 | 805 |

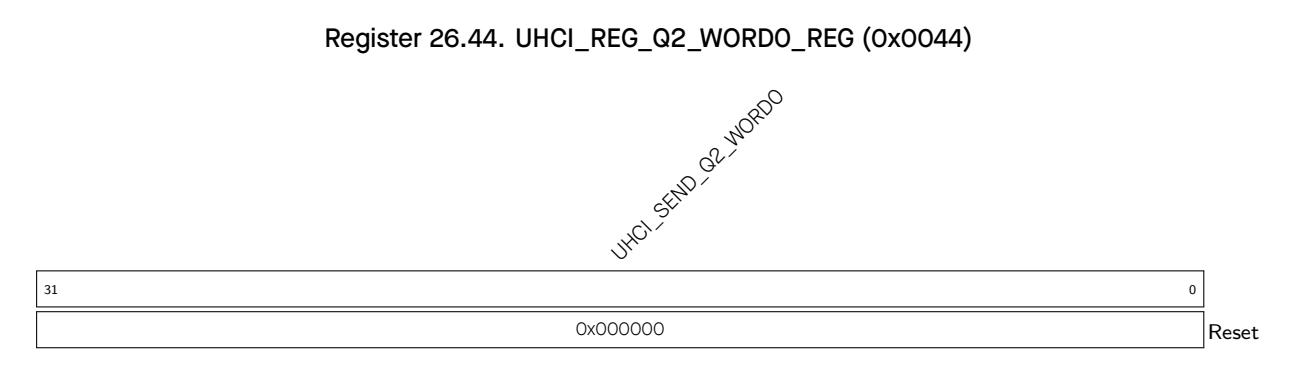

| 31.4-5 | TX/RX Identifier 1 (SFF); TWAI Address 0x44 | 805 |

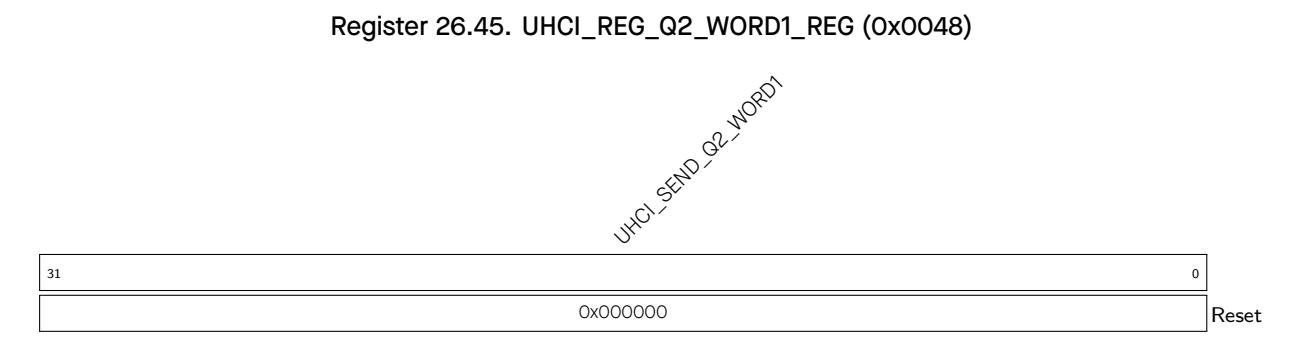

| 31.4-6 | TX/RX Identifier 2 (SFF); TWAI Address 0x48 | 805 |

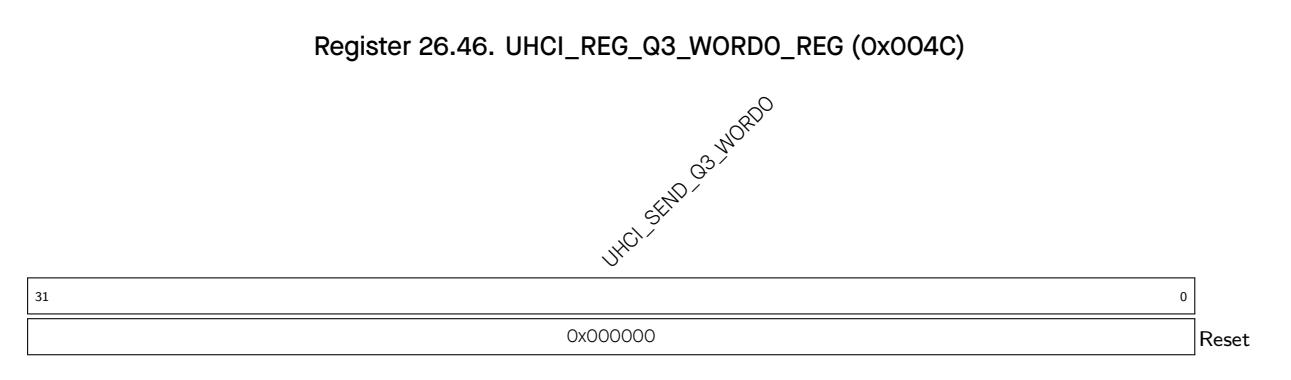

| 31.4-7 | TX/RX Identifier 1 (EFF); TWAI Address 0x44 | 806 |

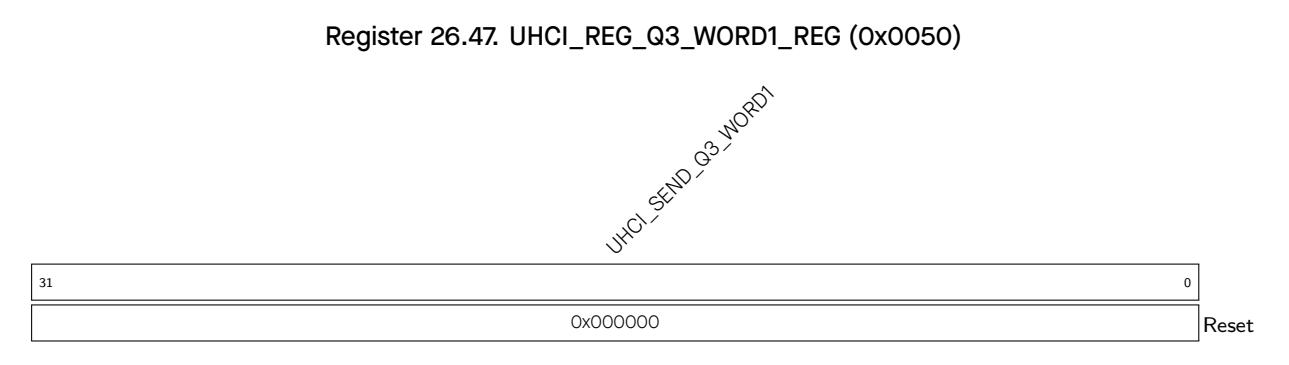

| 31.4-8 | TX/RX Identifier 2 (EFF); TWAI Address 0x48 | 806 |

| 31.4-9 | TX/RX Identifier 3 (EFF); TWAI Address 0x4c | 806 |

| 31.4-10 | TX/RX Identifier 4 (EFF); TWAI Address 0x50 | 806 |

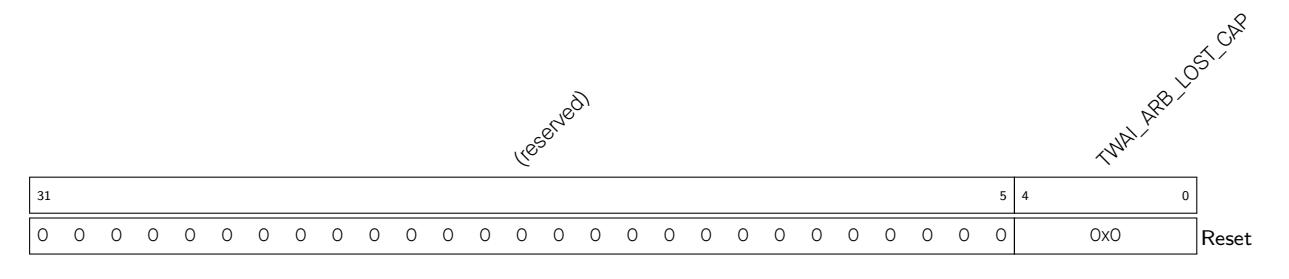

| 31.4-11 | Bit Information of TWAI_ERR_CODE_CAP_REG (0x30) | 811 |

|

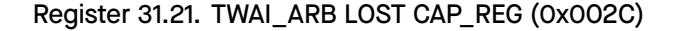

31.4-12

31.4-13 |

Bit Information of Bits SEG.4 - SEG.0

Bit Information of TWAI_ARB LOST CAP_REG (0x2c) |

811

812 |

| 32.3-1 | Commonly-used Frequencies and Resolutions | 830 |

| 32.3-1 | Commonly-used Frequencies and Resolutions | 831 |

| 33.3-1 | Configuration Update | 849 |

| 34.2-1 | SAR ADC Input Signals | 870 |

| 34.3-1 | Temperature Offset | 877 |

| CPU Block Diagram | 31 | |

|---|---|---|

| Debug System Overview | 47 | |

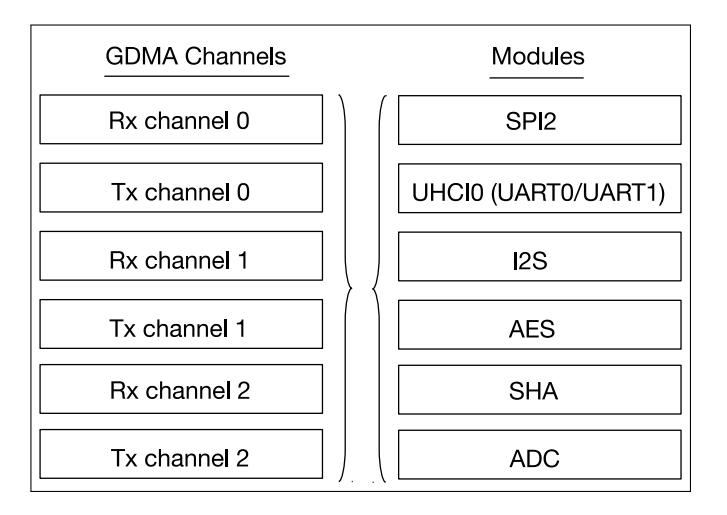

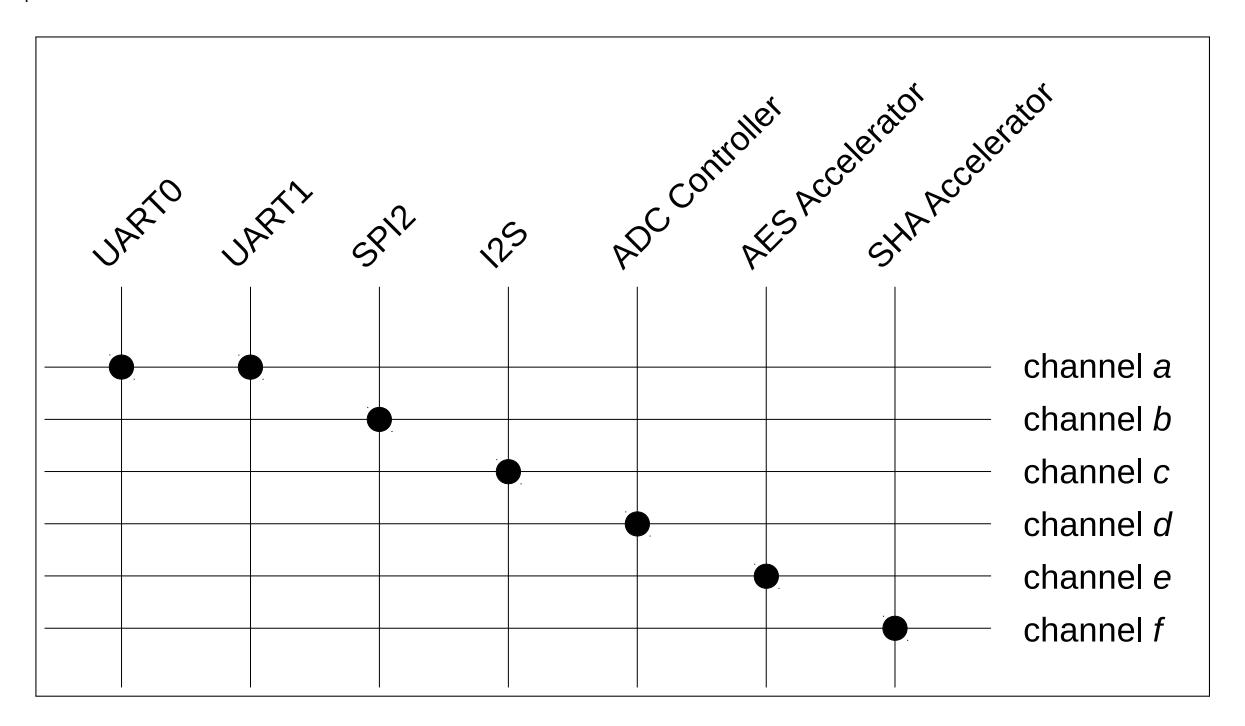

| Modules with GDMA Feature and GDMA Channels | 60 | |

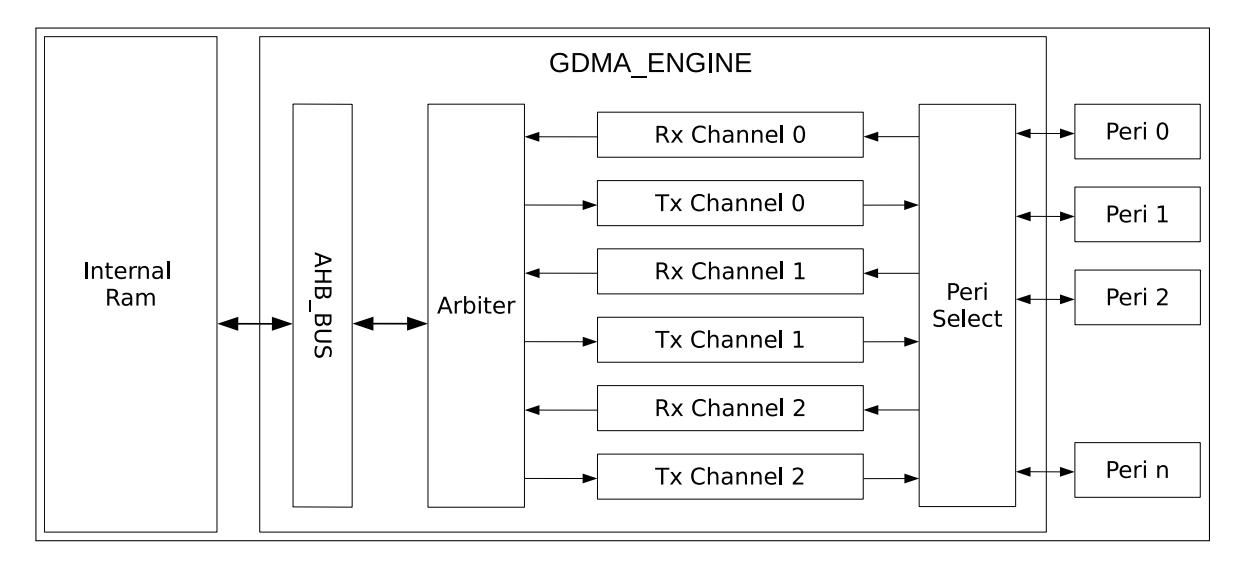

| GDMA Engine Architecture | 61 | |

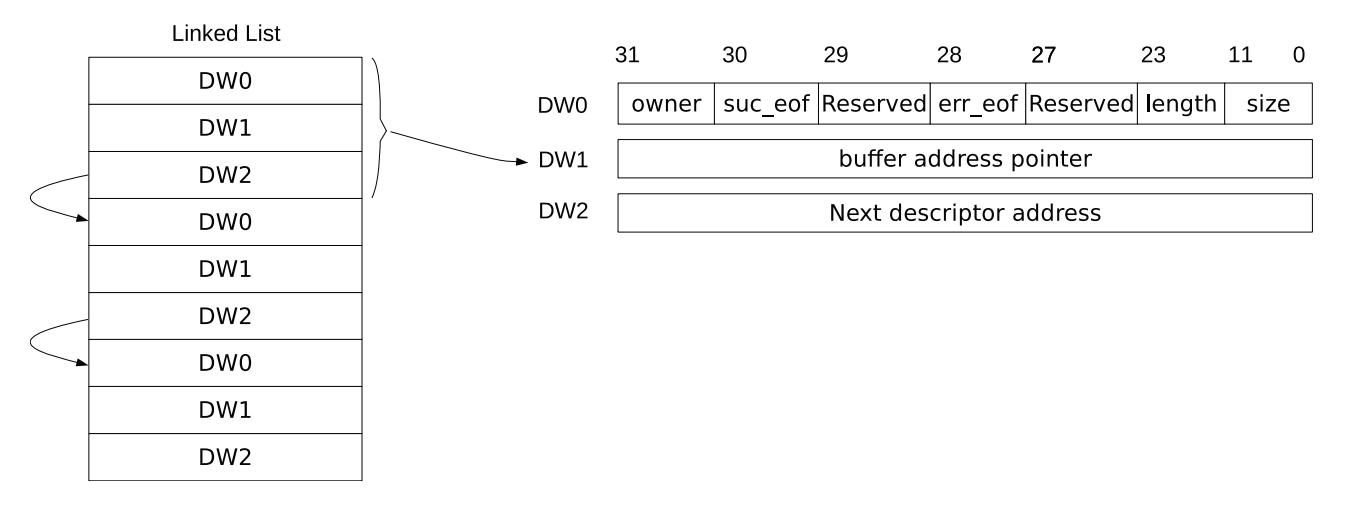

| Structure of a Linked List | 62 | |

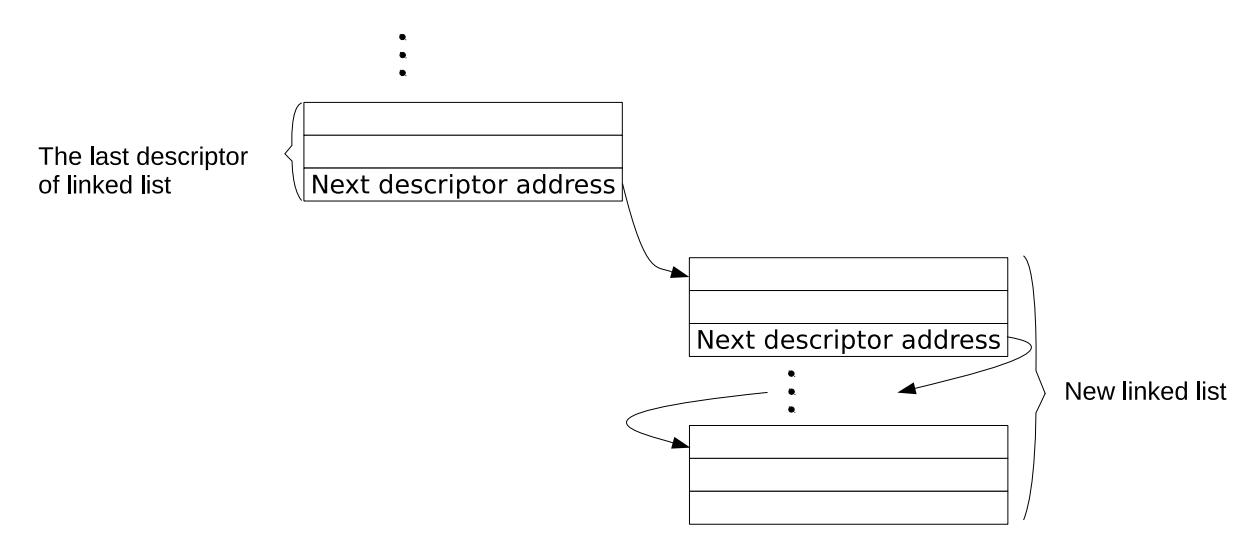

| Relationship among Linked Lists | 64 | |

|

|

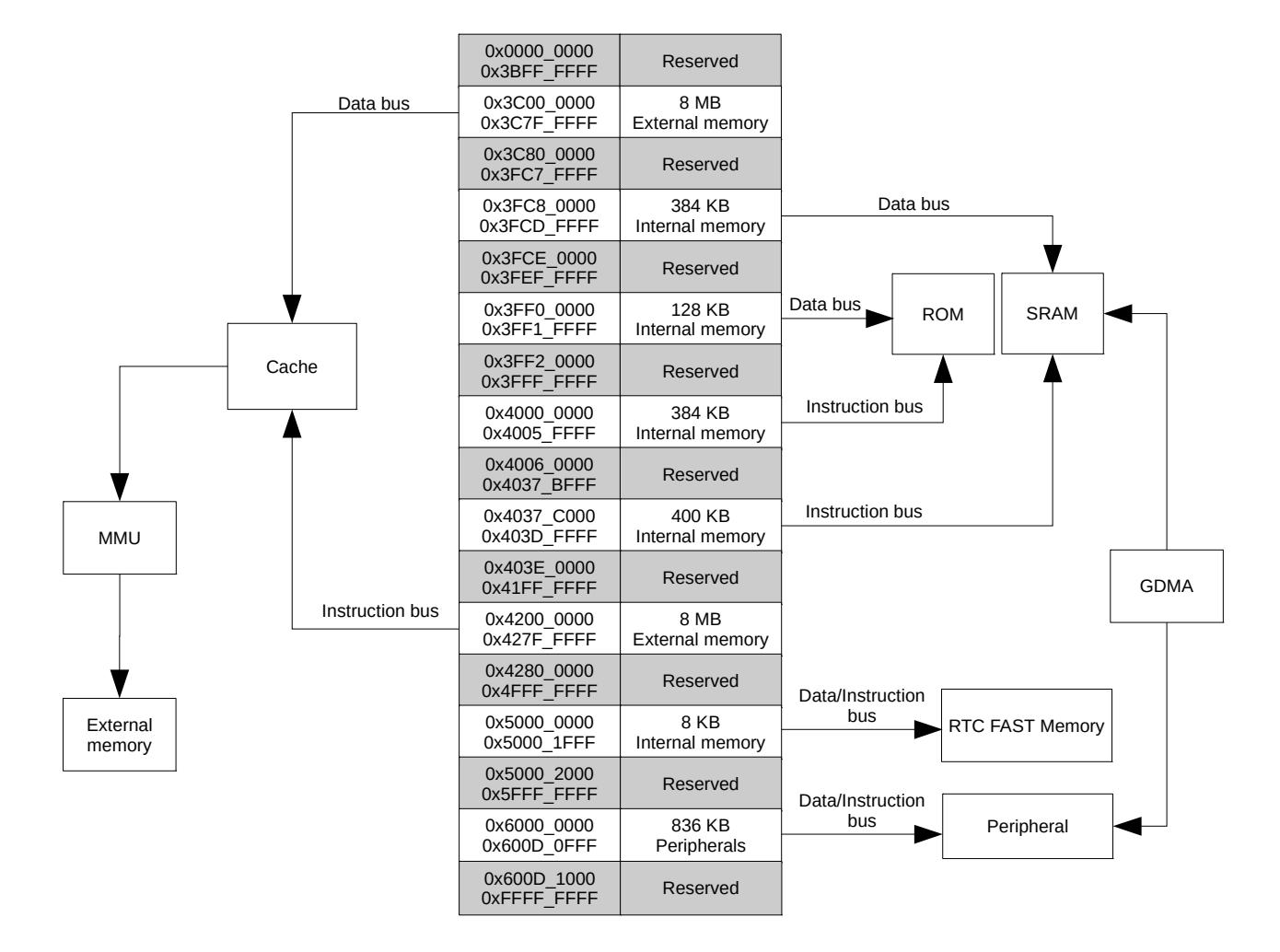

System Structure and Address Mapping

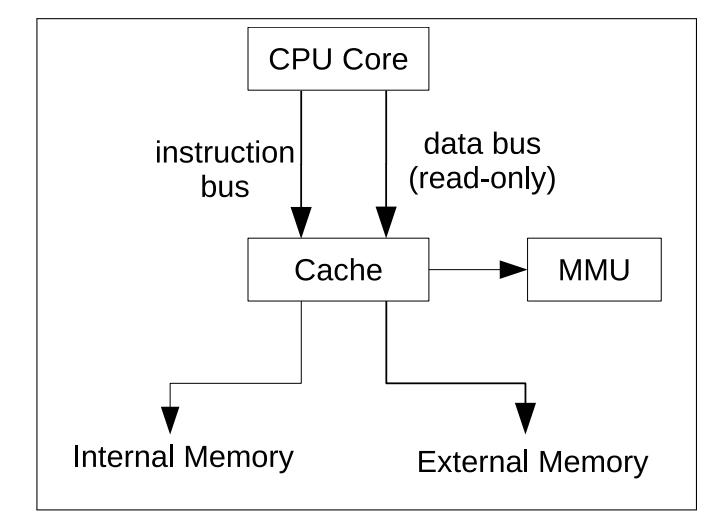

Cache Structure Peripherals/modules that can work with GDMA |

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! 97 107 |

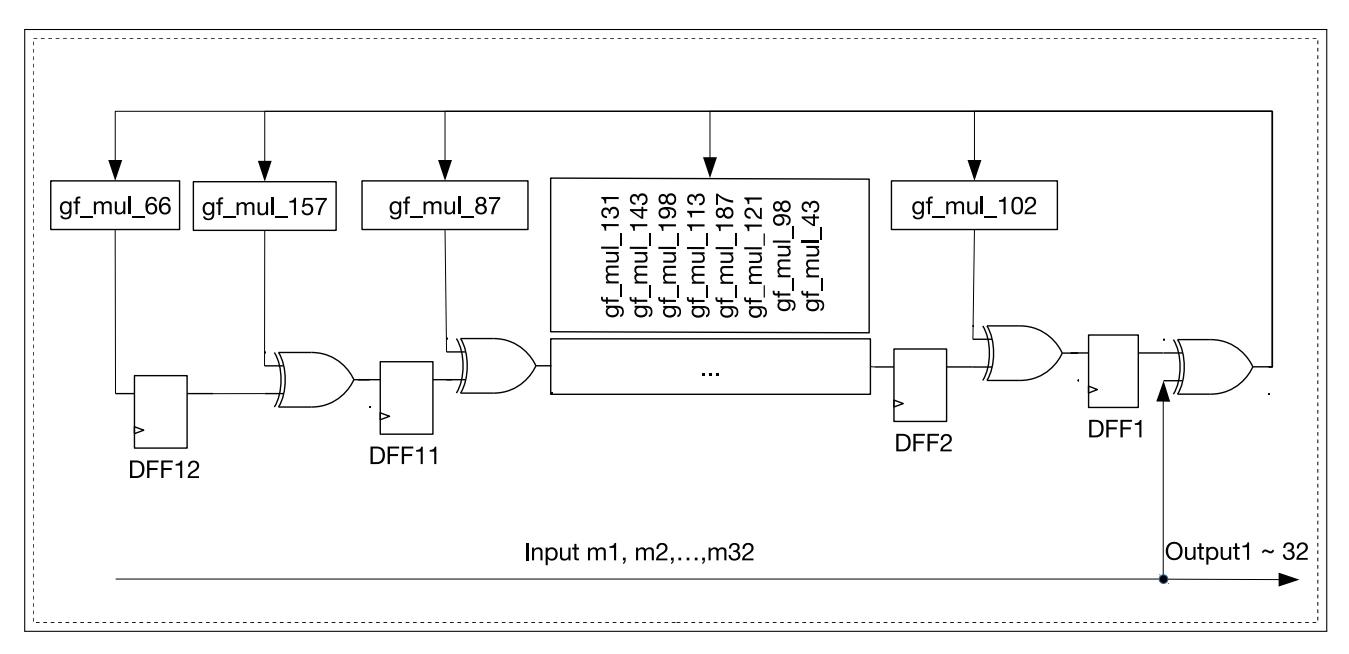

|

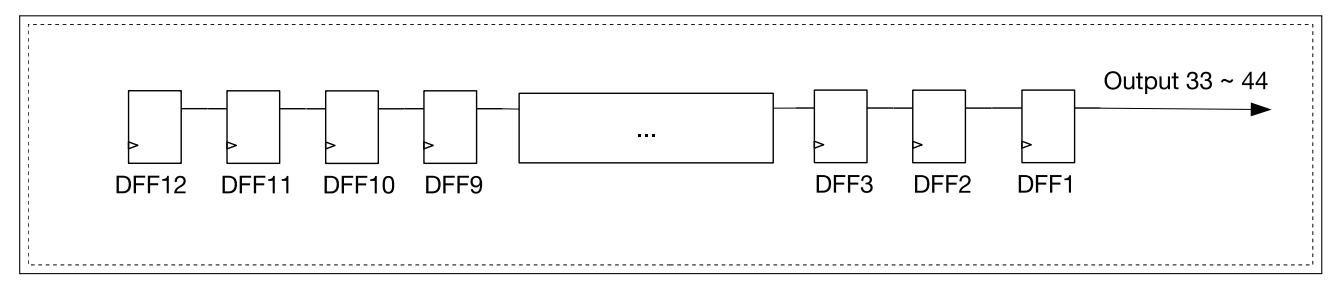

Shift Register Circuit (first 32 output)

Shift Register Circuit (last 12 output) |

107 | |

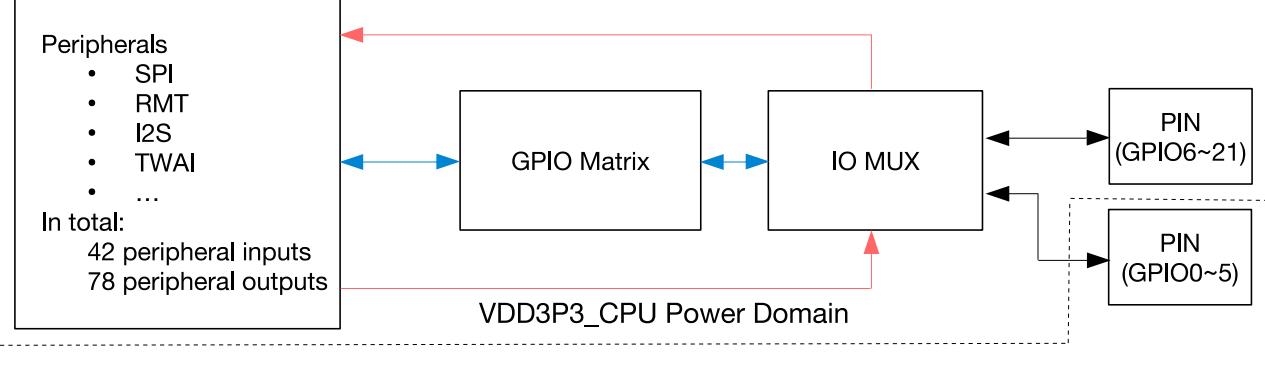

| Diagram of IO MUX and GPIO Matrix | 160 | |

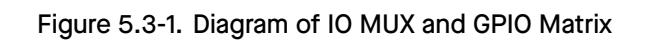

| Architecture of IO MUX and GPIO Matrix | 160 | |

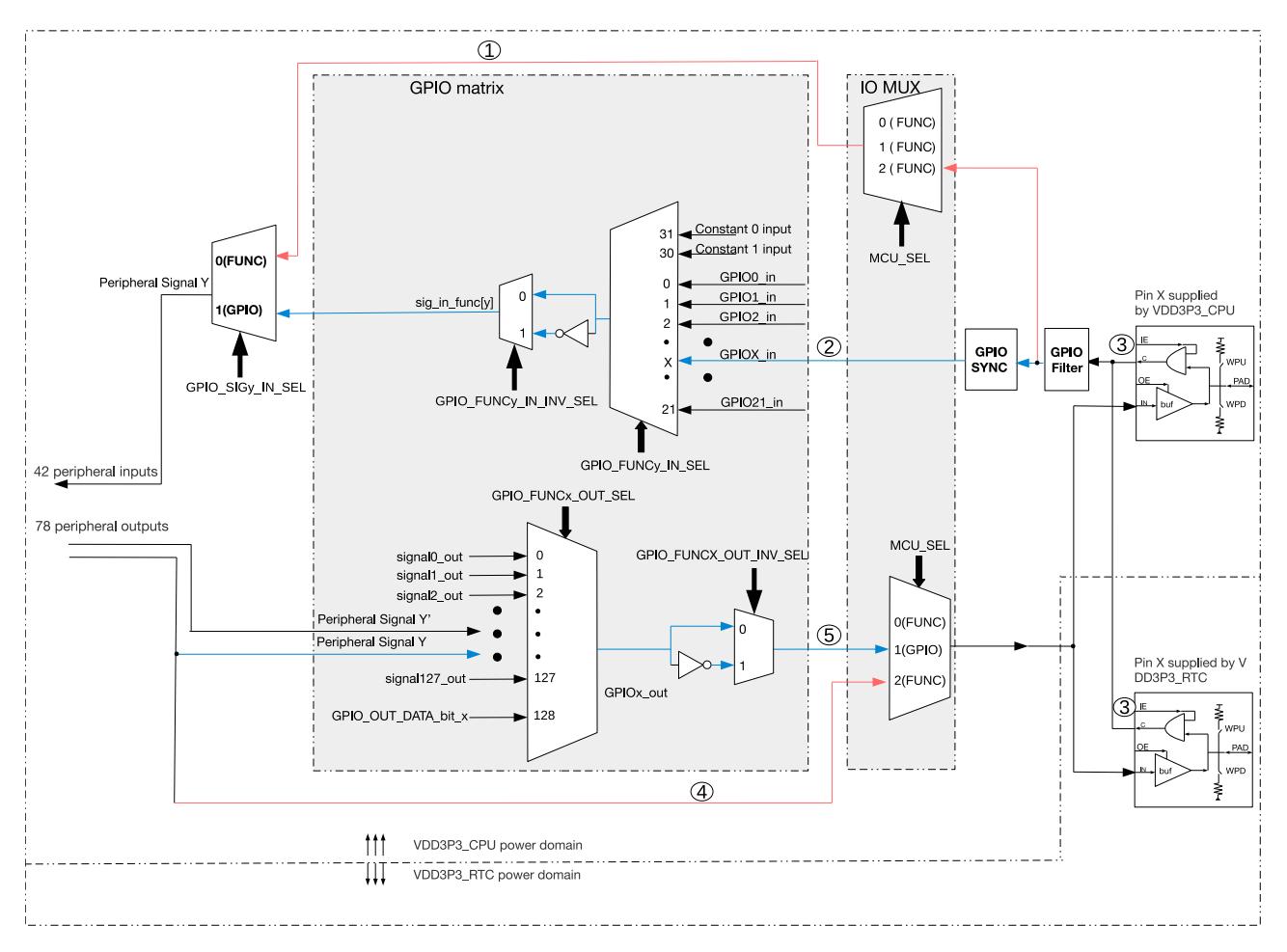

| Internal Structure of a Pad | 161 | |

| GPIO Input Synchronized on APB Clock Rising Edge or on Falling Edge | 162 | |

| Filter Timing of GPIO Input Signals | 162 | |

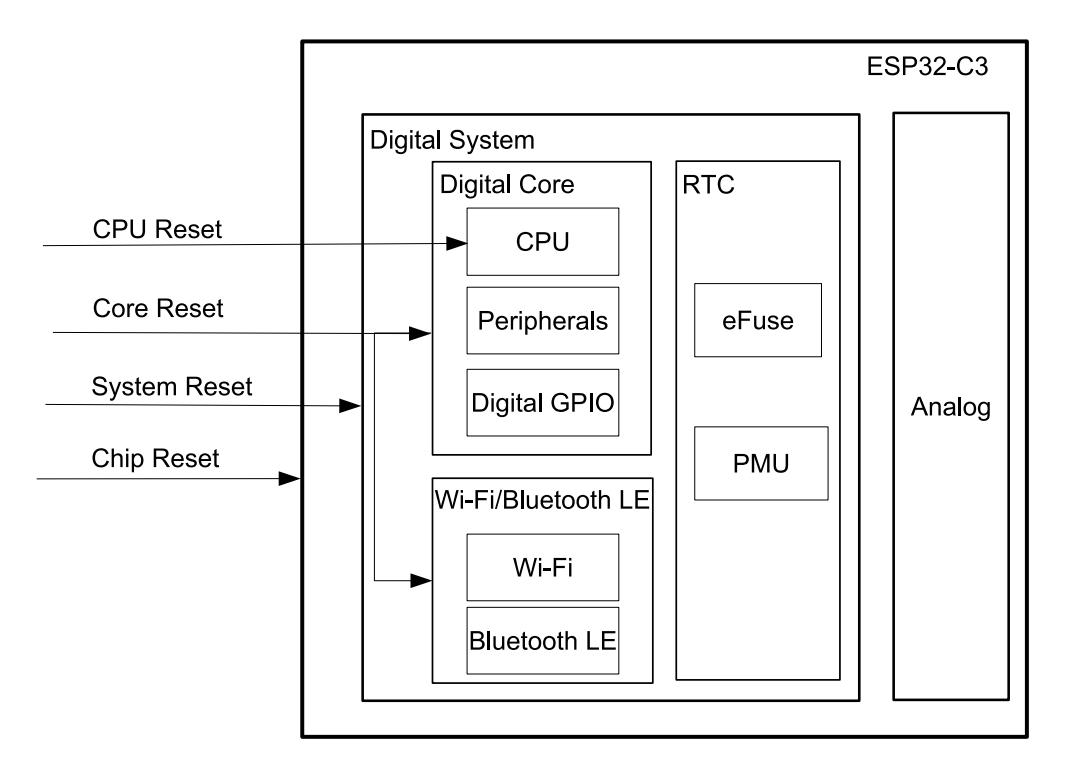

| Reset Types | 191 | |

| System Clock | 194 | |

| Interrupt Matrix Structure | 202 | |

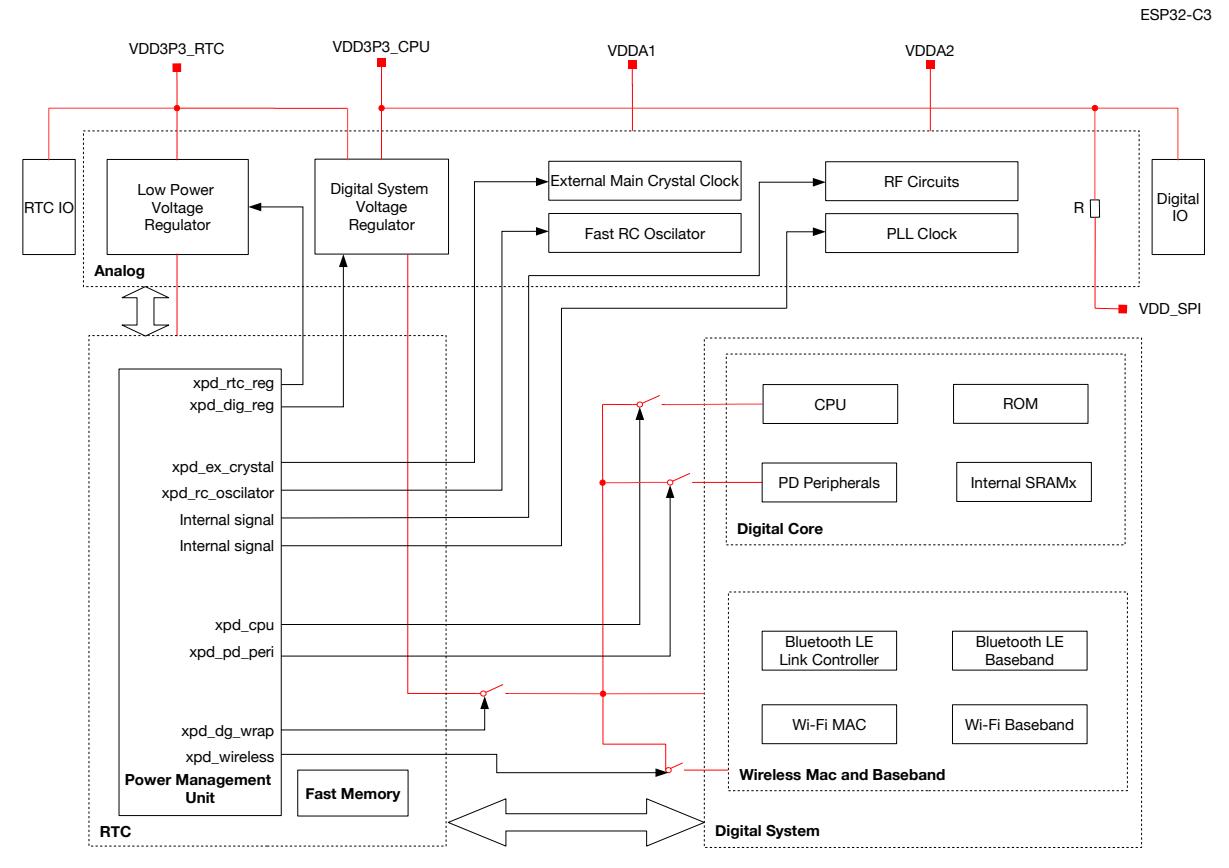

| Low-power Management Schematics | 220 | |

| Power Management Unit Workflow | 221 | |

| RTC Clocks | 222 | |

| Wireless Clock | 223 | |

| Digital System Regulator | 225 | |

| Low-power voltage regulator | 225 | |

| Brown-out detector | 226 | |

| ESP32-C3 Boot Flow | 230 | |

| System Timer Structure | 270 | |

| System Timer Alarm Generation | 271 | |

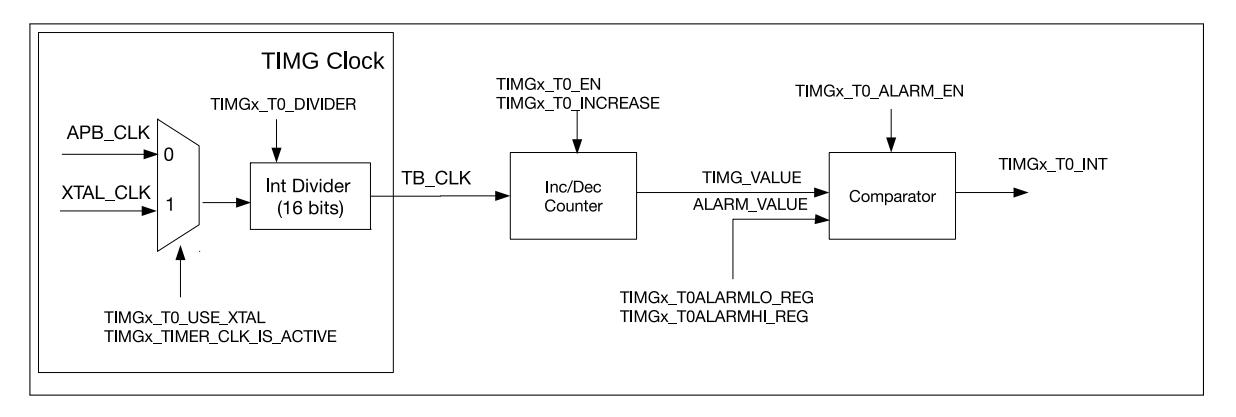

| Timer Units within Groups | 288 | |

| Timer Group Architecture | 289 | |

| Watchdog Timers Overview | 305 | |

| Watchdog Timers in ESP32-C3 | 307 | |

| Super Watchdog Controller Structure | 310 | |

| XTAL32K Watchdog Timer | 312 | |

| Permission Control Overview | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! |

| List of Figures | GoBack | |

|---|---|---|

|

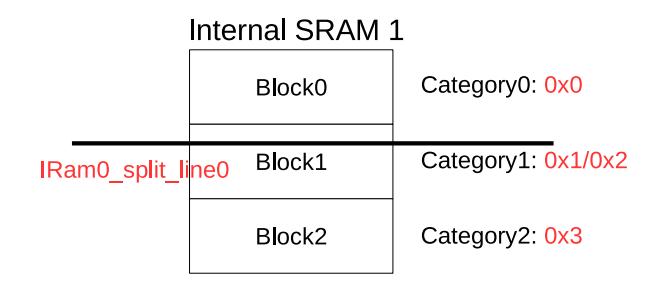

14.4-1

14.4-2 |

Split Lines for Internal SRAM1

An illustration of Configuring the Category fields |

319

321 |

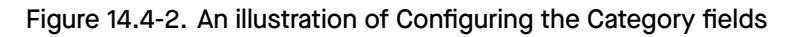

| 14.6-1 | Two Ways to Access External Memory | 326 |

| 15.4-1 | Switching From Secure World to Non-secure World | 415 |

|

15.4-2

15.5-1 |

Switching From Non-secure World to Secure World

World Switch Log Register |

416

417 |

| 15.5-2 | Nested Interrupts Handling - Entry 9 | 418 |

| 15.5-3 | Nested Interrupts Handling - Entry 1 | 419 |

| 15.5-4 | Nested Interrupts Handling - Entry 4 | 419 |

|

19.3-1

19.3-2 |

HMAC SHA-256 Padding Diagram

HMAC Structure Schematic Diagram |

491

492 |

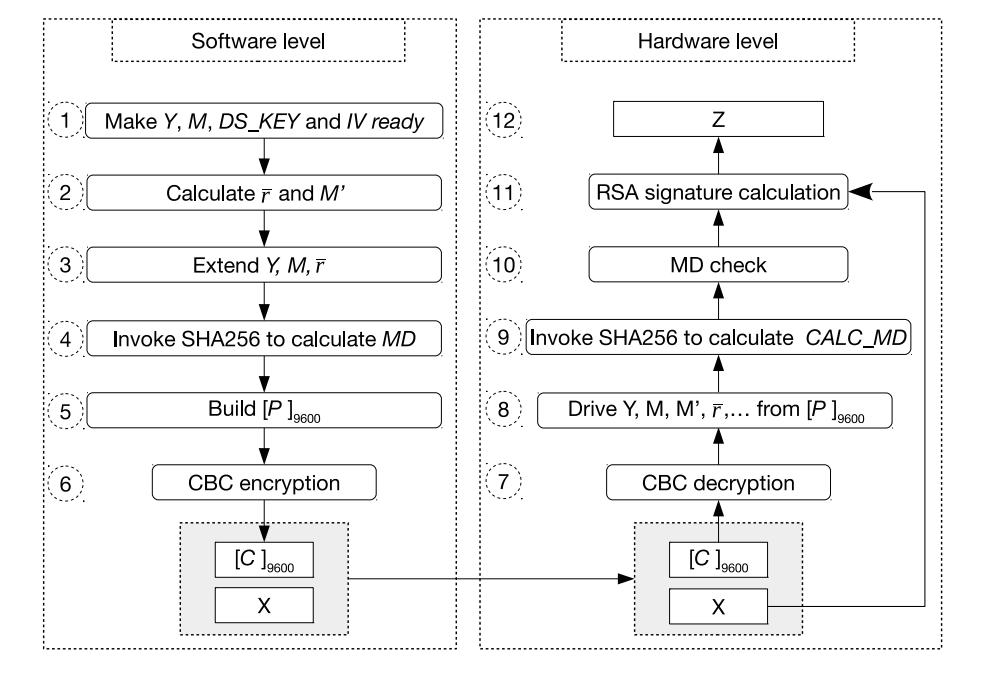

| 22.3-1 | Software Preparations and Hardware Working Process | 525 |

| 23.3-1 | Architecture of the External Memory Encryption and Decryption | 535 |

| 24.3-1 | Noise Source | 544 |

| 25.2-1 | XTAL_CLK Pulse Width | 547 |

| 26.3-1 | UART Architecture Overview | 550 |

| 26.3-2 | UART Structure | 550 |

|

26.4-1

26.4-2 |

UART Controllers Sharing RAM

UART Controllers Division |

552

554 |

| 26.4-3 | The Timing Diagram of Weak UART Signals Along Falling Edges | 554 |

| 26.4-4 | Structure of UART Data Frame | 555 |

| 26.4-5 | AT_CMD Character Structure | 556 |

| 26.4-6 | Driver Control Diagram in RS485 Mode | 557 |

| 26.4-7 | The Timing Diagram of Encoding and Decoding in SIR mode | 558 |

| 26.4-8 | IrDA Encoding and Decoding Diagram | 558 |

| 26.4-9 | Hardware Flow Control Diagram | 559 |

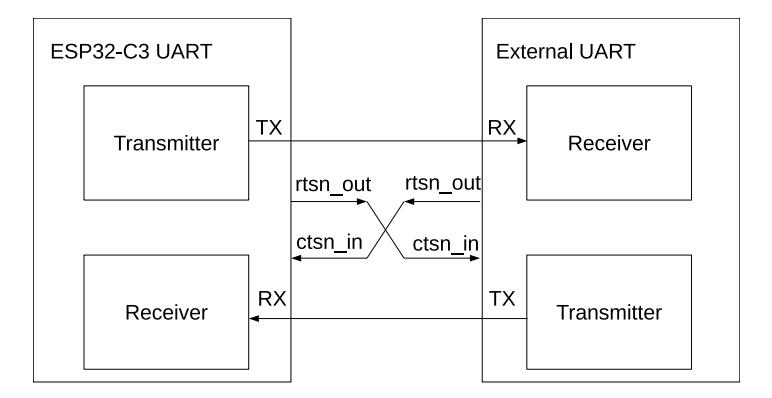

| 26.4-10 | Connection between Hardware Flow Control Signals | 560 |

|

26.4-11

26.5-1 |

Data Transfer in GDMA Mode

UART Programming Procedures |

561

565 |

| 27.4-1 | SPI Module Overview | 610 |

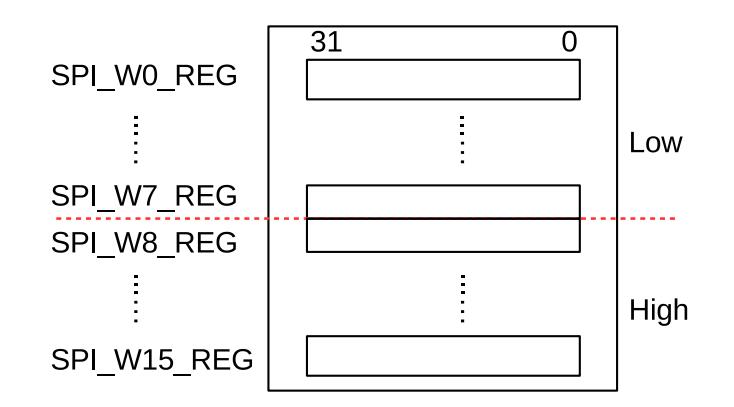

| 27.5-1 | Data Buffer Used in CPU-Controlled Transfer | 615 |

|

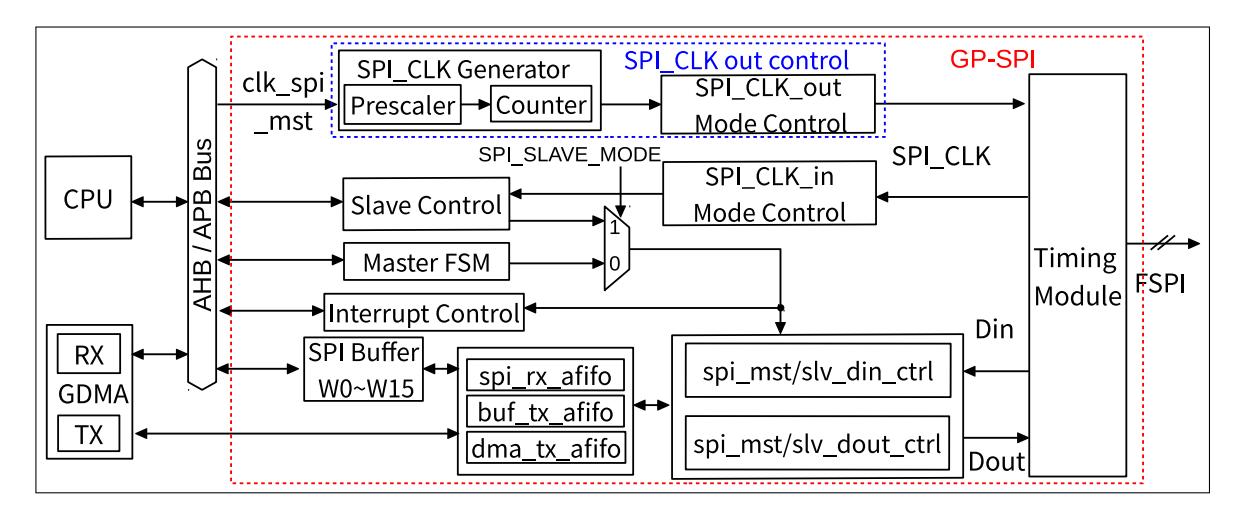

27.5-2

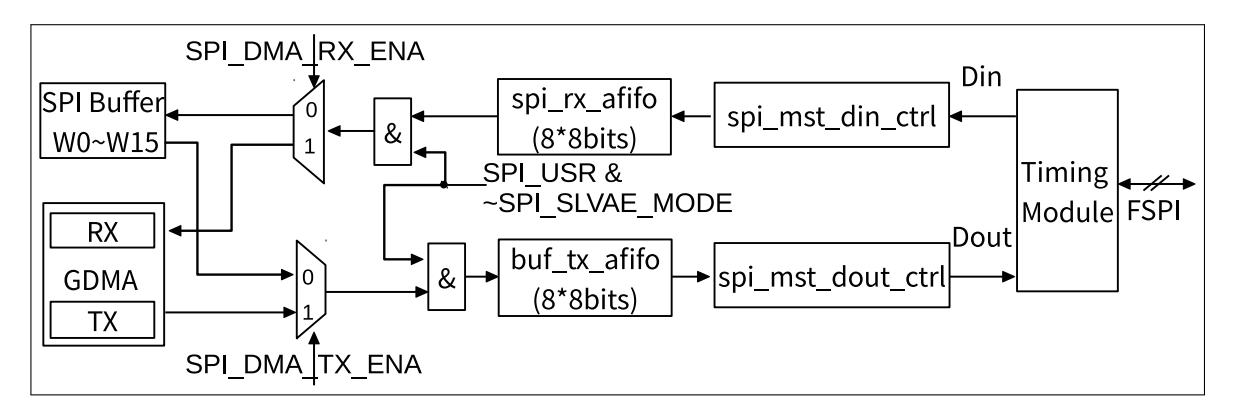

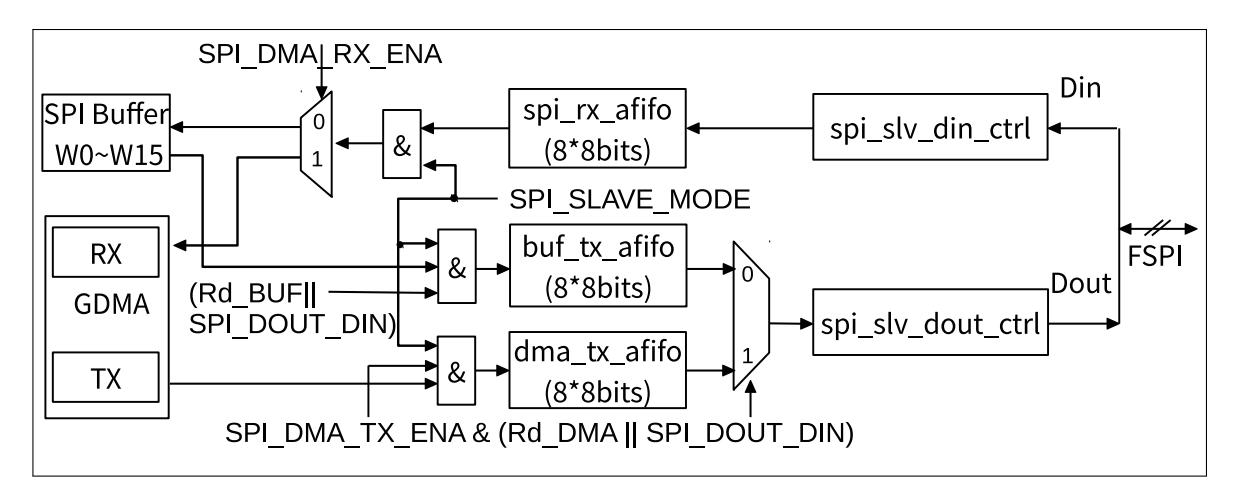

27.5-3 |

GP-SPI2 Block Diagram

Data Flow Control in GP-SPI2 Master Mode |

618

619 |

| 27.5-4 | Data Flow Control in GP-SPI2 Slave Mode | 620 |

| 27.5-5 | GP-SPI2 State Machine in Master Mode | 622 |

| 27.5-6 | Full-Duplex Communication Between GP-SPI2 Master and a Slave | 626 |

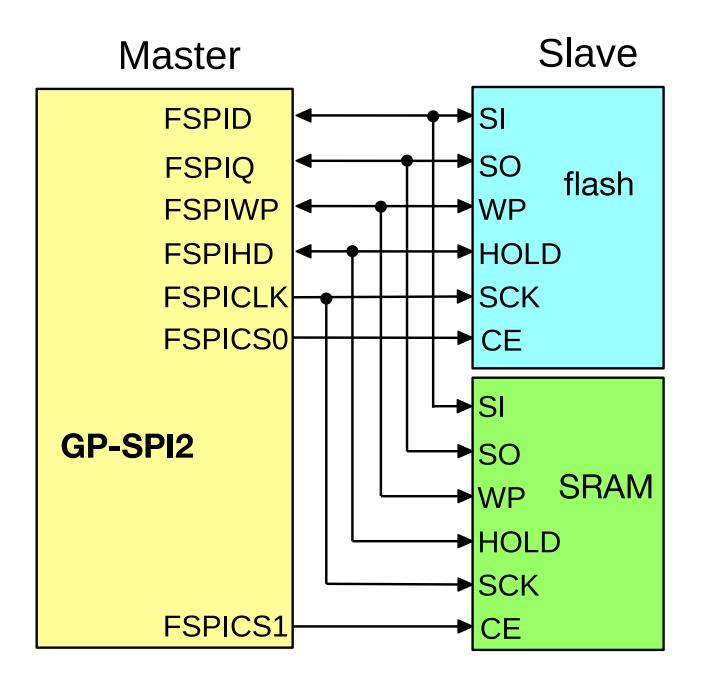

| 27.5-7 | Connection of GP-SPI2 to Flash and External RAM in 4-bit Mode | 629 |

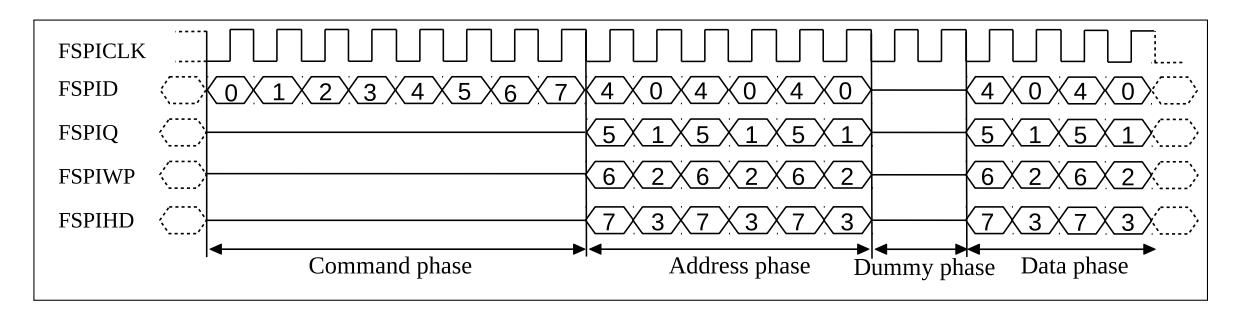

| 27.5-8 | SPI Quad I/O Read Command Sequence Sent by GP-SPI2 to Flash | 629 |

| 27.5-9 | Configurable Segmented Transfer in DMA-Controlled Master Mode | 630 |

| 27.6-1 | Recommended CS Timing and Settings When Accessing External RAM | 639 |

| List of Figures | GoBack | |

| 27.7-1 | SPI Clock Mode 0 or 2 | 641 |

|

27.7-2

27.8-1 |

SPI Clock Mode 1 or 3

Timing Compensation Control Diagram in GP-SPI2 Master Mode |

641

643 |

| 27.8-2 | Timing Compensation Example in GP-SPI2 Master Mode | 644 |

|

28.3-1

28.3-2 |

I2C Master Architecture

I2C Slave Architecture |

677

677 |

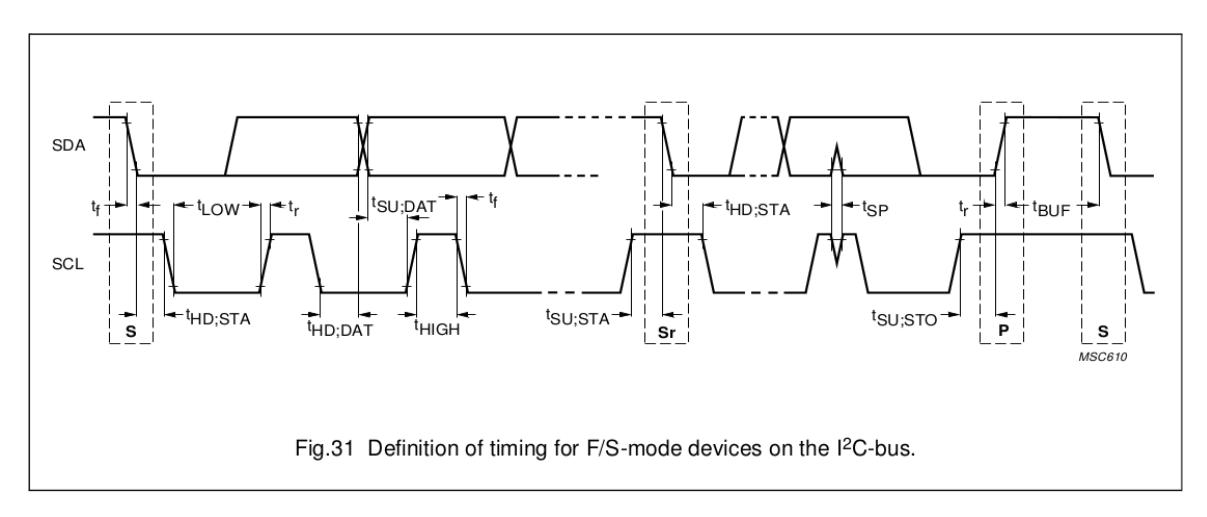

| 28.3-3 | I2C Protocol Timing (Cited from Fig.31 in The I2C-bus specification Version 2.1) | 678 |

| 28.3-4 | I2C Timing Parameters (Cited from Table 5 in The I2C-bus specification Version 2.1) | 679 |

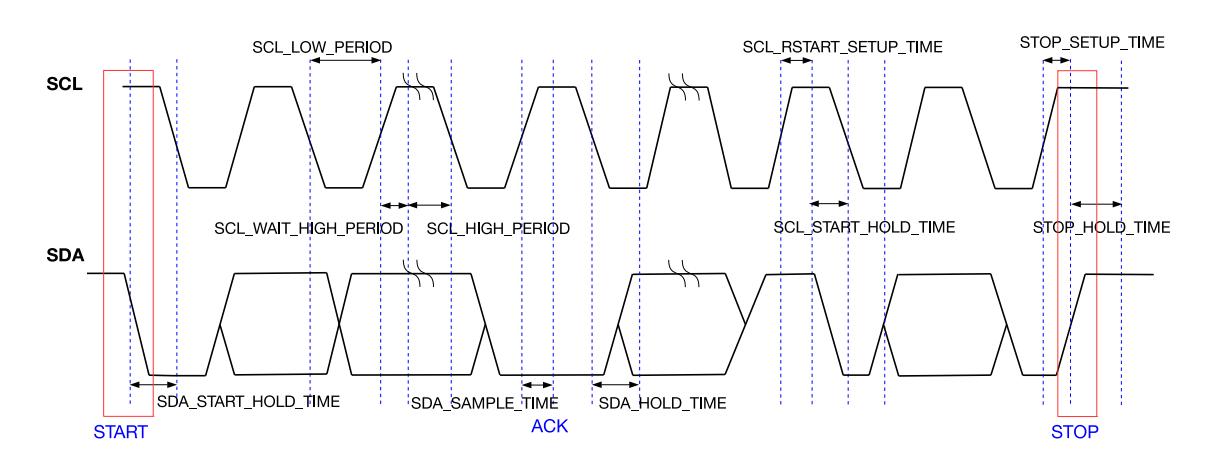

| 28.4-1 | I2C Timing Diagram | 682 |

| 28.4-2 | Structure of I2C Command Registers | 684 |

| 28.5-1 |

I2Cmaster

Writing to I2Cslave with a 7-bit Address |

688 |

| 28.5-2 |

I2Cmaster

Writing to a Slave with a 10-bit Address |

690 |

| 28.5-3 |

I2Cmaster

Writing to I2Cslave with Two 7-bit Addresses |

692 |

| 28.5-4 |

I2Cmaster

Writing to I2Cslave with a 7-bit Address in Multiple Sequences |

694 |

| 28.5-5 |

I2Cmaster

Reading I2Cslave with a 7-bit Address |

696 |

|

28.5-6

28.5-7 |

I2Cmaster

Reading I2Cslave with a 10-bit Address I2Cmaster Reading N Bytes of Data from addrM of I2Cslave with a 7-bit Address |

698

701 |

| 28.5-8 |

I2Cmaster

Reading I2Cslave with a 7-bit Address in Segments |

704 |

| 29.4-1 | ESP32-C3 I2S System Diagram | 732 |

| 29.5-1 | TDM Philips Standard Timing Diagram | 734 |

| 29.5-2 | TDM MSB Alignment Standard Timing Diagram | 735 |

|

29.5-3

29.5-4 |

TDM PCM Standard Timing Diagram

PDM Standard Timing Diagram |

735

736 |

| 29.6-1 | I2S Clock | 736 |

| 29.9-1 | TX Data Format Control | 741 |

| 29.9-2 | TDM Channel Control | 743 |

| 29.9-3 | PDM Channel Control Example | 745 |

| 30.2-1 | USB Serial/JTAG High Level Diagram | 765 |

| 30.2-2 | USB Serial/JTAG Block Diagram | 766 |

| 31.2-1 | Bit Fields in Data Frames and Remote Frames | 791 |

| 31.2-2 | Fields of an Error Frame | 793 |

| 31.2-3 | Fields of an Overload Frame | 793 |

| 31.2-4 | The Fields within an Interframe Space | 794 |

| 31.2-5 | Layout of a Bit | 797 |

| 31.3-1 | TWAI Overview Diagram | 798 |

|

31.4-1

31.4-2 |

Acceptance Filter

Single Filter Mode |

807

808 |

| 31.4-3 | Dual Filter Mode | 809 |

| 31.4-4 | Error State Transition | 810 |

| 31.4-5 | Positions of Arbitration Lost Bits | 812 |

| 32.2-1 | LED PWM Architecture | 827 |

| 32.3-1 | LED PWM Generator Diagram | 828 |

| 32.3-2 | Frequency Division When LEDC_CLK_DIV is a Non-Integer Value | 829 |

| List of Figures | GoBack | |

| 32.3-3 | LED_PWM Output Signal Diagram | 832 |

| 32.3-4 | Output Signal Diagram of Fading Duty Cycle | 832 |

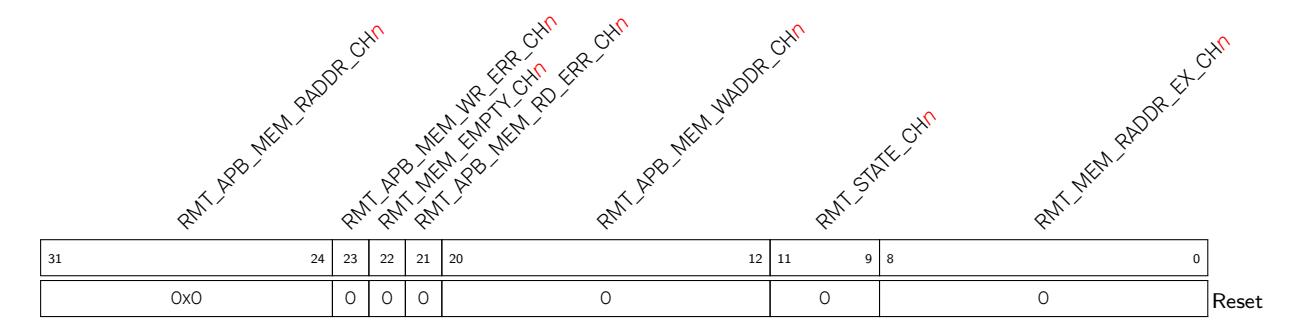

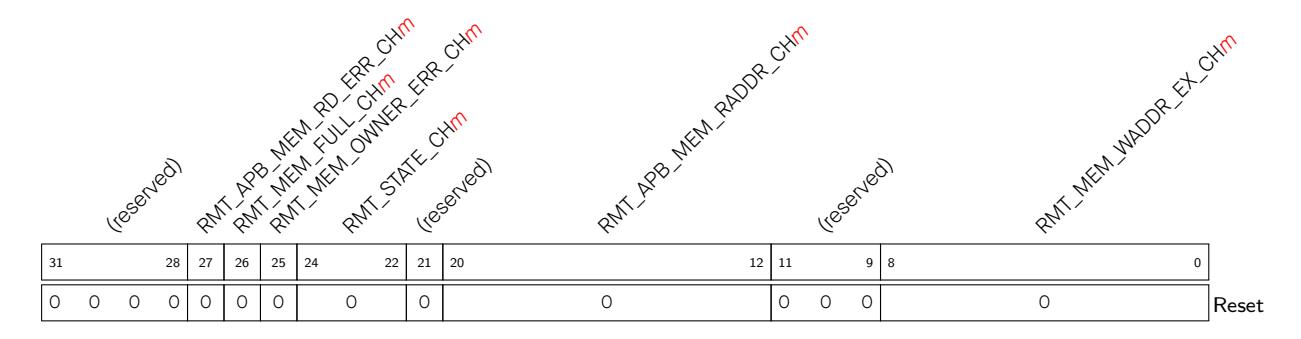

| 33.3-1 | RMT Architecture | 844 |

| 33.3-2 | Format of Pulse Code in RAM | 844 |

| 34.2-1 | SAR ADCs Function Overview | 869 |

| 34.2-2 | Diagram of DIG ADC FSM | 872 |

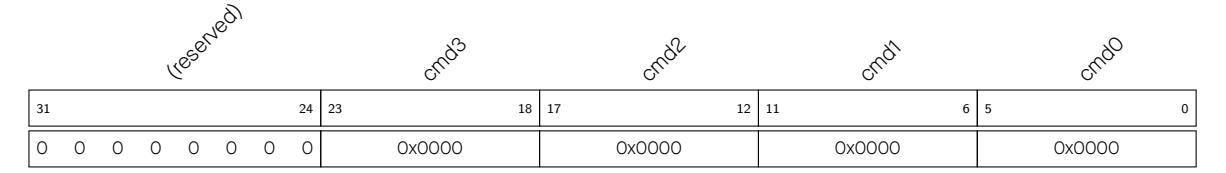

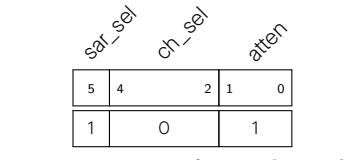

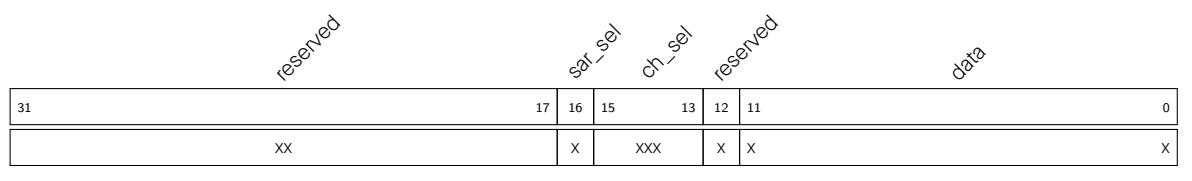

| 34.2-3 | APB_SARADC_SAR_PATT_TAB1_REG and Pattern Table Entry 0 - Entry 3 | 873 |

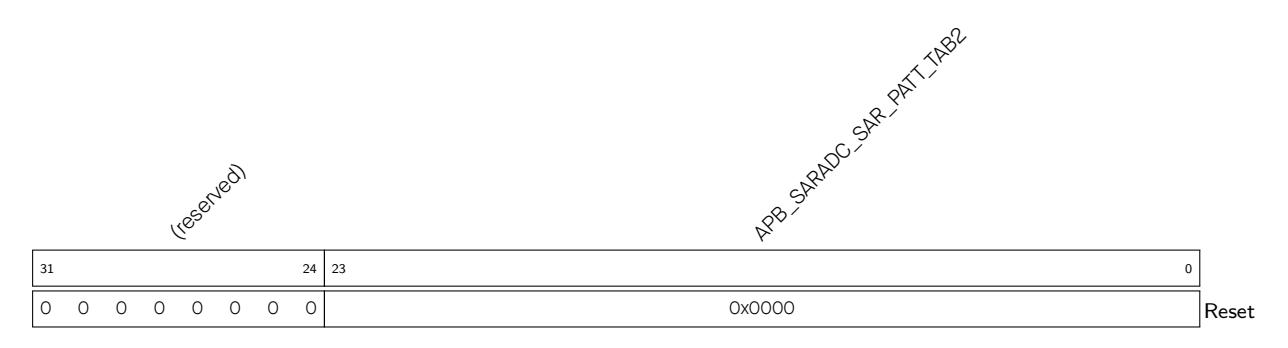

| 34.2-4 | APB_SARADC_SAR_PATT_TAB2_REG and Pattern Table Entry 4 - Entry 7 | 873 |

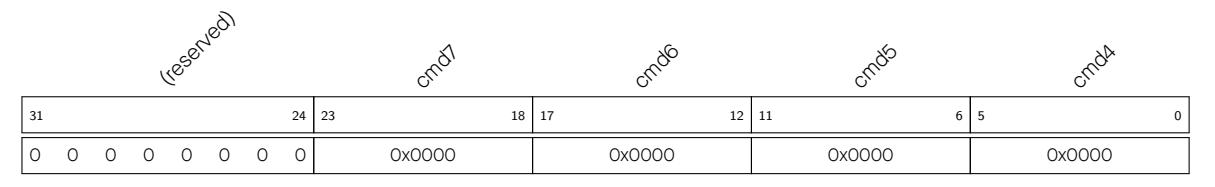

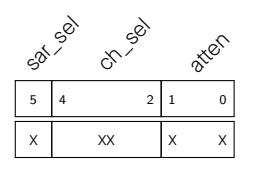

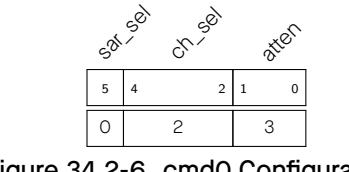

| 34.2-5 | Pattern Table Entry | 873 |

This part covers the essential processing elements of the system. Details include controllers for Direct Memory Access (DMA) and RISC-V CPU.

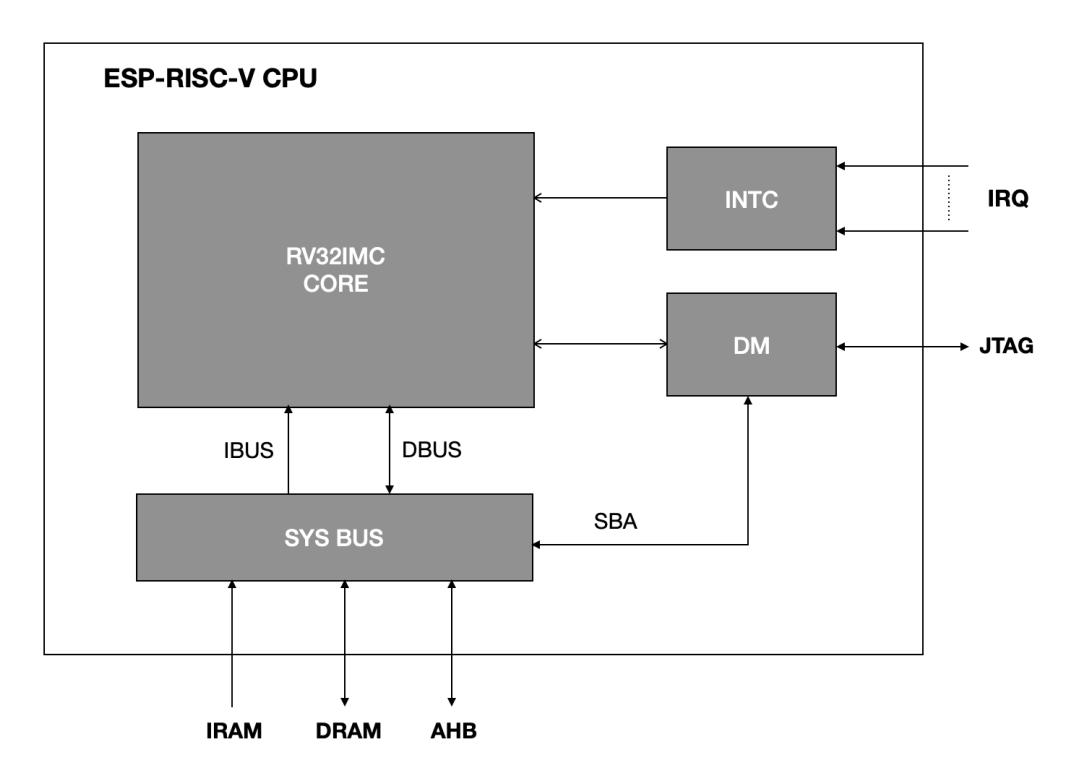

ESP-RISC-V CPU is a 32-bit core based upon RISC-V ISA comprising base integer (I), multiplication/division (M) and compressed (C) standard extensions. The core has 4-stage, in-order, scalar pipeline optimized for area, power and performance. CPU core complex has an interrupt-controller (INTC), debug module (DM) and system bus (SYS BUS) interfaces for memory and peripheral access.

Below table shows address map of various regions accessible by CPU for instruction, data, system bus peripheral and debug.

| Table 1.3-1. CPU Address Map | |

|---|---|

| Table 1.3-1. CPU Address Map | ||||

|---|---|---|---|---|

| Name | Description | Starting Address | Ending Address | Access |

| IRAM | Instruction Address Map | 0x4000_0000 | 0x47FF_FFFF | R/W |

| DRAM | Data Address Map | 0x3800_0000 | 0x3FFF_FFFF | R/W |

*default : Address not matching any of the specified ranges (IRAM, DRAM, DM) are accessed using AHB bus.

Below is a list of CSRs available to the CPU. Except for the custom performance counter CSRs and the tcontrol register (which complies with the RISC-V External Debug Support Version 0.13.2), all the implemented CSRs follow the standard mapping of bit fields as described in the RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10. It must be noted that even among the standard CSRs, not all bit fi elds have been implemented, limited by the subset of features implemented in the CPU. Refer to the next section for detailed description of the subset of fields implemented under each of these CSRs.

|

Name

Description Address Access |

||||||||||

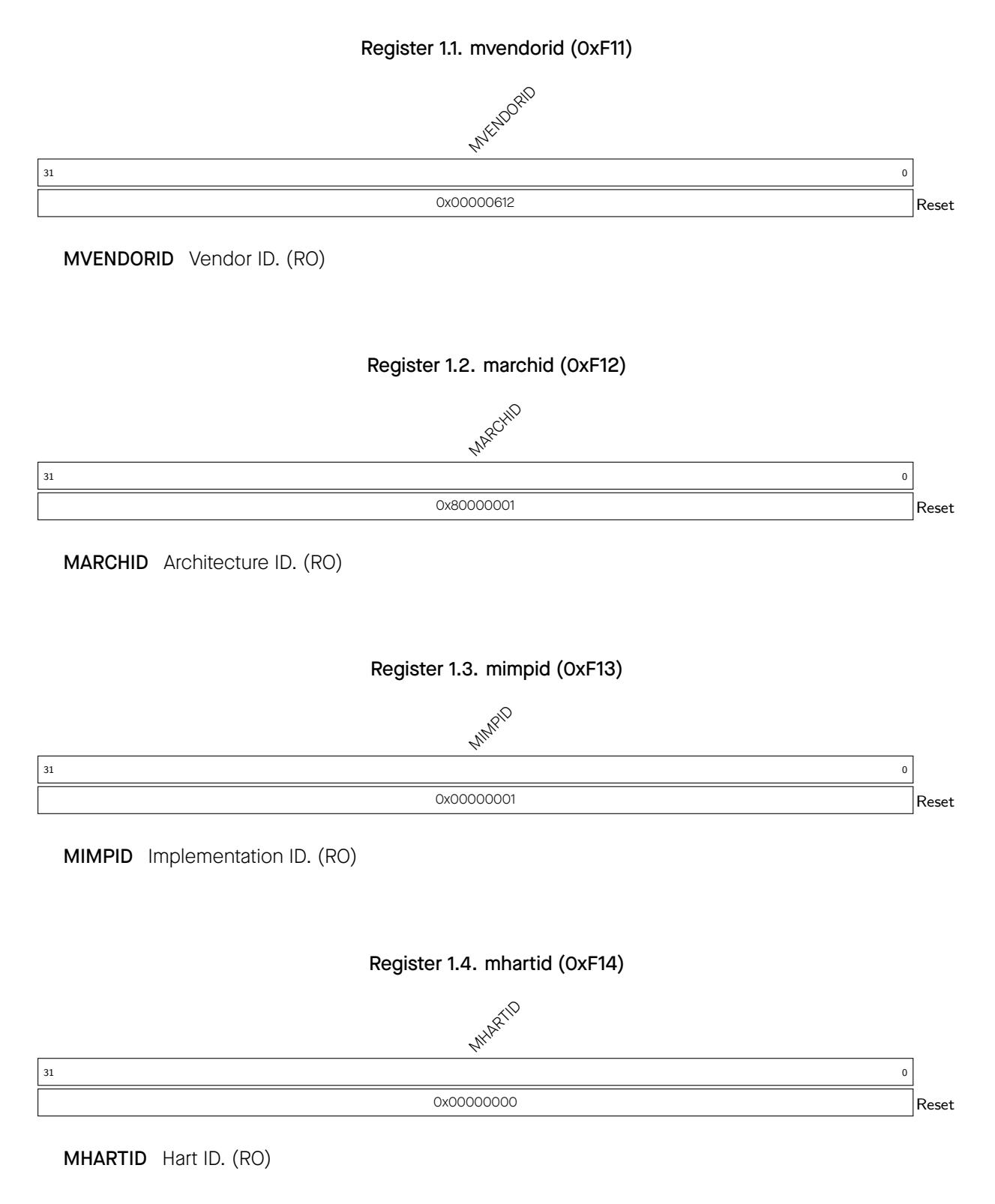

| Machine Information CSRs | ||||||||||

| mvendorid | Machine Vendor ID | 0xF11 | RO | |||||||

|

marchid

mimpid |

Machine Architecture ID

Machine Implementation ID |

0xF12

0xF13 |

RO

RO |

|||||||

| mhartid | Machine Hart ID | 0xF14 | RO | |||||||

The abbreviations given in Column Access are explained in Section Access Types for Registers .

| Chapter 1 ESP-RISC-V CPU | GoBack | ||

| Name | Description | Address | Access |

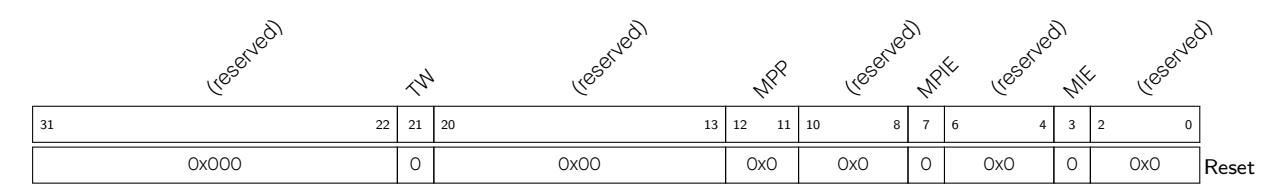

| mstatus | Machine Mode Status | 0x300 | R/W |

| misa ¹ | Machine ISA | 0x301 | R/W |

| mtvec ² | Machine Trap Vector | 0x305 | R/W |

| Machine Trap Handling CSRs | |||

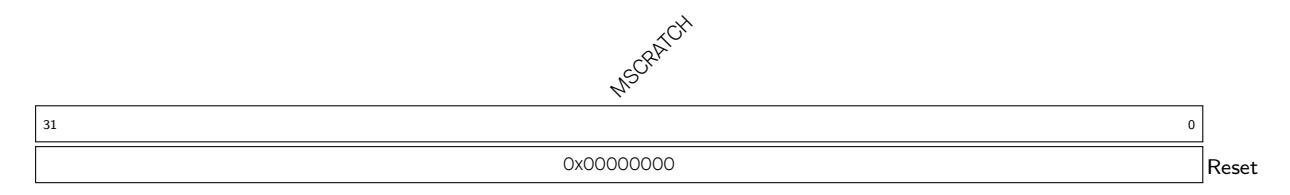

| mscratch | Machine Scratch | 0x340 | R/W |

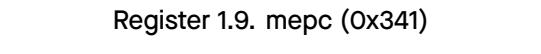

| mepc | Machine Trap Program Counter | 0x341 | R/W |

|

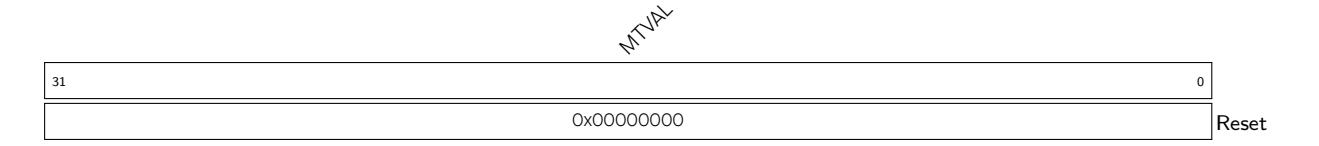

mcause ³

mtval |

Machine Trap Cause

Machine Trap Value |

0x342

0x343 |

R/W

R/W |

| Physical Memory Protection (PMP) CSRs | |||

| pmpcfg0 | Physical memory protection configuration | 0x3A0 | R/W |

| pmpcfg1 | Physical memory protection configuration | 0x3A1 | R/W |

| pmpcfg2 | Physical memory protection configuration | 0x3A2 | R/W |

| pmpcfg3 | Physical memory protection configuration | 0x3A3 | R/W |

| pmpaddr0 | Physical memory protection address register | 0x3B0 | R/W |

| pmpaddr1 | Physical memory protection address register | 0x3B1 | R/W |

| pmpaddr15 | Physical memory protection address register | 0x3BF | R/W |

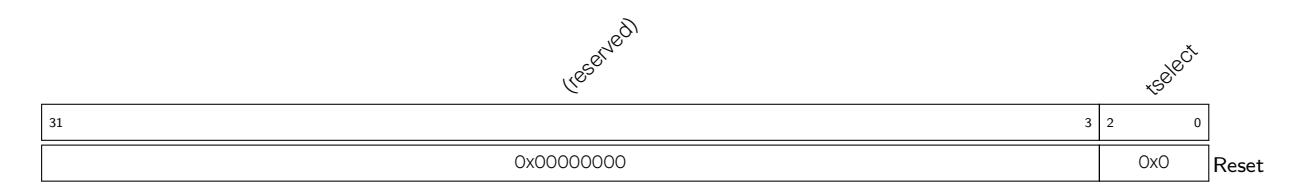

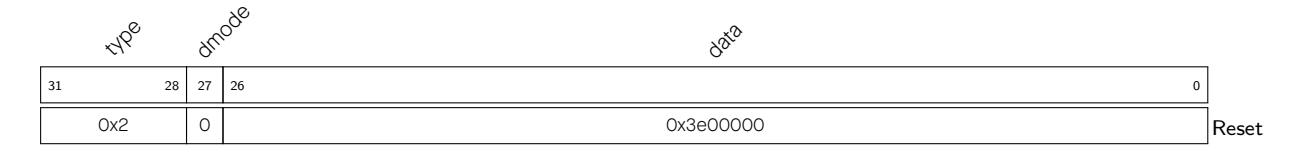

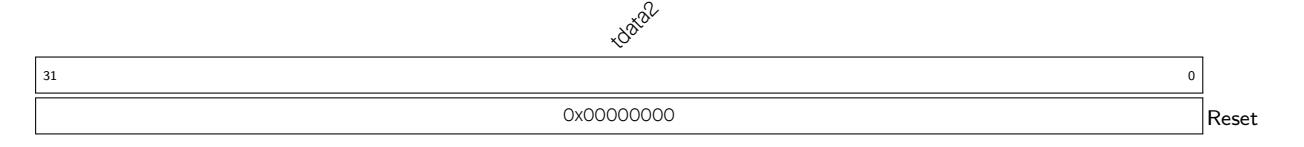

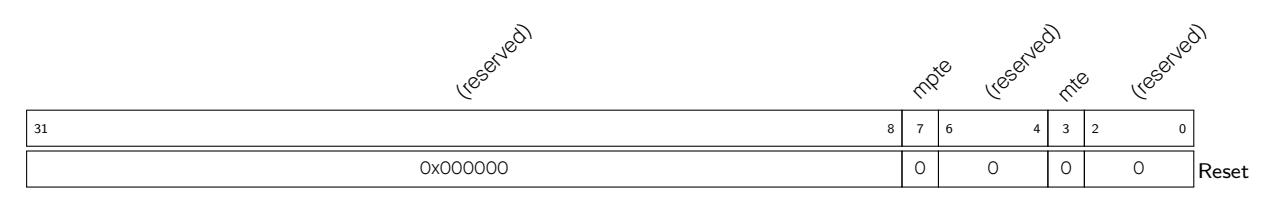

| Trigger Module CSRs (shared with Debug Mode) | |||

| tselect | Trigger Select Register | 0x7A0 | R/W |

| tdata1 | Trigger Abstract Data 1 | 0x7A1 | R/W |

| tdata2 | Trigger Abstract Data 2 | 0x7A2 | R/W |

| tcontrol | Global Trigger Control | 0x7A5 | R/W |

| Debug Mode CSRs | |||

|

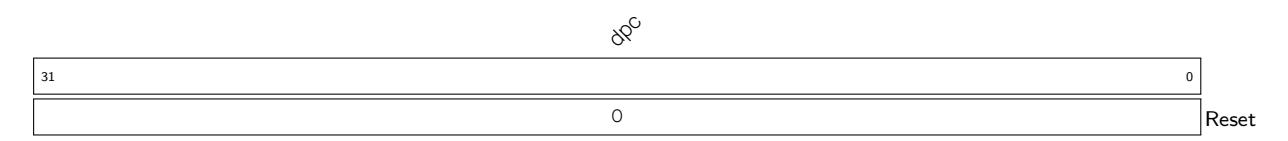

dcsr

dpc |

Debug Control and Status

Debug PC |

0x7B0

0x7B1 |

R/W

R/W |

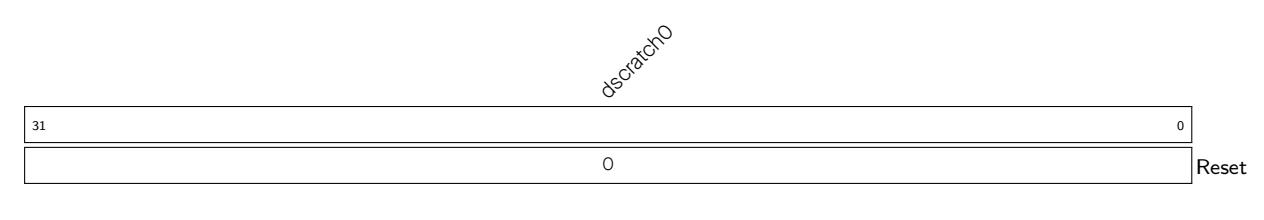

| dscratch0 | Debug Scratch Register 0 | 0x7B2 | R/W |

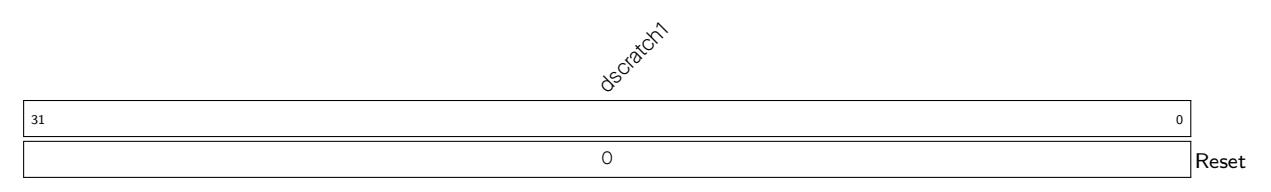

| dscratch1 | Debug Scratch Register 1 | 0x7B3 | R/W |

| Performance Counter CSRs (Custom) ⁴ | |||

| mpcer | Machine Performance Counter Event | 0x7E0 | R/W |

| mpcmr | Machine Performance Counter Mode | 0x7E1 | R/W |

| mpccr | Machine Performance Counter Count | 0x7E2 | R/W |

| GPIO Access CSRs (Custom) | |||

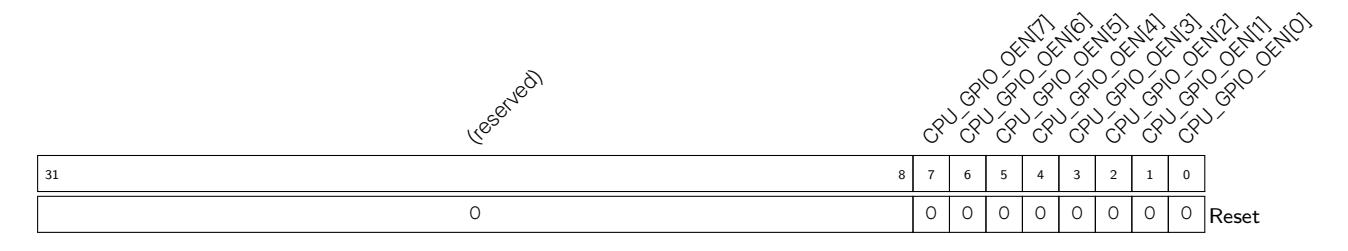

| cpu_gpio_oen | GPIO Output Enable | 0x803 | R/W |

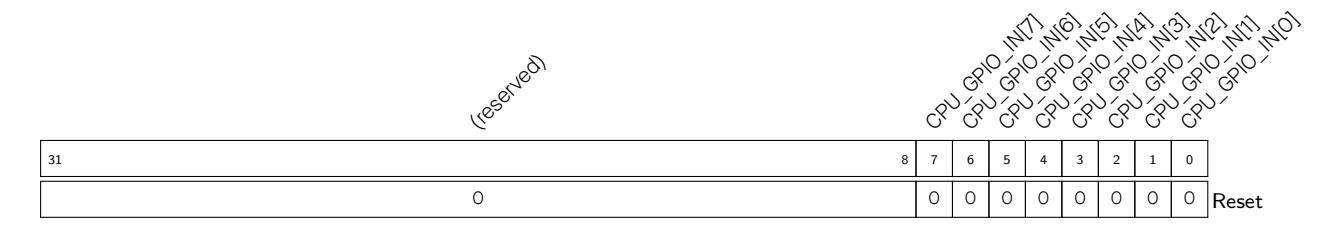

| cpu_gpio_in | GPIO Input Value | 0x804 | RO |

No te that if write /set/clear operation is attempted on any of the CSRs which are read-only (RO), as indicated in th e above table, t he CPU will generate illegal instruction exception.

¹Although misa is specified as having both read and write access (R/W), its fields are hardwired and thus write has no effect. This is what would be termed WARL (Write Any Read Legal) in RISC-V terminology

²mtvec only provides configuration for trap handling in vectored mode with the base address aligned to 256 bytes

³External interrupt IDs reflected in mcause include even those IDs which have been reserved by RISC-V standard for core internal sources. ⁴These cu stom CSRs have been implemented in the address space reserved by RISC-V standard for custom use

Possible values:

Note : Only lower bit is writable. Write to the higher bit is ignored as it is directly tied to the lower bit.

TW Timeout wait. (R/W)

If this bit is set, executing WFI (Wait-for-Interrupt) instruction in User mode will cause illegal instruction exception.

| Register 1.6. misa (0x301) | ||||||

|---|---|---|---|---|---|---|

| (reserved) | ||||||

|

MXL

31 30 |

W

M Q O Z Y V U S R P N K H G D C B A X T L F E J I 29 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|||||

| 0x1 |

0x0

0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 |

|||||

| MXL | Machine XLEN = 1 (32-bit). (RO) | |||||

| Z | Reserved = 0. (RO) | |||||

| Y | Reserved = 0. (RO) | |||||

| X | Non-standard extensions present = 0. (RO) | |||||

| W | Reserved = 0. (RO) | |||||

| V | Reserved = 0. (RO) | |||||

| U | User mode implemented = 1. (RO) | |||||

| T | Reserved = 0. (RO) | |||||

| S | Supervisor mode implemented = 0. (RO) | |||||

| R | Reserved = 0. (RO) | |||||

| Q | Quad-precision floating-point extension = 0. (RO) | |||||

| P | Reserved = 0. (RO) | |||||

| O | Reserved = 0. (RO) | |||||

| N | User-level interrupts supported = 0. (RO) | |||||

| M | Integer Multiply/Divide extension = 1. (RO) | |||||

| L | Reserved = 0. (RO) | |||||

| K | Reserved = 0. (RO) | |||||

| J | Reserved = 0. (RO) | |||||

| I | RV32I base ISA = 1. (RO) | |||||

| H | Hypervisor extension = 0. (RO) | |||||

| G | Additional standard extensions present = 0. (RO) | |||||

|

F

E |

Single-precision floating-point extension = 0. (RO) | |||||

| D |

RV32E base ISA = 0. (RO)

Double-precision floating-point extension = 0. (RO) |

|||||

| C | Compressed Extension = 1. (RO) | |||||

A Atomic Extension = 0. (RO)

Espressif Systems 36

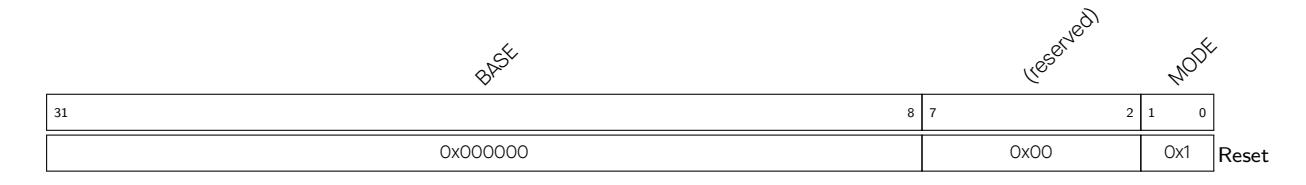

MODE Only vectored mode 0x1 is available. (RO)

BASE Higher 24 bits of trap vector base address aligned to 256 bytes. (R/W)

MSCRATCH Machine scratch register for custom use. (R/W)

MEPC Machine trap/exception program counter. (R/W)

This is automatically updated with address of the instruction which was about to be executed while CPU encountered the most recent trap.

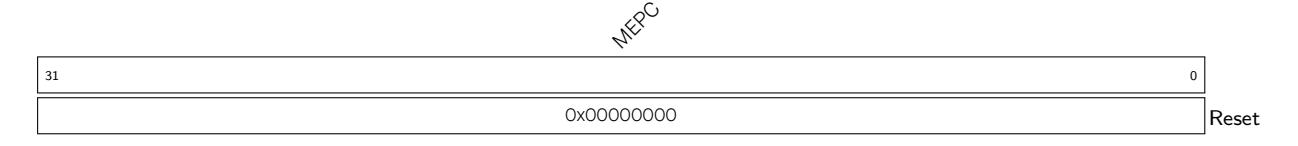

Exception Code This field is automatically updated with unique ID of the most recent exception or interrupt due to which CPU entered trap. (R/W)

Possible exception IDs are:

Note : Exception ID 0x0 (instruction access misaligned) is not present because CPU always masks the lowest bit of the address during instruction fetch.

Interrupt Flag This flag is automatically updated when CPU enters trap. (R/W)

If this is found to be set, indicates that the latest trap occurred due to interrupt. For exceptions it remains unset.

Note : The interrupt controller is using up IDs in range 1-31 for all external interrupt sources. This is different from the RISC-V standard which has reserved IDs in range 0-15 for core internal interrupt sources.

MTVAL Machine trap value. (R/W)

This is automatically updated with an exception dependent data which may be useful for handling that exception.

Data is to be interpreted depending upon exception IDs:

Note : The value of this register is not valid for other exception IDs and interrupts.

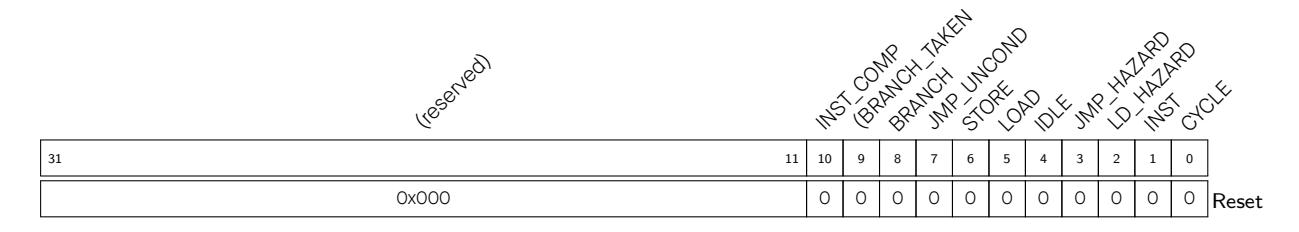

INST_COMP Count Compressed Instructions. (R/W)

BRANCH_TAKEN Count Branches Taken. (R/W)

BRANCH Count Branches. (R/W)

JMP_UNCOND Count Unconditional Jumps. (R/W)

STORE Count Stores. (R/W)

LOAD Count Loads. (R/W)

IDLE Count IDLE Cycles. (R/W)

JMP_HAZARD Count Jump Hazards. (R/W)

LD_HAZARD Count Load Hazards. (R/W)

INST Count Instructions. (R/W)

CYCLE Count Clock Cycles. Cycle count does not increment during WFI mode. (R/W)

Note: Each bit selects a specific event for counter to increment. If more than one event is selected and occurs simultaneously, then counter increments by one only.

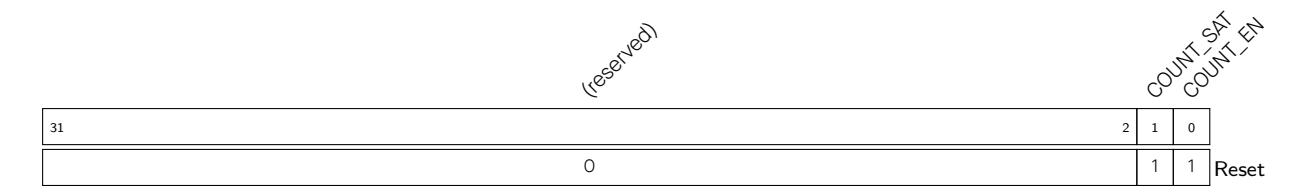

COUNT_SAT Counter Saturation Control. (R/W) Possible values:

COUNT_EN Counter Enable Control. (R/W)

Possible values:

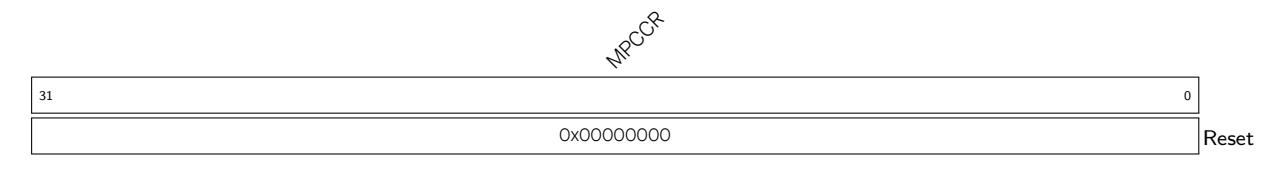

MPCCR Machine Performance Counter Value. (R/W)

Register 1.15. cpu_gpio_oen (0x803)

CPU_GPIO_OEN GPIOn (n=0 ~ 21) Output Enable. CPU_GPIO_OEN[7:0] correspond to output enable signals cpu_gpio_out_oen[7:0] in Table 5.11-1 Peripheral Signals via GPIO Matrix . CPU_GPIO_OEN value matches that of cpu_gpio_out_oen. CPU_GPIO_OEN is the enable signal of CPU_GPIO_OUT. (R/W)

CPU_GPIO_IN GPIOn (n=0 ~ 21) Input Value. It is a CPU CSR to read input value (1=high, 0=low) from SoC GPIO pin.

CPU_GPIO_IN[7:0] correspond to input signals cpu_gpio_in[7:0] in Table 5.11-1 Peripheral Signals via GPIO Matrix .

CPU_GPIO_IN[7:0] can only be mapped to GPIO pins through GPIO matrix. For details please refer to Section 5.4 in Chapter IO MUX and GPIO Matrix (GPIO, IO MUX) . (RO)

| Register 1.17. cpu_gpio_out (0x805) | ||||||

|---|---|---|---|---|---|---|

| CPU_GPIO_OUT[7] | CPU_GPIO_OUT[6] |

CPU_GPIO_OUT[5]

CPU_GPIO_OUT[4] |

CPU_GPIO_OUT[3] |

CPU_GPIO_OUT[2]

CPU_GPIO_OUT[1] |

CPU_GPIO_OUT GPIOn (n=0 ~ 21) Output Value. It is a CPU CSR to write value (1=high, 0=low) to SoC GPIO pin. The value takes effect only when CPU_GPIO_OEN is set.

CPU_GPIO_OUT[7:0] correspond to output signals cpu_gpio_out[7:0] in Table 5.11-1 Peripheral Signals via GPIO Matrix .

CPU_GPIO_OUT[7:0] can only be mapped to GP IO pins through G PIO matrix. For details please refer to Section 5.5 in Chapter IO MUX and GPIO Matrix (GPIO, IO MUX) . (R/W)

The interrupt controller allows capturing, masking and dynamic prioritization of interrupt sources routed from peripherals to the RISC-V CPU. It supports:

For the complete list of interrupt registers and detailed configuration information, please refer to Chapter 8 Interrupt Matrix (INTERRUPT) , section 8.4, register group "CPU Interrupt Registers".

Each interrupt ID has 5 prope rties ass ocia ted with it:

When CPU services a pending interrupt, it:

Table 1.5-1 shows the ma ppin g of each interrupt ID with the corre spon ding trap-vector address. In short, the word aligned trap address for an interrupt with a certain ID = i can be calculated as ( mtvec + 4 i ).

Note : ID = 0 is unavailable and therefore cannot be used for capturing inter rupts. This is because the corre spon ding trap vector address (mtvec + 0x00) is reserved for exceptions.

| ID | Address | ID | Address | ID | Address |

ID

Address |

|||

| 0 | NA | 8 | mtvec + 0x20 | 16 | mtvec + 0x40 | 24 | mtvec + 0x60 | ||

| 1 | mtvec + 0x04 | 9 | mtvec + 0x24 | 17 | mtvec + 0x44 | 25 | mtvec + 0x64 | ||

| 2 | mtvec + 0x08 | 10 | mtvec + 0x28 | 18 | mtvec + 0x48 | 26 | mtvec + 0x68 | ||

| 3 | mtvec + 0x0c | 11 | mtvec + 0x2c | 19 | mtvec + 0x4c | 27 | mtvec + 0x6c | ||

| 4 | mtvec + 0x10 | 12 | mtvec + 0x30 | 20 | mtvec + 0x50 | 28 | mtvec + 0x70 | ||

| 5 | mtvec + 0x14 | 13 | mtvec + 0x34 | 21 | mtvec + 0x54 | 29 | mtvec + 0x74 | ||

| 6 | mtvec + 0x18 | 14 | mtvec + 0x38 | 22 | mtvec + 0x58 | 30 | mtvec + 0x78 | ||

Table 1.5-1. ID wise map of Interrupt Trap-Vector Addresses

After jumping to the trap-vector, the execution flow is dependent on software implementation, although it can be presumed that the interrupt will get handled (and cleared) in some interrupt service routine (ISR) and later the normal execution will resume once the CPU encounters MRET instruction.

Upon execution of MRET instruction, the CPU:

It is p ossibl e to perform softwa re assi sted ne sting of interrupts inside a n ISR as explained in 1.5.3.

The below listed points outline the f unction al behavior of the controller:

There is latency involved while configuring the Interrupt Controller.

In steady state operation, the Interrupt Controller has a fixed latency of 4 cycles. Steady state means that no changes have been made to the Interrupt Controller registers recently. This implies that any interrupt that is asserted to the controller will take exactly 4 cycles before the CPU starts processing the interrupt. This further implies that CPU may execute up to 5 instructions before the preemption happens.

Whenever any of its registers are modified, the Interrupt Controller enters into transient state, which may take up to 4 cycles for it to settle down into steady state again. During this transient state, the ordering of interrupts may not be predictable, and therefore, a few safety measures need to be taken in software to avoid any synchronization issues.

Also, it must be noted that the Interrupt Controller configuration registers lie in the APB address range, hence any R/W access to these registers may take multiple cycles to complete.

In consideration of above mentioned characteristics, users are advised to follow the sequence described below, whenever modifying any of the Interrupt Controller registers:

Due to its critical nature, it is recommended to disable interrupts globally (MIE=0) beforehand, whenever configuring interrupt controller registers, and then restore MIE right after, as shown in the sequence above.

After execution of the sequence above, the Interrupt Controller will resum e op eration in steady state.

By default, interrupts are disabled globally, since the reset value of MIE bit in mstatus is 0. Software must set MIE=1 after initialization of the interrupt stack (including setting mtvec to the interrupt vector address) is done.

During normal execution, if an interrupt n is to be enabled, the bel ow se que nce may be followed:

When one or more interrupts become pending, the CPU acknowledges (claims) the interrupt with the highest priority and jumps to the trap vector address corresponding to the interrupt's ID. Software implementation may read mcause to infer the type of trap (mcause(31) is 1 for interrupts and 0 for exceptions) and then the ID of the interrupt (mcause(4-0) gives ID of interrupt or exception). This inference may not be necessary if each entry in the trap vector are jump instructions to different trap handlers. Ultimately, the trap handler(s) will redir ect execu tion to the appropriate I SR for this in terrupt.

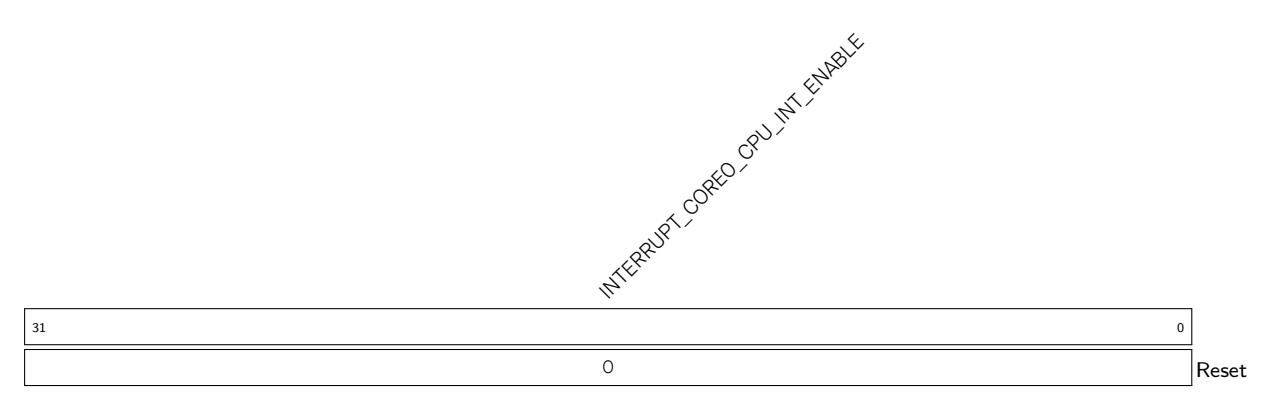

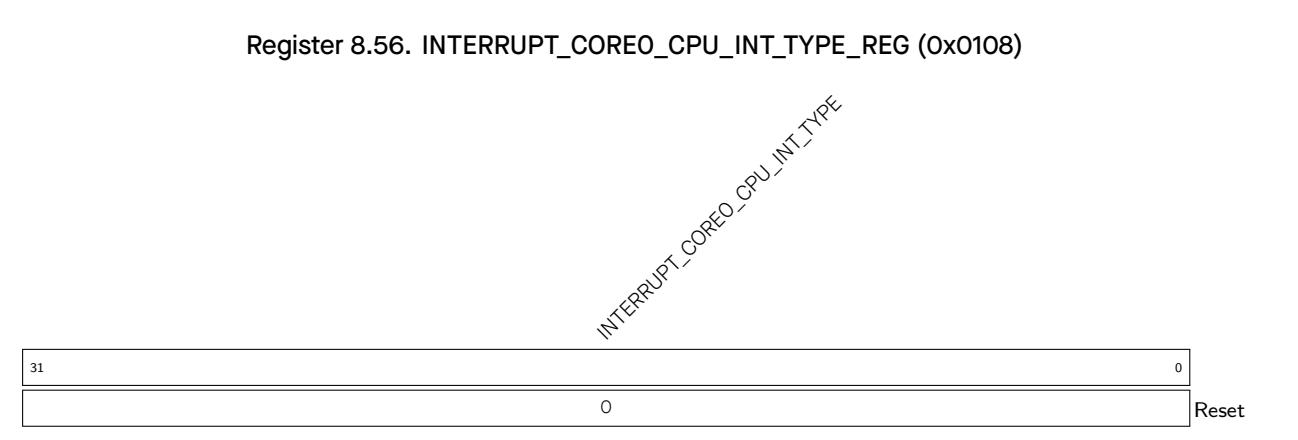

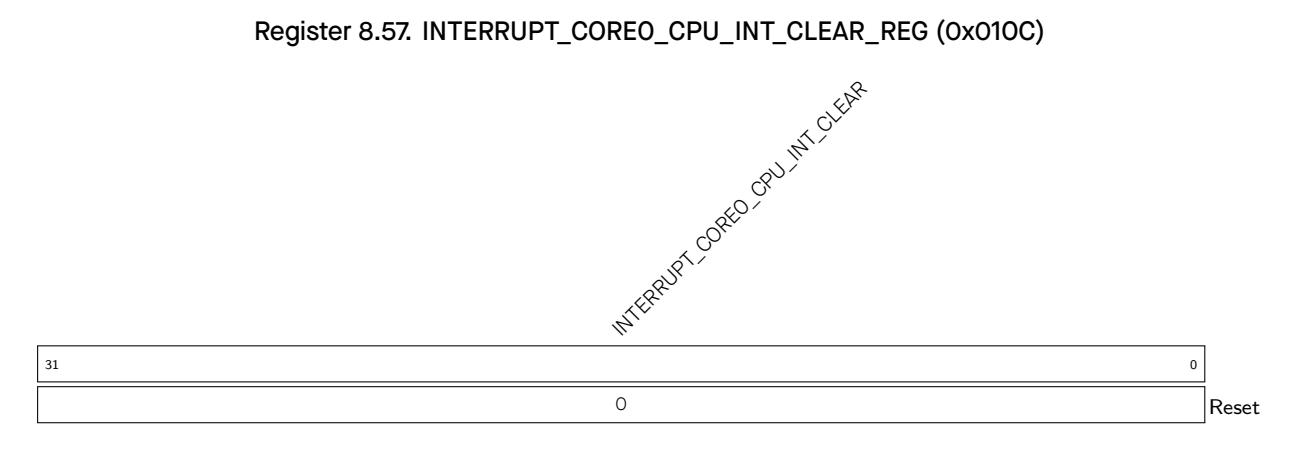

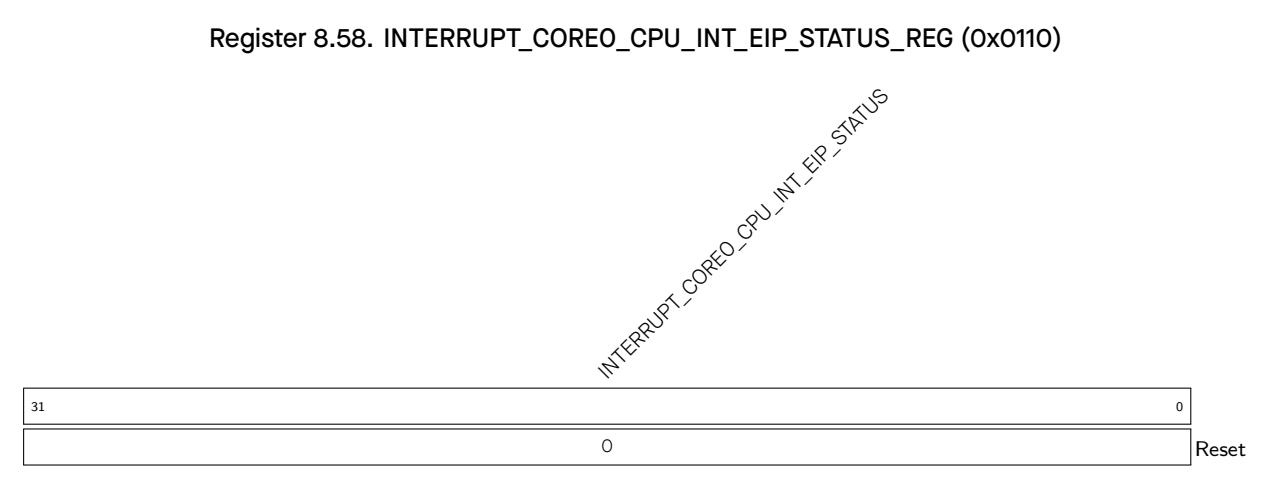

Upon enterin g into an ISR, s oftware must toggle the n th bit of INTERRUPT_CORE0_CPU_INT_CLEAR_REG if the interrupt is of edge type, or clear the source of the interrupt if it is of level type.

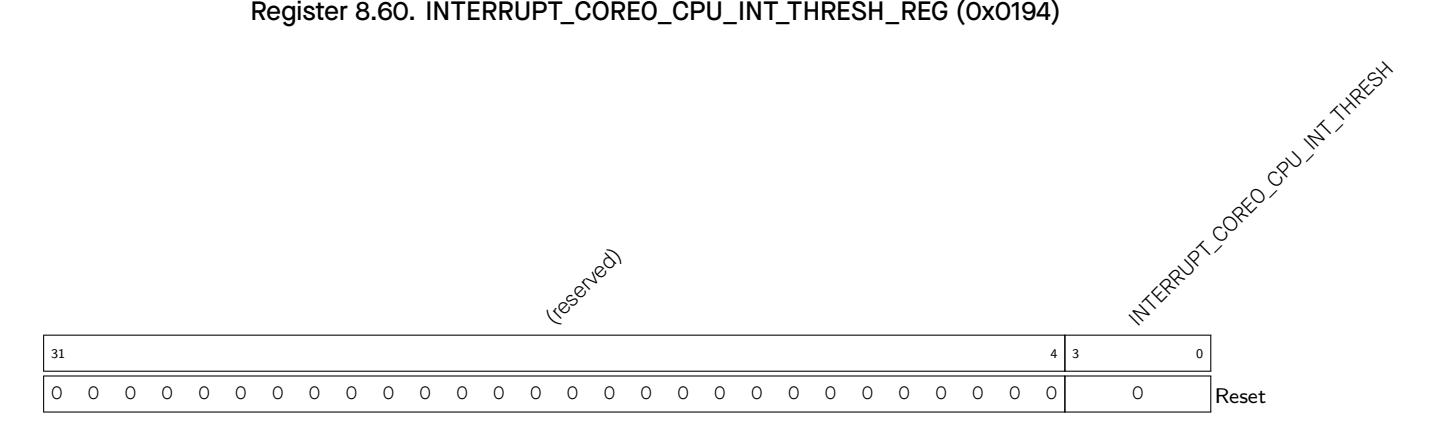

Software may also update the value of INTERRUPT_CORE0_CPU_INT_THRESH_REG and program MIE=1 for allowing higher priority interrupts to preempt the current ISR ( nesting), however, before doing so, all the s tate CSRs must be saved (mepc, mstatus, mcause, etc.) since they will get overwritten due to occurrence of such an interrupt. Later, when exiting the IS R, the values of these CSRs must be restored .

Finally, after the execution returns from the ISR back to the trap handler, MRET instruction is used to resume normal execution.

Later, if the n interrupt is no longer needed and needs to be disabled, the following sequence may be followed:

Above is only a suggested scheme of operation. Actual software implementation may vary.

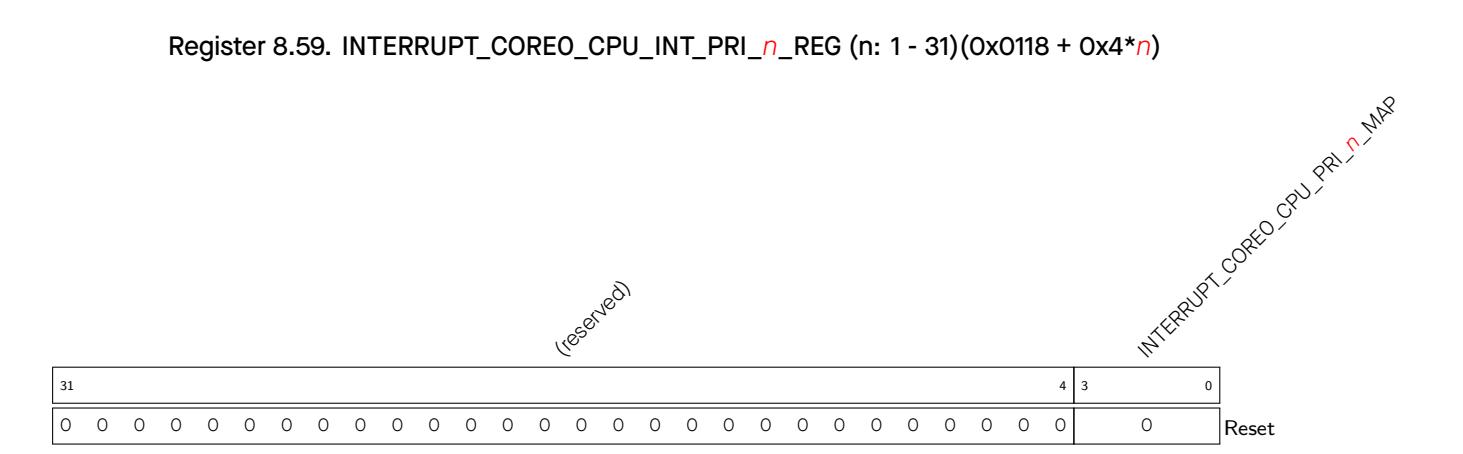

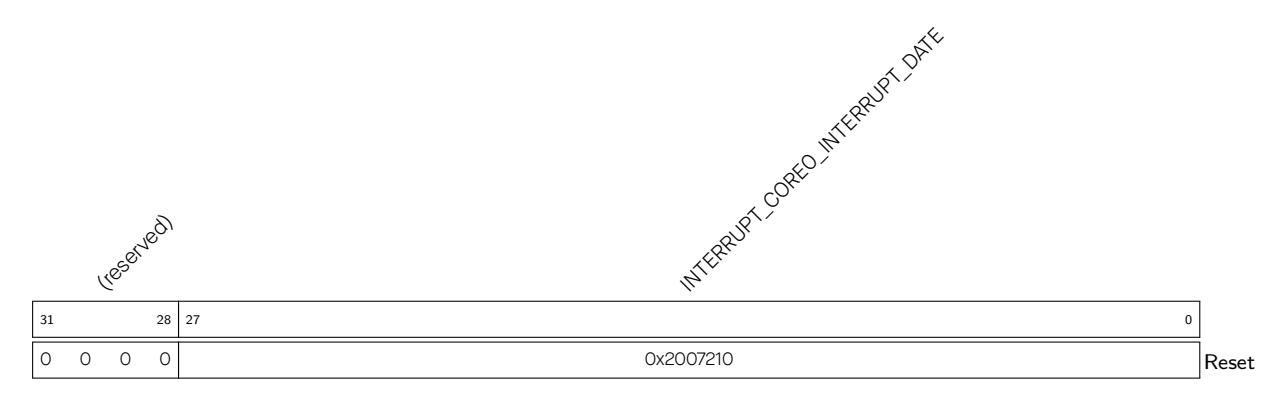

The addresses in this section are relative to Interrupt Controller base address provided in Table 3.3-3 in Chapter 3 System and Memory .

For the complete list of interrupt registers and detailed configuration information, please refer to Chapter 8 Interrupt Matrix (INTERRUPT) , section 8.4, register group "CPU Interrupt Registers".

The addresses in this section are relat ive to Interrupt Controller base address provided in Table 3.3-3 in Chapter 3 System and Memory .

For the complete list of interrupt registers and detailed configuration information, please refer to Chapter 8 Interrupt Matrix (INTERRUPT) , section 8.4, register group "CPU Interrupt Registers".

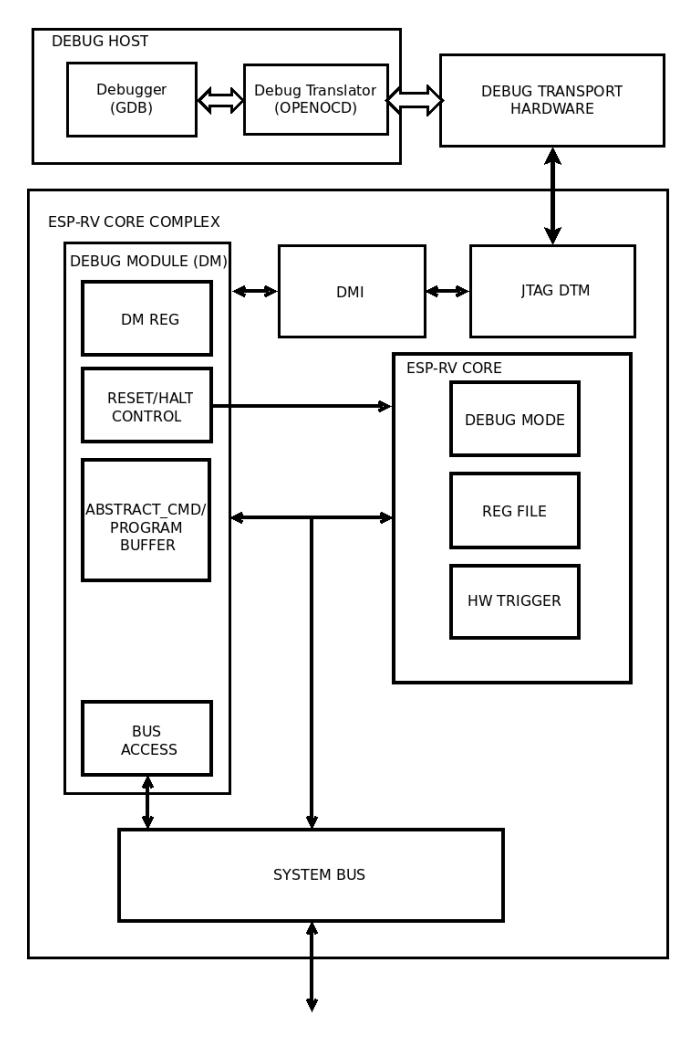

This section describes how to debug and test software running on CPU core. Debug support is provided through standard JTAG pins and complies to RISC-V External Debug Support Specification version 0.13.

Figure 1.6-1 below shows the main components of External Debug Support.

Figure 1.6-1. Debug System Overview

The user interacts with the Debug Host (eg. laptop), which is running a debugger (eg. gdb). The debugger communicates with a Debug Translator (eg. OpenOCD, which may include a hardware driver) to communicate with Debug Transport Hardware (eg. Olimex USB-JTAG adapter). The Debug Transport Hardware connects the Debug Host to the ESP-RV Core's Debug Transport Module (DTM) through standard JTAG interface. The DTM provides access to the Debug Module (DM) using the Debug Module Interface (DMI).

The DM allows the debugger to halt the core. Abstract commands provide access to its GPRs (general purpose registers). The Program Buffer allows the debugger to execute arbitrary code on the core, which allows access to additional CPU core state. Alternatively, additional abstract commands can provide access to additional CPU core state. ESP-RV core contains Trigger Module supporting 8 triggers. When trigger conditions are met, cores will halt spontaneously and inform the debug module that they have halted.

System bus access block allows memory and peripheral register access without using RISC-V core.

Espressif Systems 47

Basic debug functionality supports below features.

As mentioned earlier, Debug Scheme conforms to RISC-V External Debug Support Specification version 0.1 3. Please refer the specs for functional operation details.

Below is the list of Debug CSR's supported by ESP-RV core.

The abbreviations given in Column Access are explained in Section Access Types for Registers .

| The abbreviations given in Column Access are explained in Section Access Types for Registers. | |||

|---|---|---|---|

| Name | Description | Address | Access |

| dcsr | Debug Control and Status | 0x7B0 | R/W |

| dpc | Debug PC | 0x7B1 | R/W |

| dscratch0 | Debug Scratch Register 0 | 0x7B2 | R/W |

All the debug module registers are implemented in conformance to RISC-V External Debug Support Sp ecification version 0.13. Please refer it for more details.

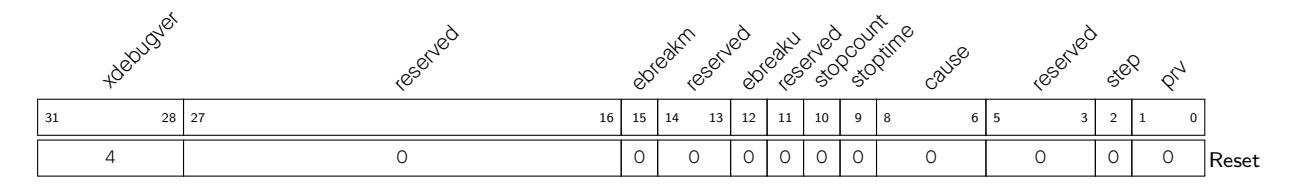

Below are the details of Debug CSR's supported by ESP-RV core

xdebugver Debug version. (RO)

ebreaku When 1, ebreak instructions in User/Application Mode enter Debug Mode. (R/W)

stopcount This bit is not implemented. Debugger will always read this bit as 0. (RO)

Other values are reserved for future use. (RO)

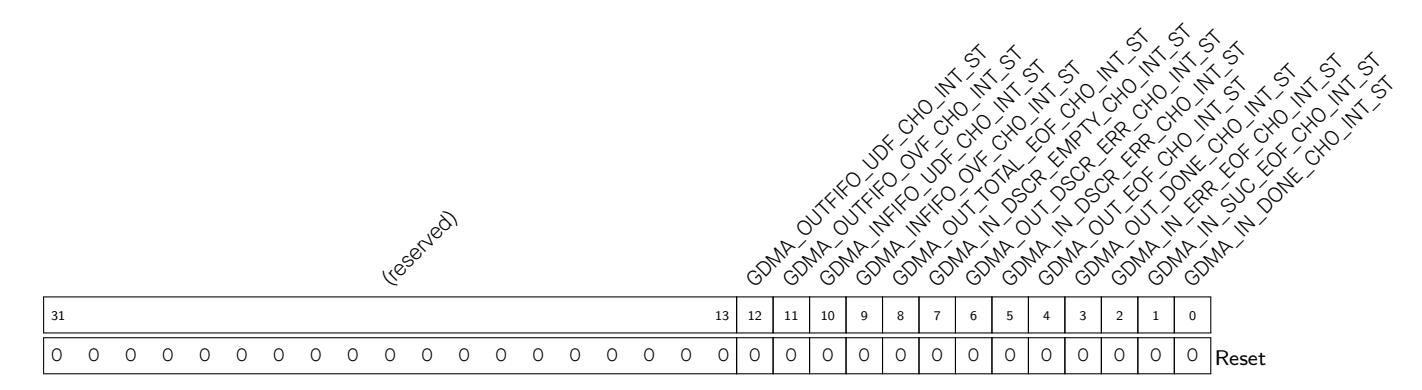

*Note: Different from RISC-V Debug specification 0.13

dpc Upon entry to debug mode, dpc is written with the virtual address of the instruction that encountered the exception. When resuming, the CPU core's PC is updated to the virtual address stored in dpc. A debugger may write dpc to change where the CPU resumes. (R/W)

dscratch0 Used by Debug Module internally. (R/W)

dscratch1 Used by Debug Module internally. (R/W)

Hardware Trigger module provides breakpoint and watchpoint capability for debugging. It includes the following features:

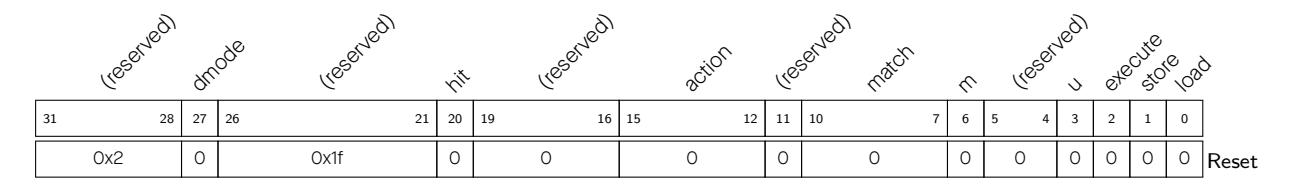

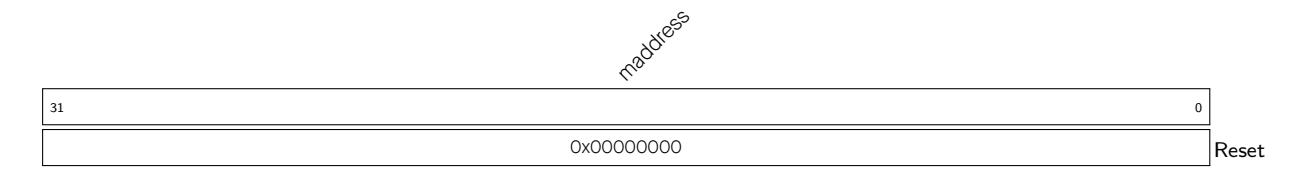

The Hardware Trigger module provides four CSRs, which are listed under register summary section. Among these, tdata1 and tdata2 are abstract CSRs, which means they are shadow registers for accessing internal registers for each of the eight trigger units, one at a time.

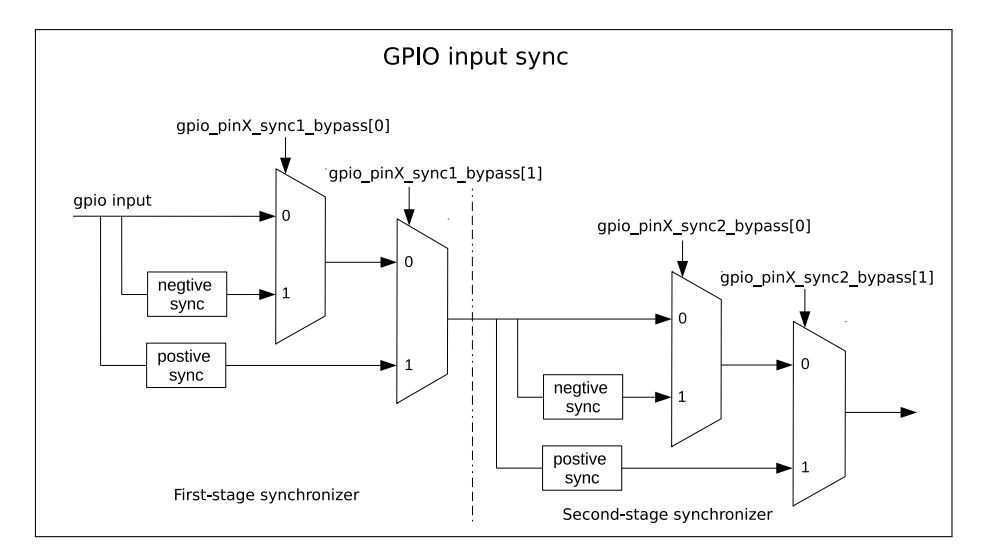

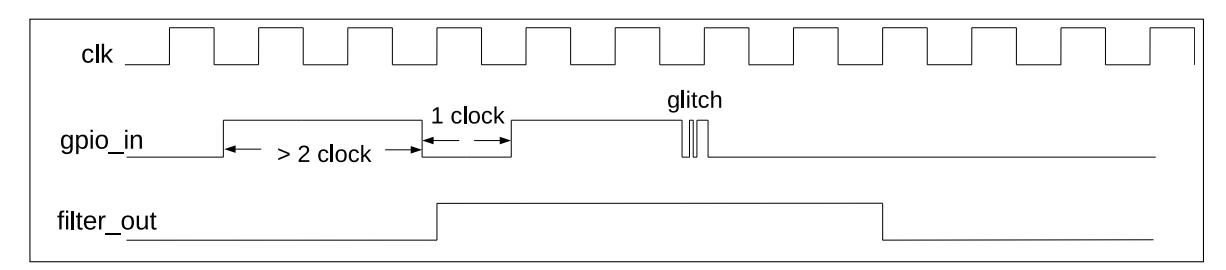

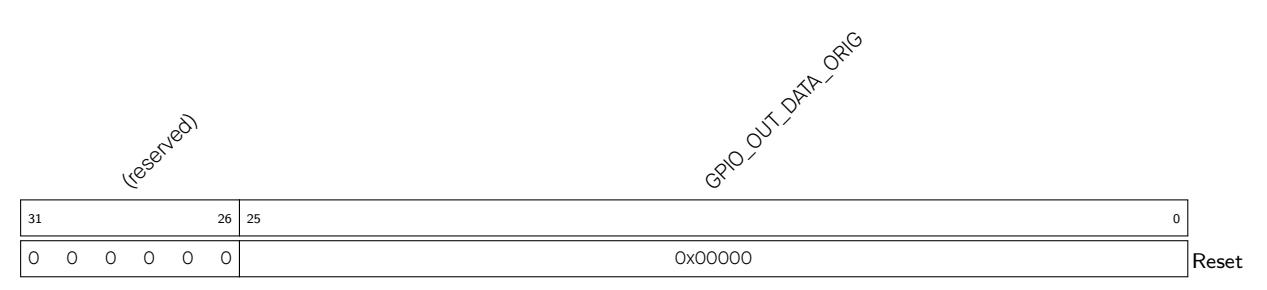

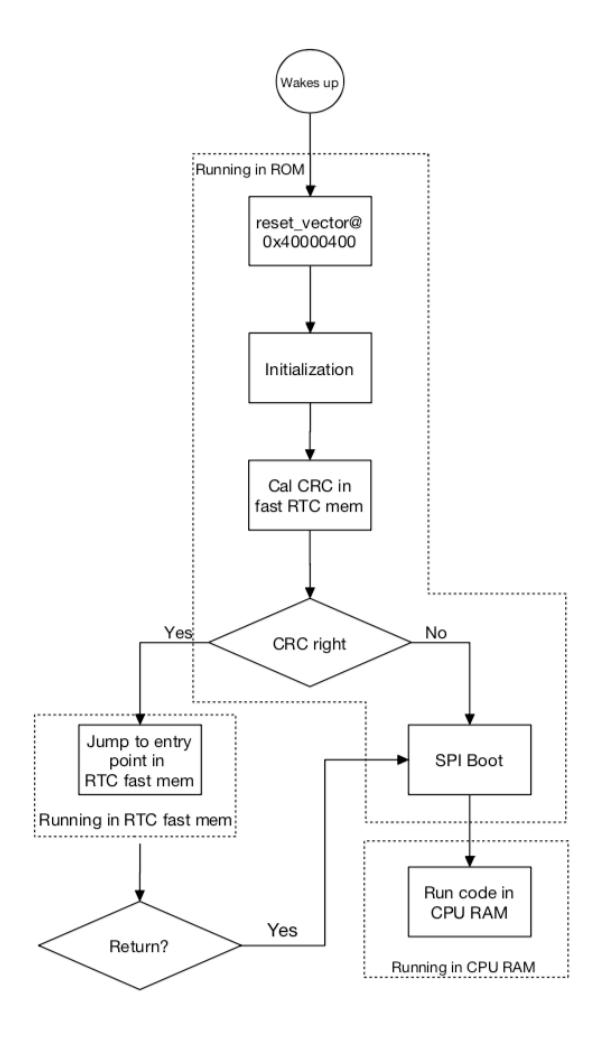

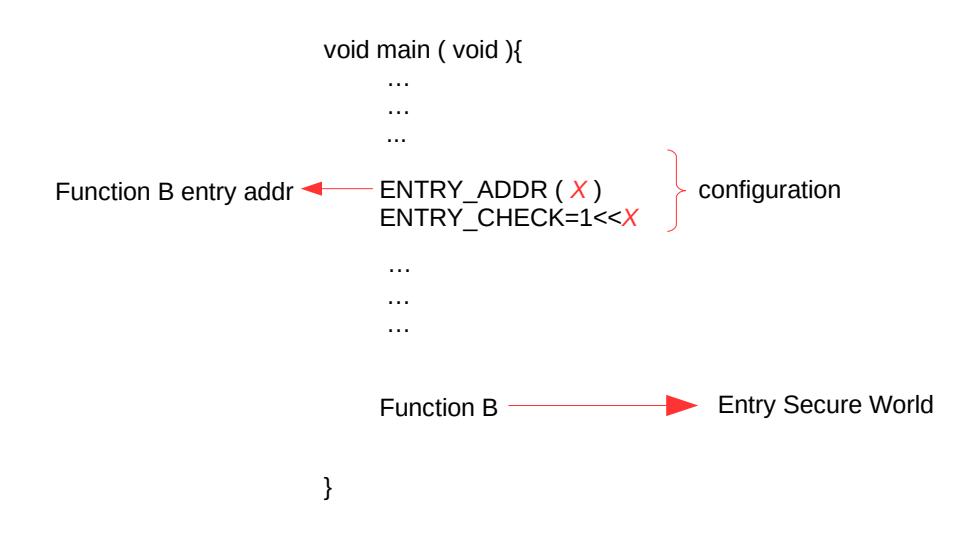

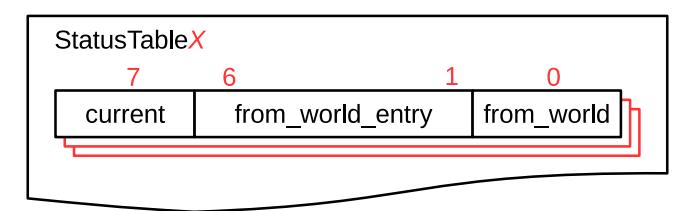

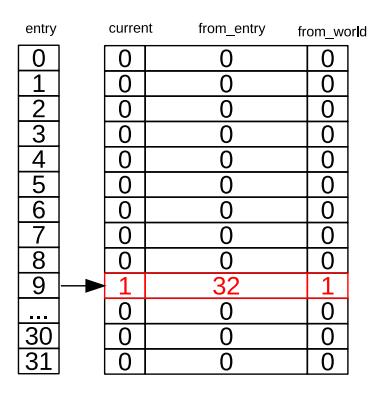

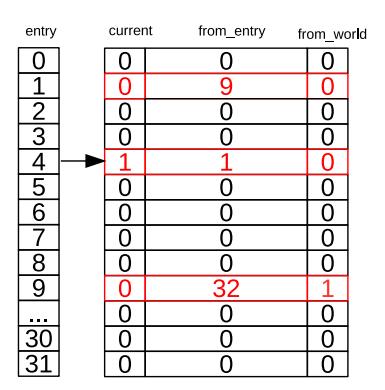

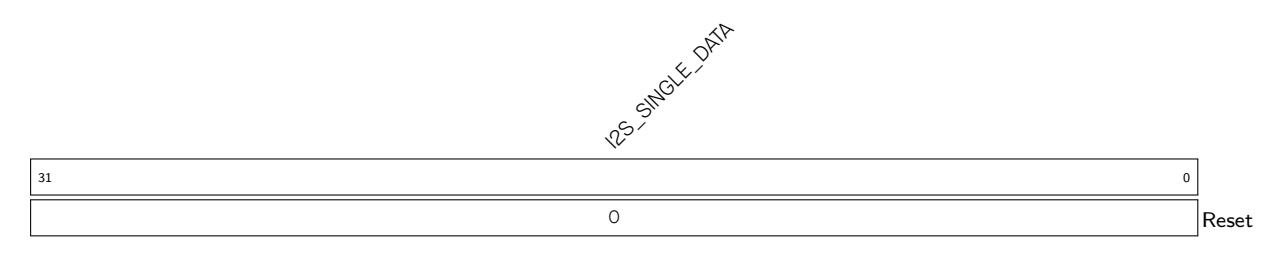

To choose a particular trigger unit write the index (0-7) of that unit into tselect CSR. When t select is written with a valid in dex, the ab stract CSRs tdata1 and tdata2 are automatically mapped to reflect internal registers of that trigger unit. Each trigger unit has two internal registers, namely mcontrol and maddress, which are mapped to tdata1 and tdata2, respectively.