DW3000 USER MANUAL

HOW TO USE, CONFIGURE AND CONTROL THE DW3000 UWB TRANSCEIVER

This document is subject to change without notice

| LIST OF FIGURES 4 | ||||||

|---|---|---|---|---|---|---|

| LIST OF TABLES 5 | ||||||

| 1 | INTRODUCTION 7 | |||||

| 1.1 | ABOUT THE DW3000 7 | |||||

| 1.2 | ABOUT THIS DOCUMENT 8 | |||||

| 2 | OVERVIEW OF THE DW300010 | |||||

| 2.1 | INTRODUCTION 10 | |||||

| 2.2 | COMPARISON AND COMPATIBILITY WITH DW1000 | |||||

| 10 | ||||||

| 2.3 | INTERFACING TO THE DW3000 11 | |||||

| 2.4 | DW3000 OPERATIONAL STATES 18 | |||||

| 2.5 | POWER ON RESET (POR) 21 | |||||

| 2.6 | UWB CHANNELS AND PREAMBLE CODES 28 | |||||

| 2.7 | DATA MODULATION SCHEME 28 | |||||

| 2.8 | SYNCHRONISATION HEADER MODULATION SCHEME29 | |||||

| 2.9 | PHY HEADER: STANDARD DATA FRAME LENGTH 30 | |||||

| 2.10 | EXTENDED PHY HEADER: EXTENDED DATA FRAME | |||||

| LENGTH | 31 | |||||

| 3 | MESSAGE TRANSMISSION33 | |||||

| 3.1 | BASIC TRANSMISSION 33 | |||||

| 3.2 | TRANSMISSION TIMESTAMP 34 | |||||

| 3.3 | DELAYED TRANSMISSION 35 | |||||

| 3.4 | EXTENDED LENGTH DATA FRAMES 36 | |||||

| 4 | MESSAGE RECEPTION38 | |||||

| 4.1 | PHY RECEPTION 38 | |||||

| 4.2 | TDOA AND PDOA SUPPORT 41 | |||||

| 4.3 | DELAYED RECEIVE 41 | |||||

| 4.4 | DOUBLE RECEIVE BUFFER 42 | |||||

| 4.5 | LOW-POWER SNIFF MODE 45 | |||||

| 4.6 | DIAGNOSTICS 46 | |||||

| 4.7 | ASSESSING THE QUALITY OF RECEPTION AND THE RX | |||||

| TIMESTAMP 47 | ||||||

| 5 | MEDIA ACCESS CONTROL (MAC) HARDWARE | |||||

| FEATURES 50 | ||||||

| 5.1 | MAC LEVEL PROCESSING IN THE DW3000 50 | |||||

| 5.2 | GENERAL MAC MESSAGE FORMAT 50 | |||||

| 5.3 | CYCLIC REDUNDANCY CHECK 51 | |||||

| 5.4 | FRAME FILTERING 51 | |||||

| 5.5 | AUTOMATIC ACKNOWLEDGEMENT 53 | |||||

| 5.6 | TRANSMIT AND AUTOMATICALLY WAIT FOR RESPONSE | |||||

| 55 | ||||||

| 5.7 | PSEUDO CLEAR CHANNEL ASSESSMENT (CCA) | |||||

| MECHANISM 55 | ||||||

|

SECURE RANGING / TIMESTAMPING62

OTHER FEATURES OF THE IC 66 EXTERNAL SYNCHRONISATION 66 EXTERNAL POWER AMPLIFICATION 67 USING THE ON-CHIP OTP MEMORY 67 MEASURING IC TEMPERATURE AND VOLTAGE 70 THE BROWNOUT DETECTOR 70 THE DW3000 REGISTER SET 71 REGISTER MAP OVERVIEW 71 DETAILED REGISTER DESCRIPTION 72 FAST COMMANDS 238 CMD_TXRXOFF 238 CMD_TX 239 CMD_RX 239 CMD_DTX 239 CMD_DRX 240 CMD_DTX_TS 240 |

|---|

| CMD_DRX_TS 240 |

| CMD_DTX_RS 241 |

| CMD_DRX_RS 241 |

| CMD_DTX_REF 241 |

| CMD_DRX_REF 241 |

| CMD_CCA_TX 241 |

| CMD_TX_W4R 241 |

| CMD_DTX_W4R 241 |

| CMD_DTX_TS_W4R 242 |

| CMD_DTX_RS_W4R 242 |

| CMD_DTX_REF_W4R 242 |

| CMD_CCA_TX_W4R 242 |

| CMD_CLR_IRQS 242 |

| CMD_DB_TOGGLE 242 |

| CALIBRATION 243 |

| IC CALIBRATION – CRYSTAL OSCILLATOR TRIM 243 |

| IC CALIBRATION – TRANSMIT POWER AND SPECTRUM |

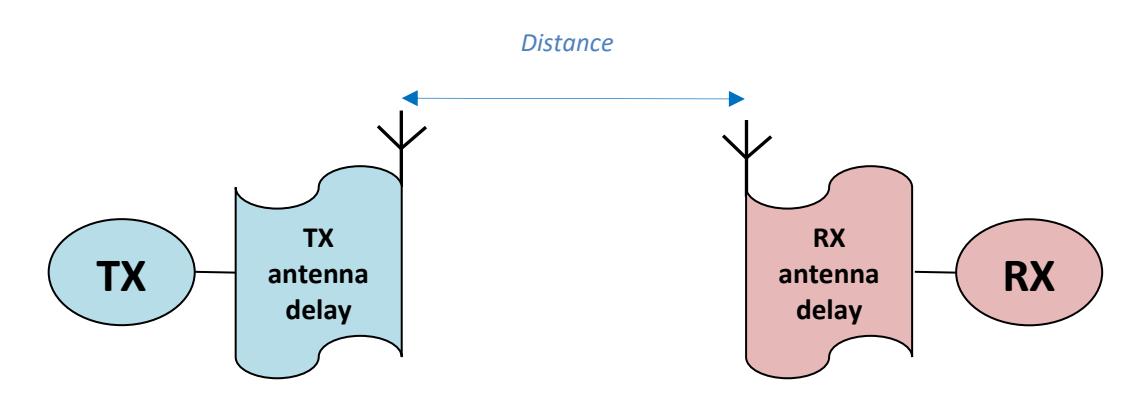

| IC CALIBRATION – ANTENNA DELAY 244 |

| TEMPERATURE 245 |

| LOCATION SCHEMES246 |

| APPENDIX 1: TWO-WAY RANGING 248 |

| INTRODUCTION 248 |

| 12.3 | DOUBLE-SIDED TWO-WAY RANGING 249 | ||

|---|---|---|---|

| 13 | APPENDIX 2: ABBREVIATIONS AND ACRONYMS | ||

| 251 | |||

| 14 | APPENDIX 3: REFERENCES 254 | ||

| 15 | DOCUMENT HISTORY 254 | ||

ABOUT DECAWAVE ........................................255

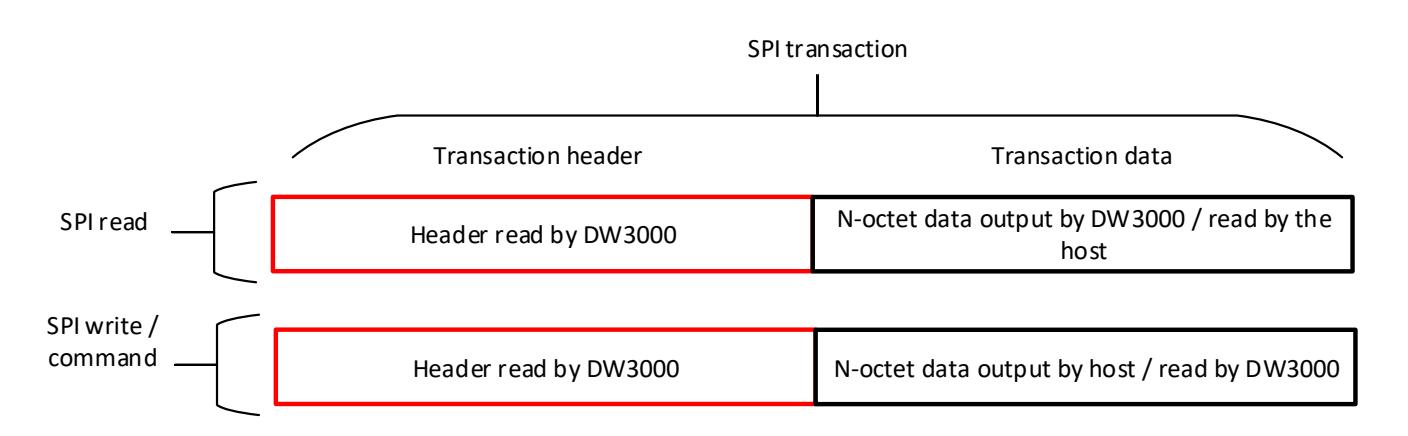

| FIGURE 1: SPI TRANSACTION HEADER AND TRANSACTION DATA 12 |

|---|

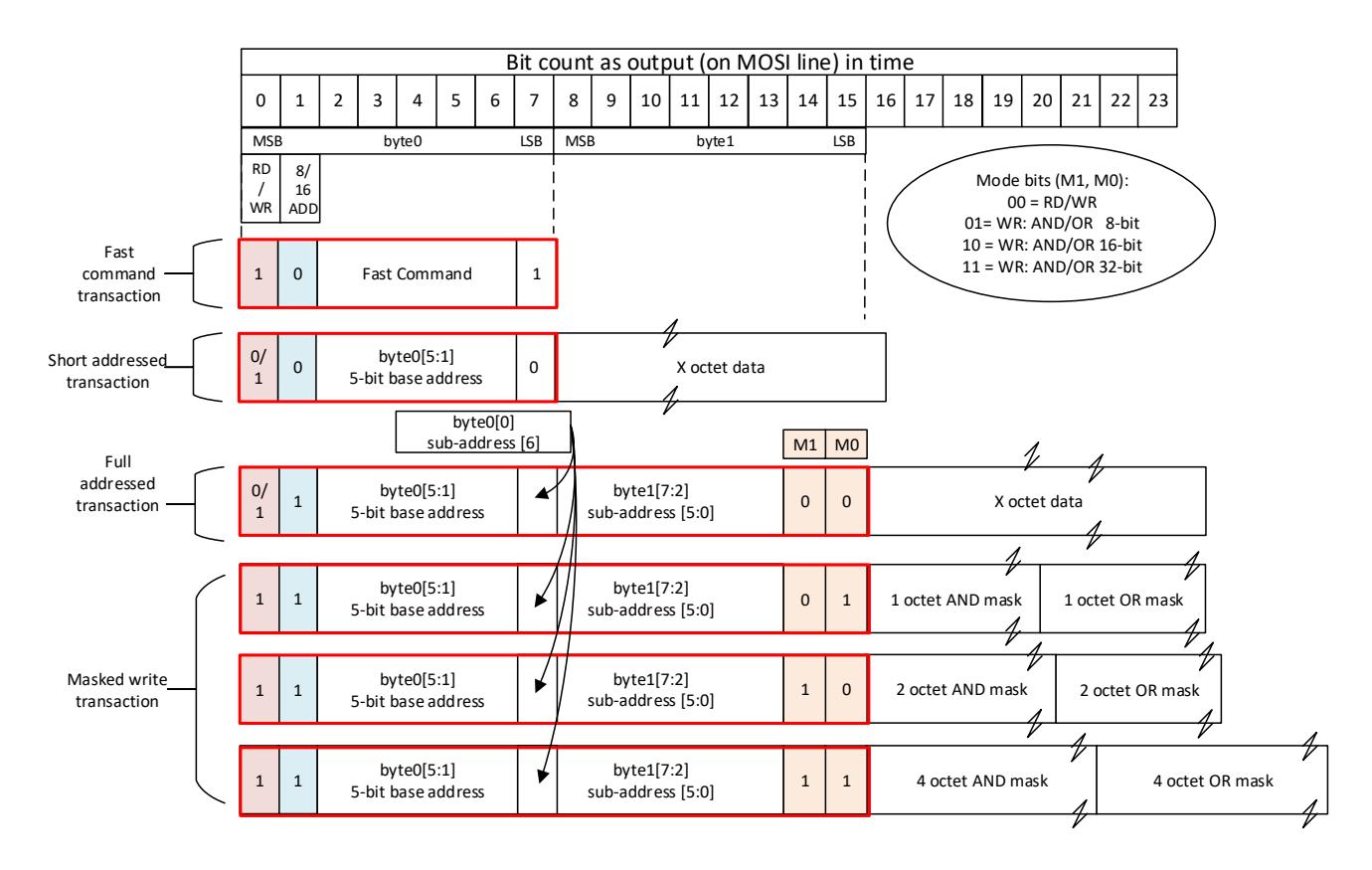

| FIGURE 2: SPI COMMAND FORMATTING 13 |

| FIGURE 3: SINGLE OCTET FAST COMMAND (START TX) SPI |

| TRANSACTION 14 |

| FIGURE 4: READING FIRST OCTET FROM DEV_ID REGISTER OF THE |

| IC 14 |

| FIGURE 5: WRITING TWO OCTETS TO REGISTER 0X2 SUBADDRESS |

| 0X1C 15 |

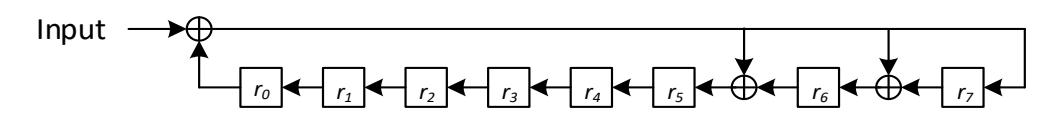

| FIGURE 6: SPI CRC POLYNOMIAL IMPLEMENTATION 16 |

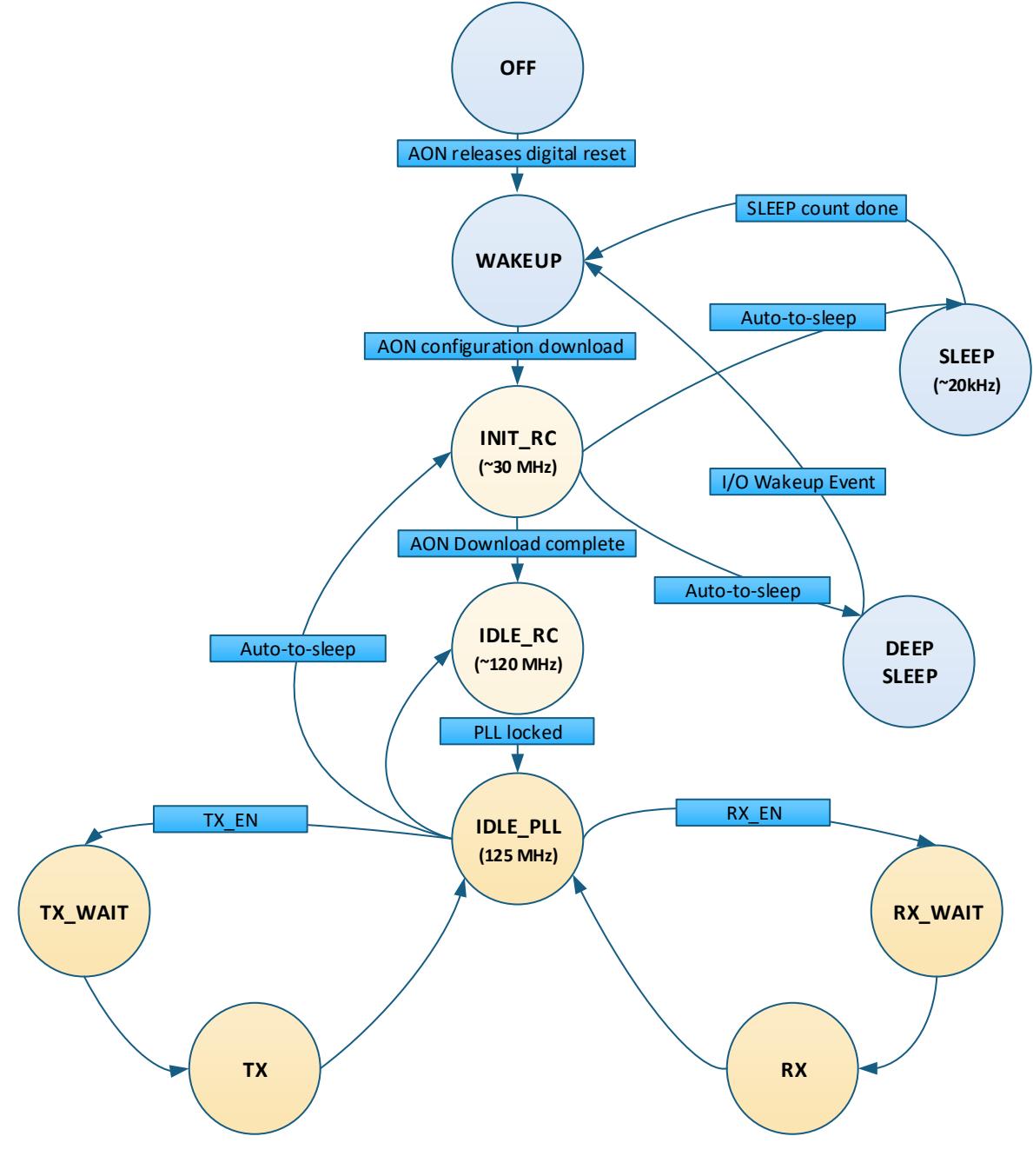

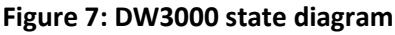

| FIGURE 7: DW3000 STATE DIAGRAM 18 |

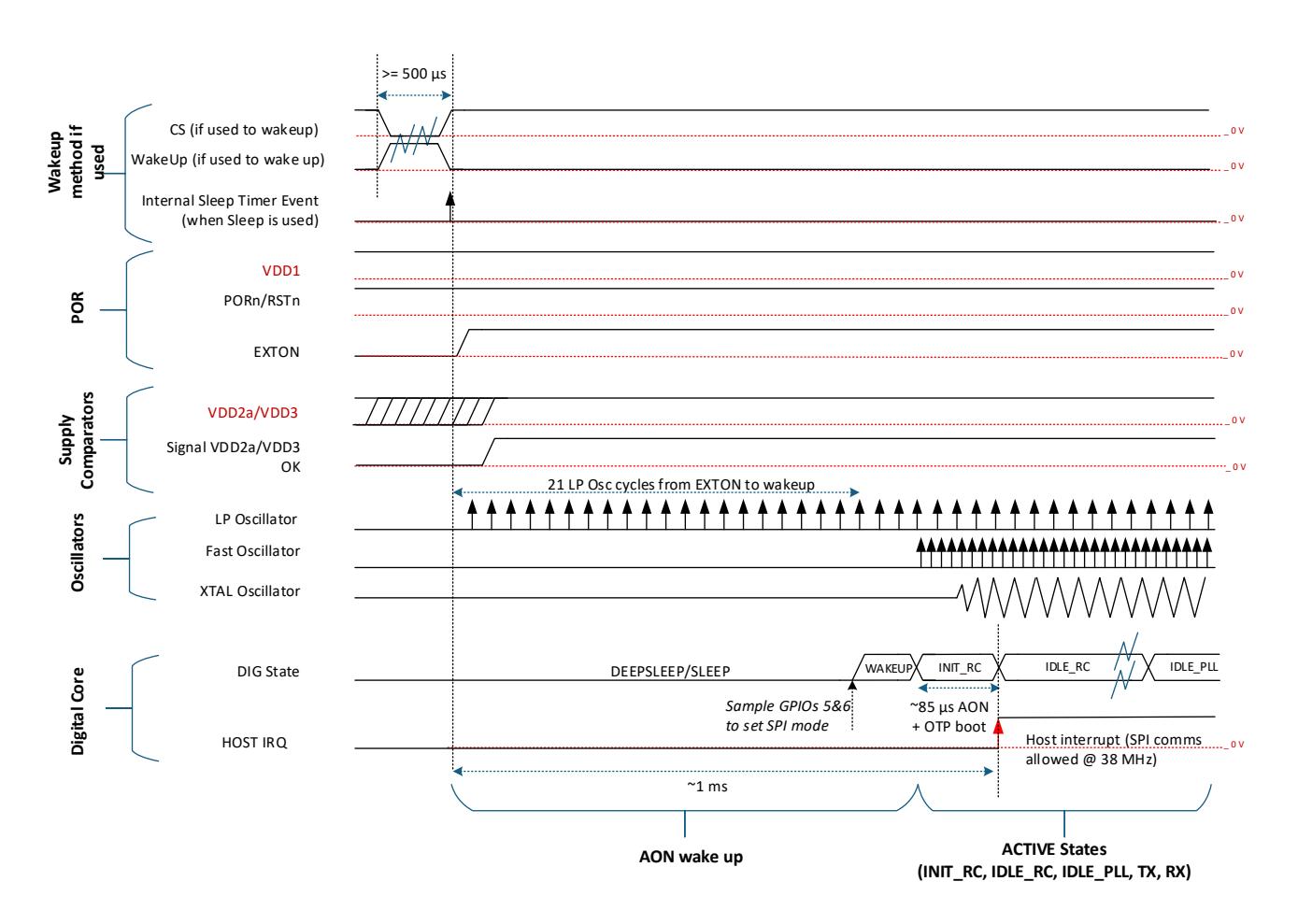

| FIGURE 8: TIMING DIAGRAM FOR COLD START POR 22 |

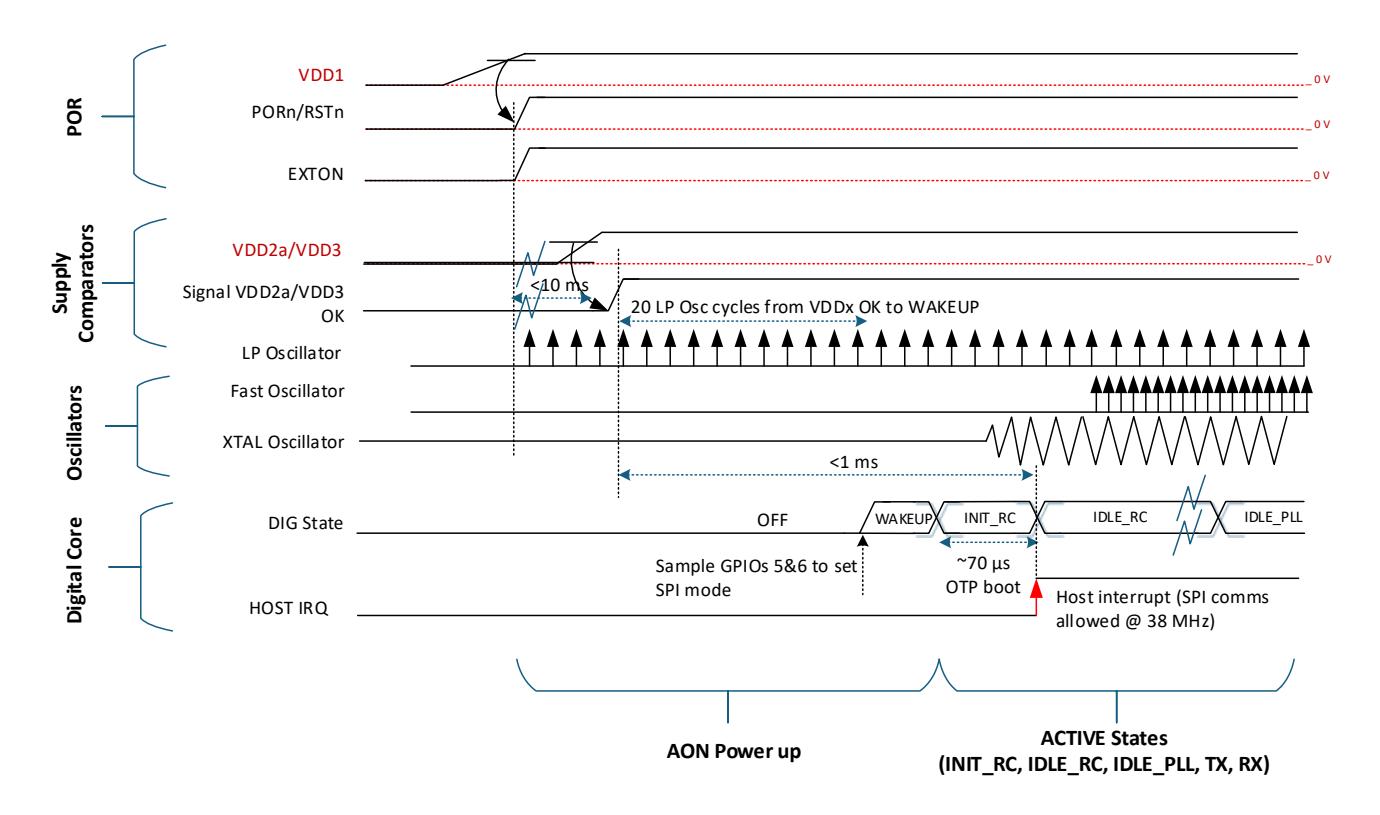

| FIGURE 9: TIMING DIAGRAM FOR WARM START (@ VDD = 3V)23 |

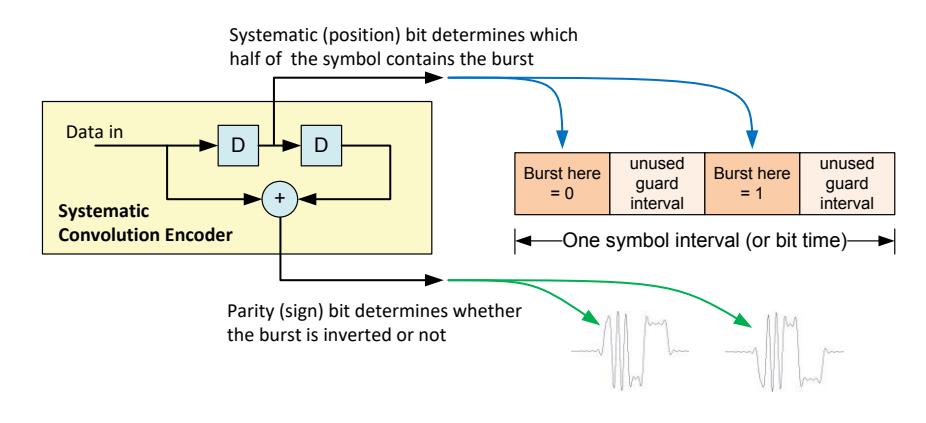

| FIGURE 10: BPM/BPSK DATA AND PHR MODULATION 29 |

| FIGURE 11: PHR BIT ASSIGNMENT 31 |

| FIGURE 12: PHR BIT ASSIGNMENT EXTENDED LENGTH FRAMES. 32 |

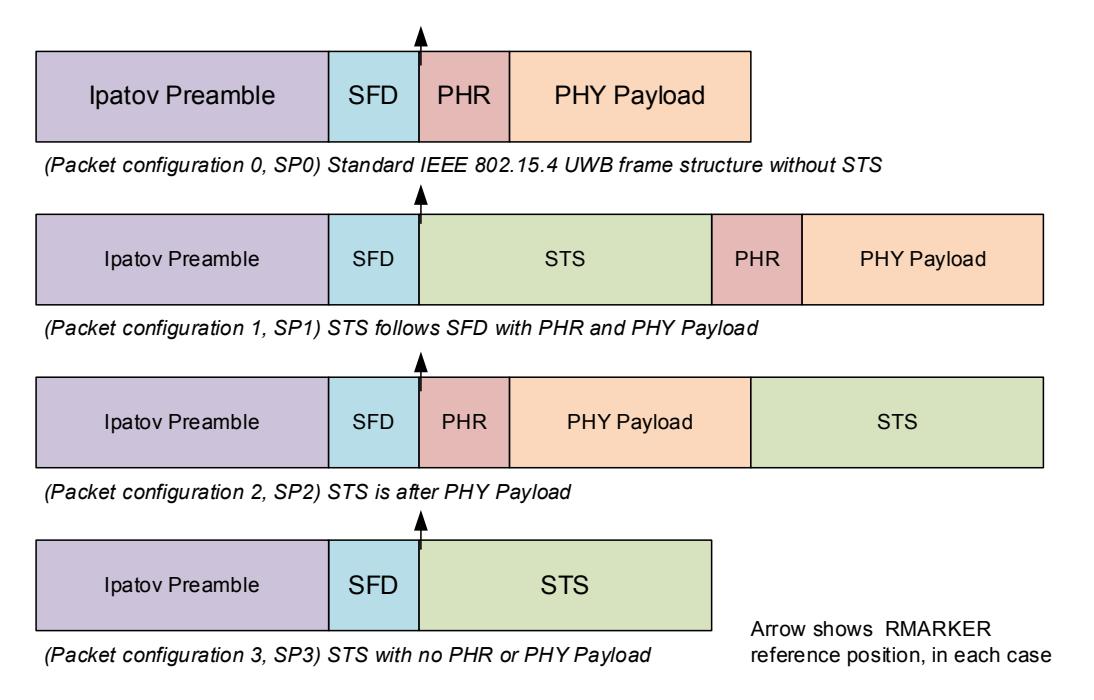

| FIGURE 13: PACKET FORMATS 33 |

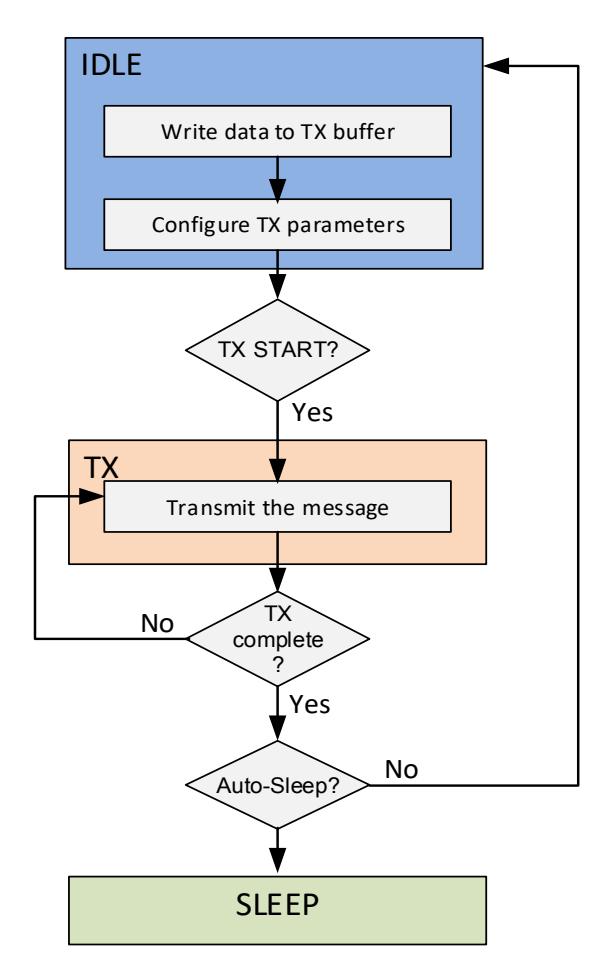

| FIGURE 14: BASIC TRANSMIT SEQUENCE 34 |

| FIGURE 14: PHR ENCODING EXTENDED LENGTH FRAMES 36 |

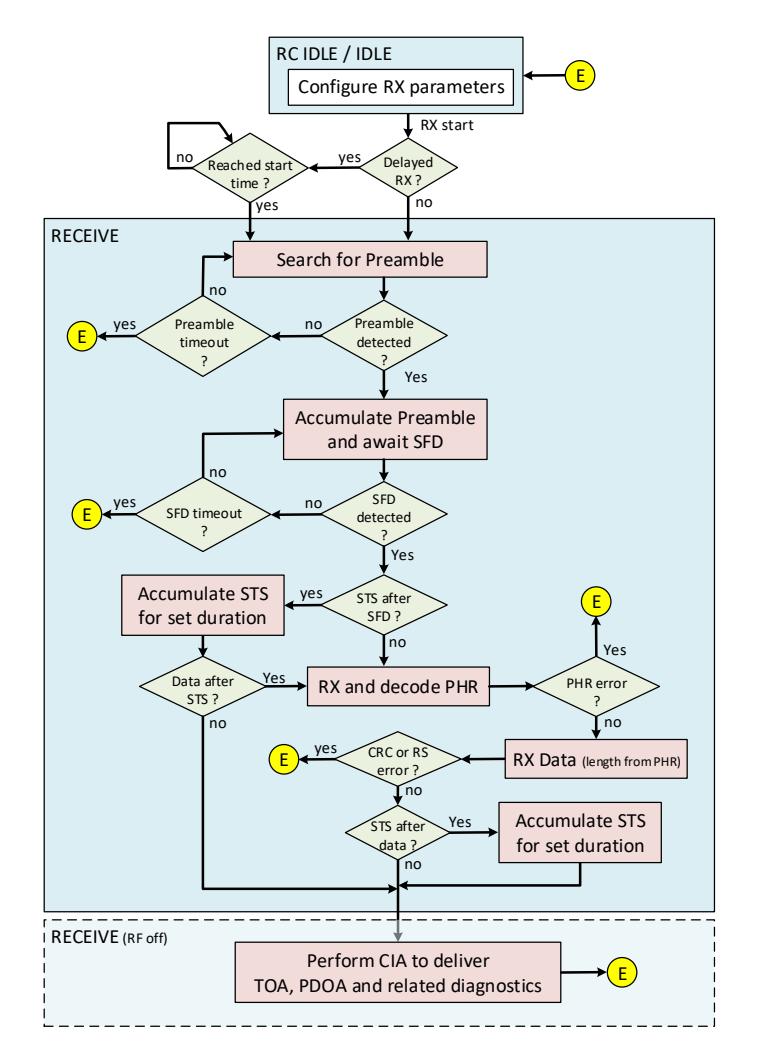

| FIGURE 15: RECEIVE SEQUENCE 38 |

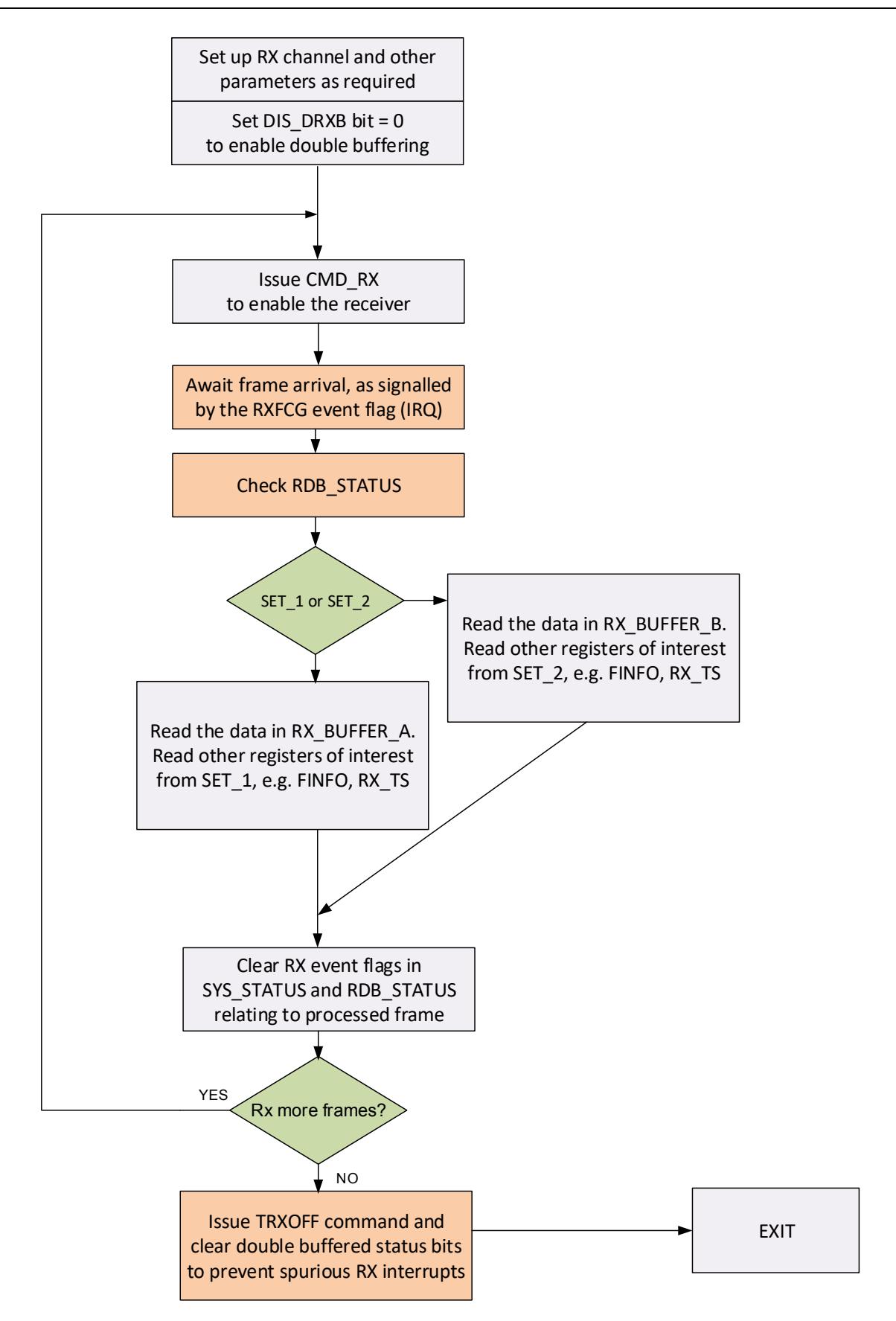

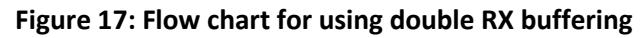

| FIGURE 16: FLOW CHART FOR USING DOUBLE RX BUFFERING 44 |

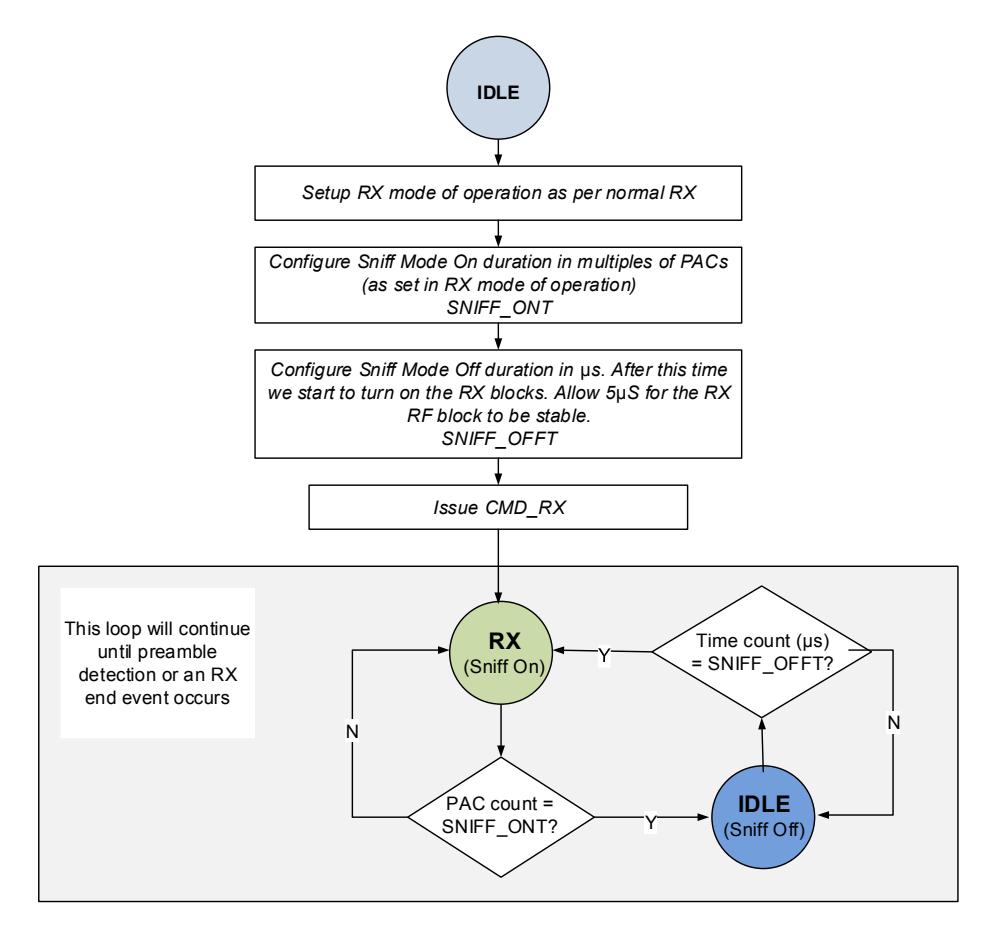

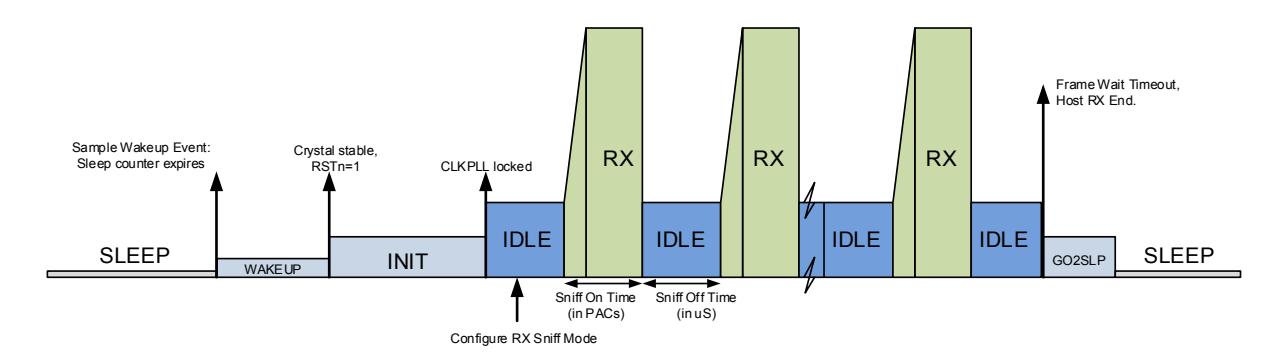

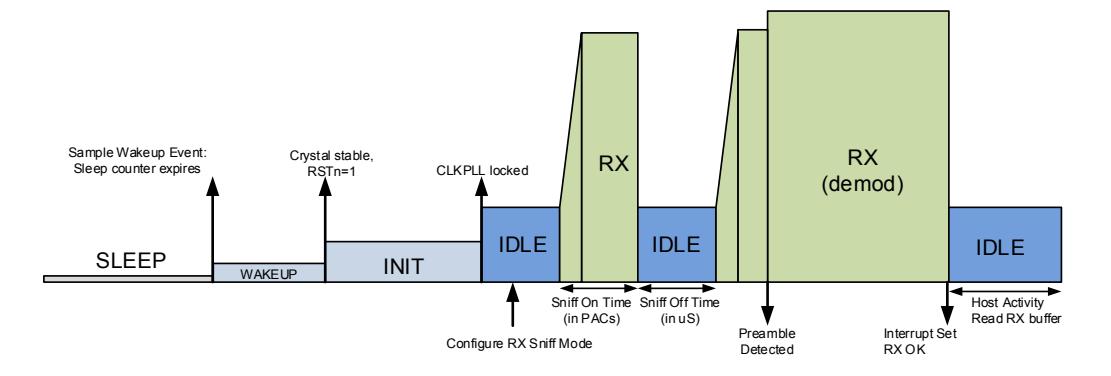

| FIGURE 17: STATE TRANSITIONS DURING SNIFF MODE 45 |

| FIGURE 18 POWER PROFILE FOR SNIFF WHERE A PACKET IS NOT |

| RECEIVED 46 |

| FIGURE 19 POWER PROFILE FOR SNIFF WHERE A PACKET IS |

| RECEIVED 46 |

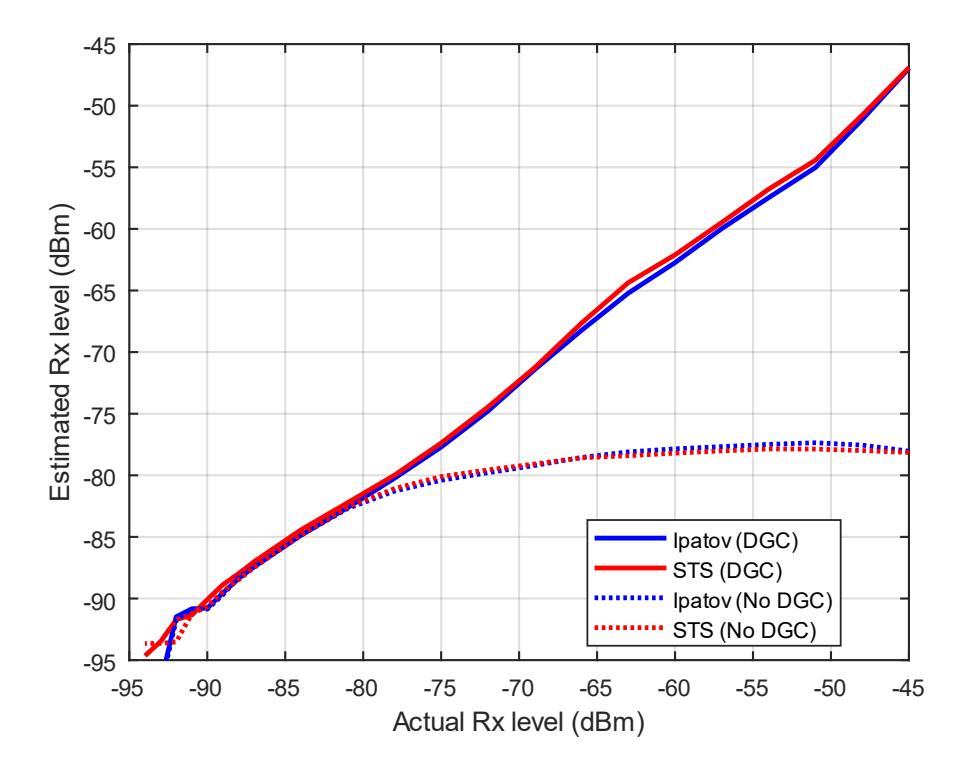

| FIGURE 20: ESTIMATED RX LEVEL VERSUS ACTUAL RX LEVEL 49 |

|---|

| FIGURE 21: GENERAL MAC MESSAGE FORMAT 51 |

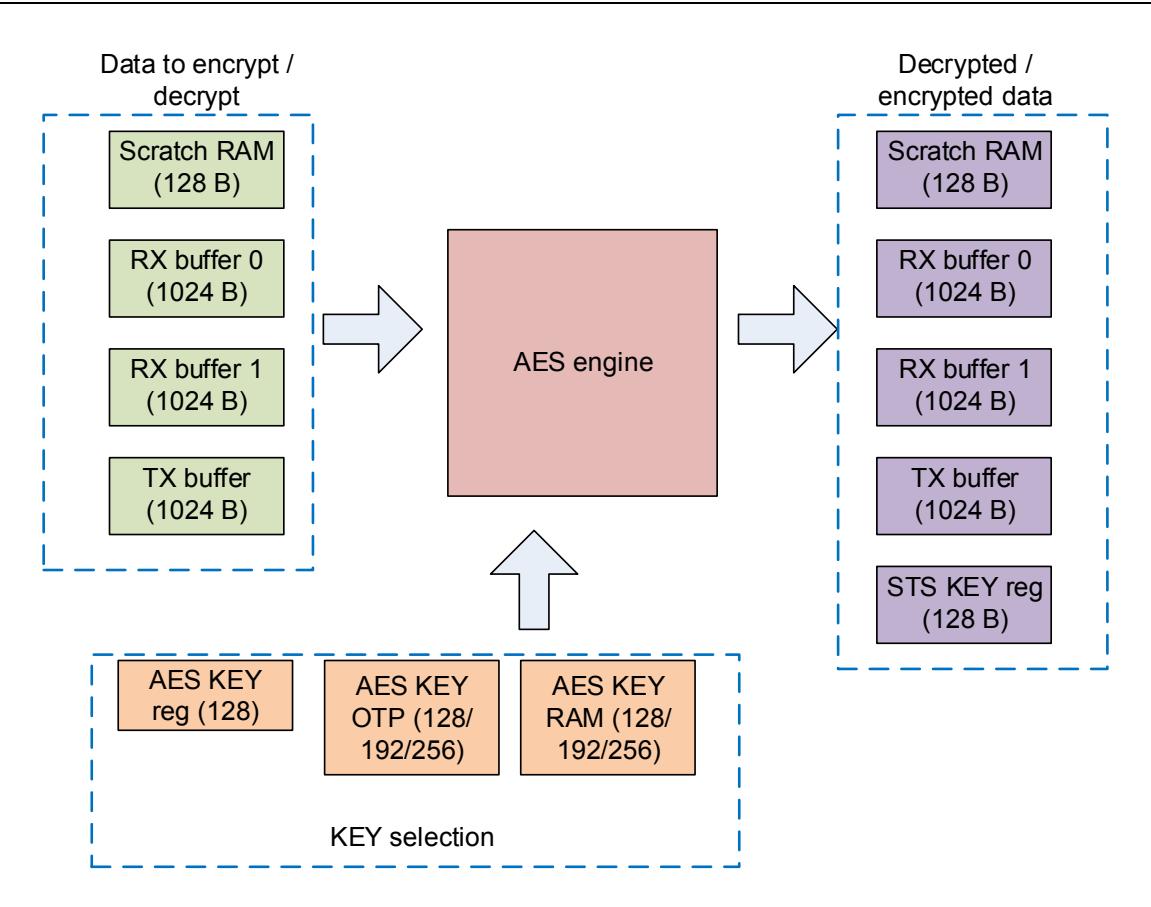

| FIGURE 22: AES ENGINE SOURCE/DESTINATION BUFFERS 57 |

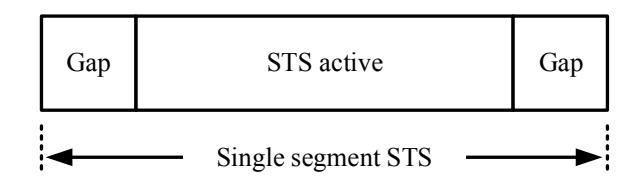

| FIGURE 23: STS STRUCTURE 62 |

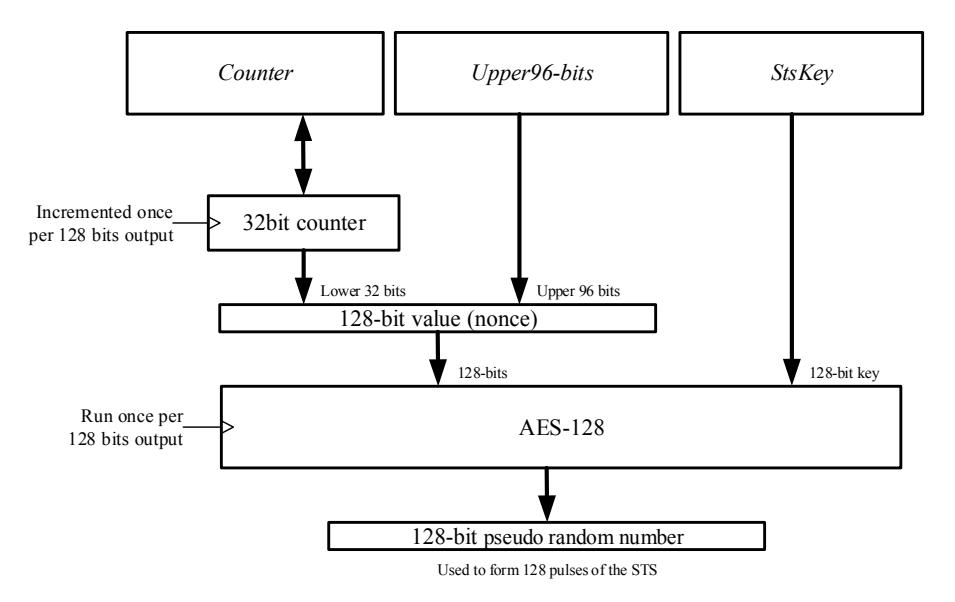

| FIGURE 24: AES IN COUNTER MODE BASED CPRNG 64 |

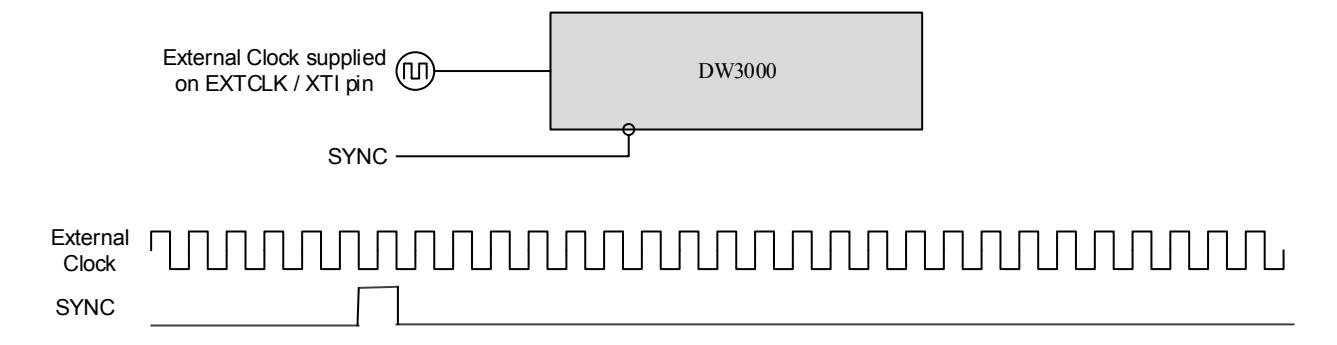

| FIGURE 25: DW3000 EXTERNAL SYNCHRONISATION INTERFACE |

| 66 |

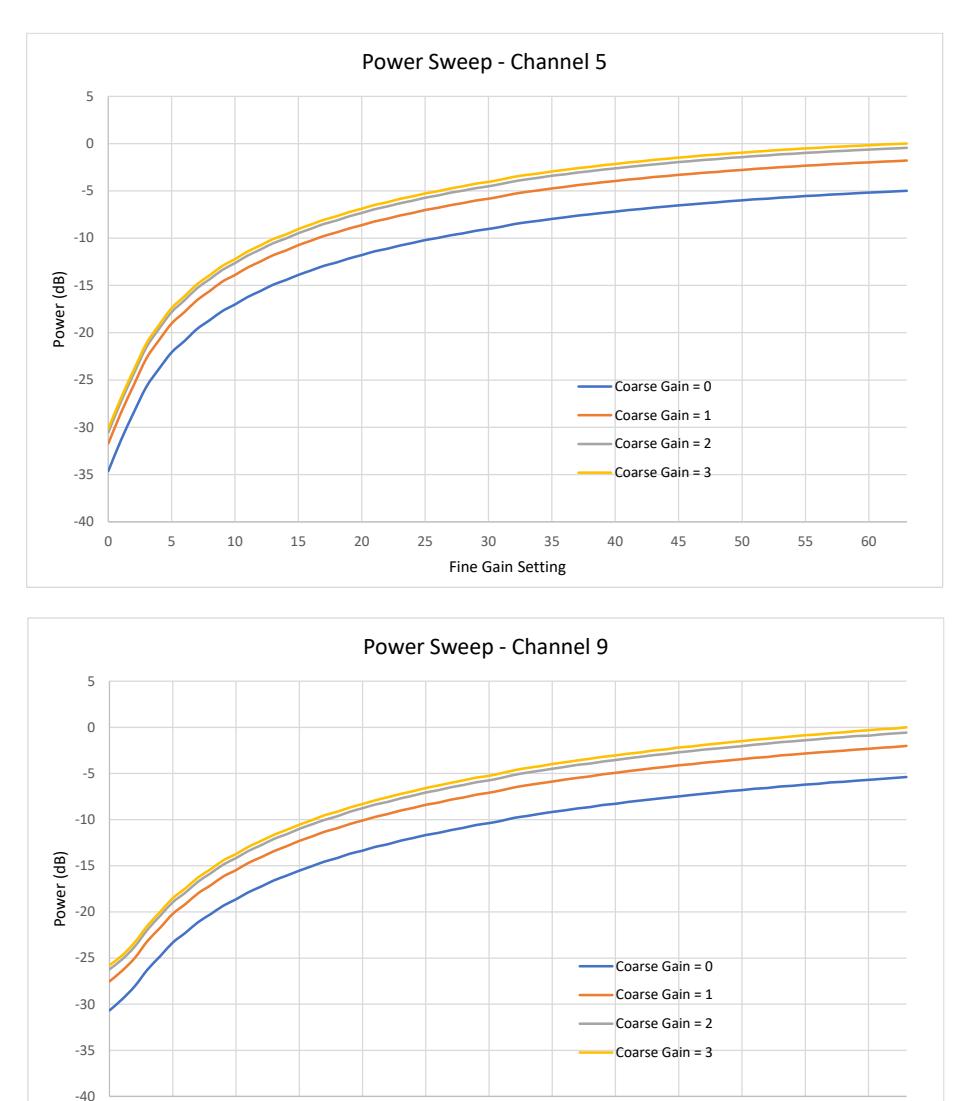

| FIGURE 26: TYPICAL TX POWER VARIATION WITH COARSE AND |

| FINE GAIN 109 |

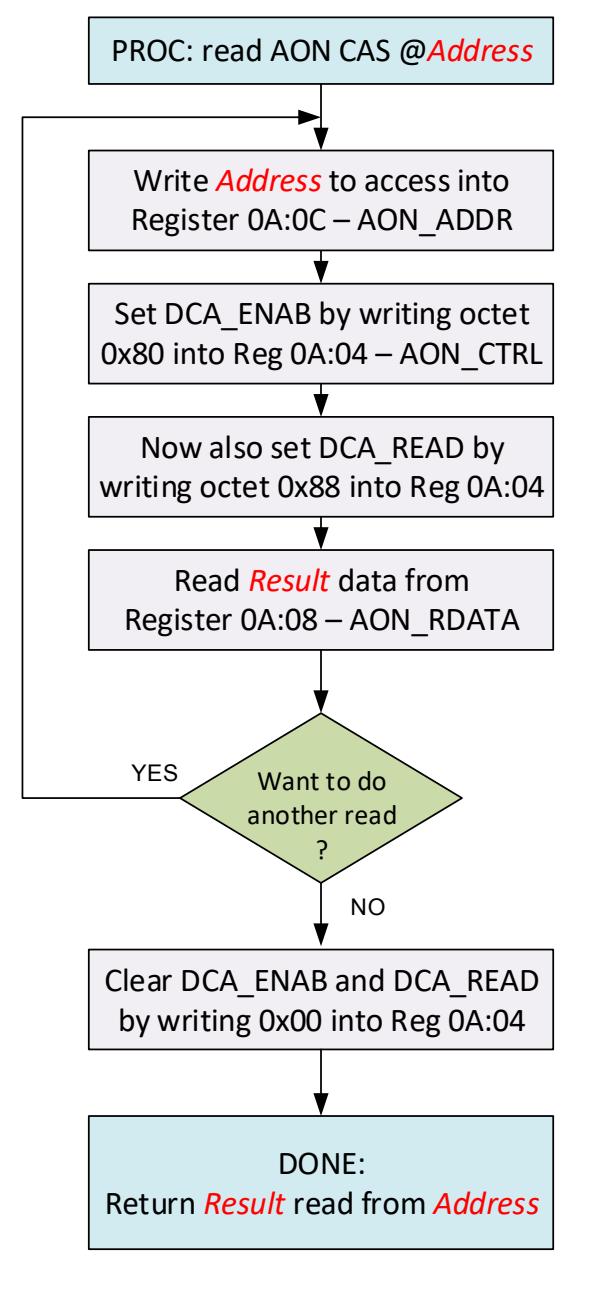

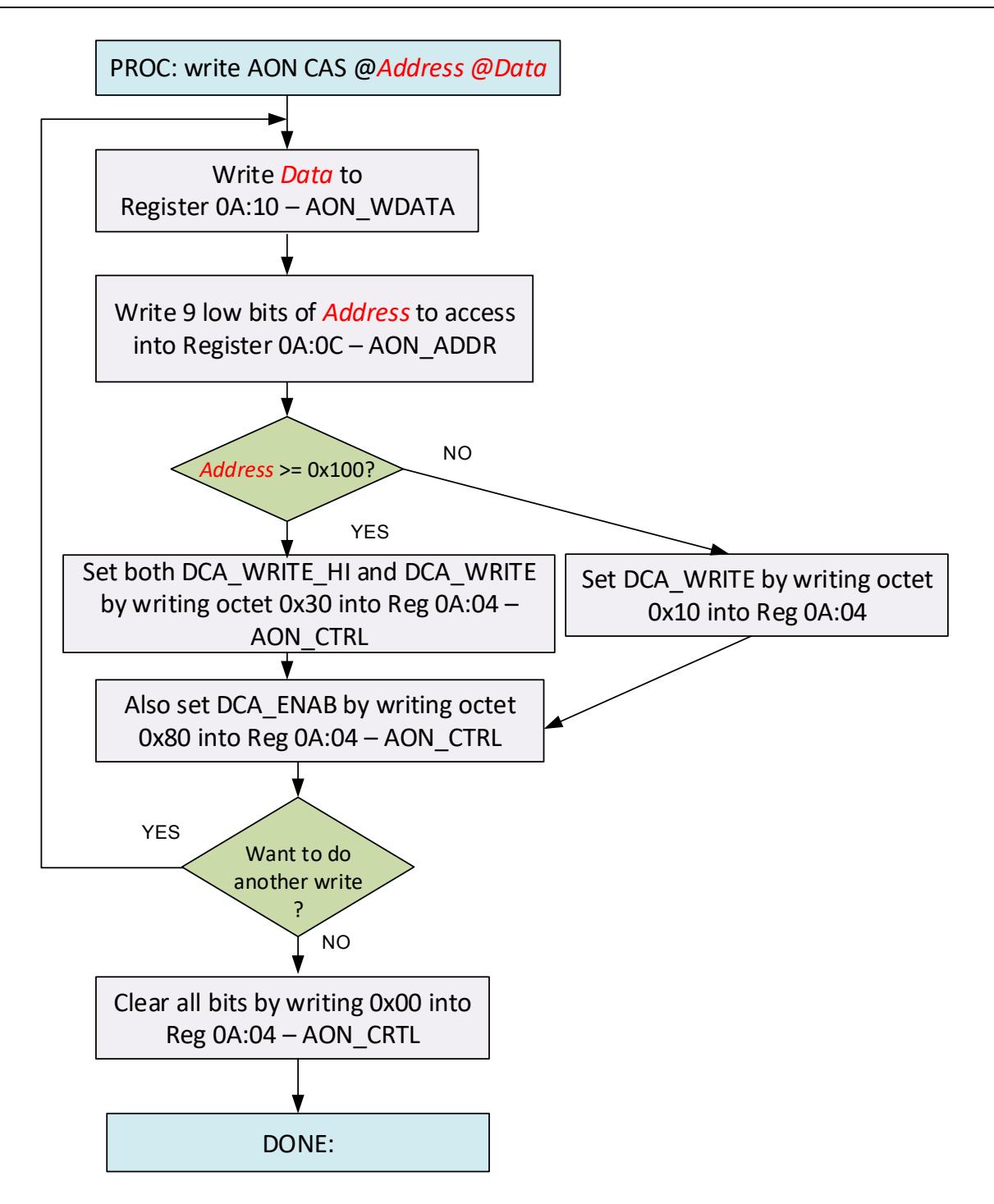

| FIGURE 27: FLOW CHART FOR DIRECT READ OF AON ADDRESS169 |

| FIGURE 28: FLOW CHART FOR DIRECT WRITE OF AON ADDRESS |

| 171 |

| FIGURE 29: TRANSMIT AND RECEIVE ANTENNA DELAY 245 |

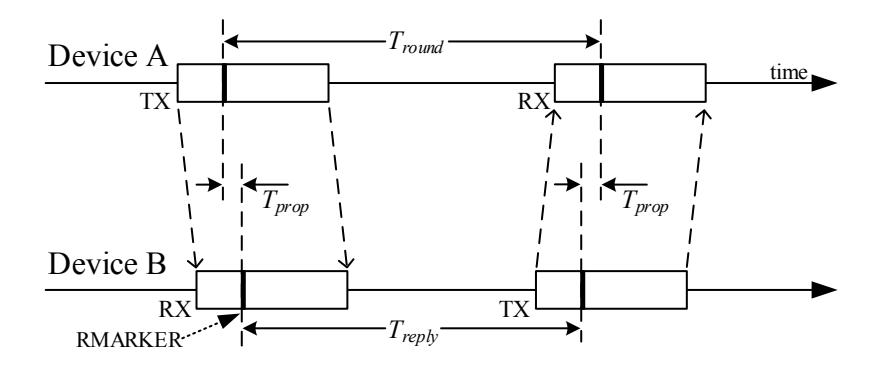

| FIGURE 30: SINGLE-SIDED TWO-WAY RANGING 248 |

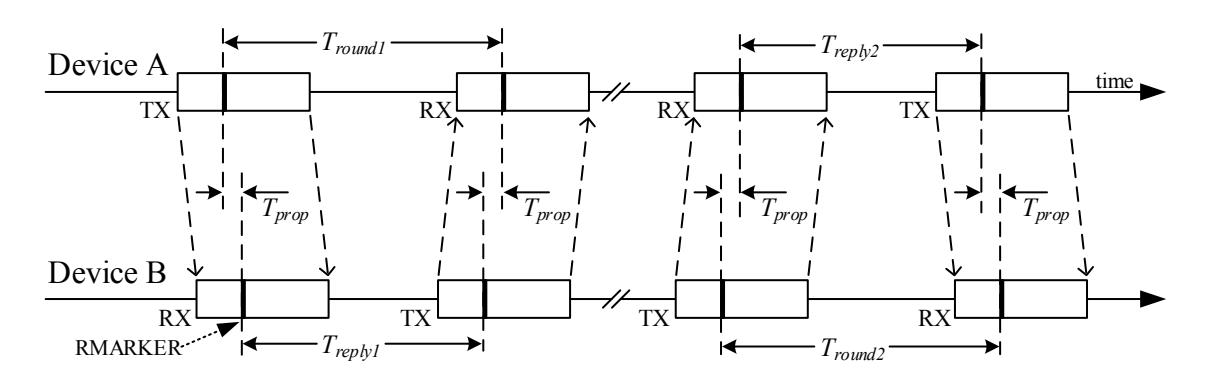

| FIGURE 31: DOUBLE-SIDED TWO-WAY RANGING WITH FOUR |

| MESSAGES 249 |

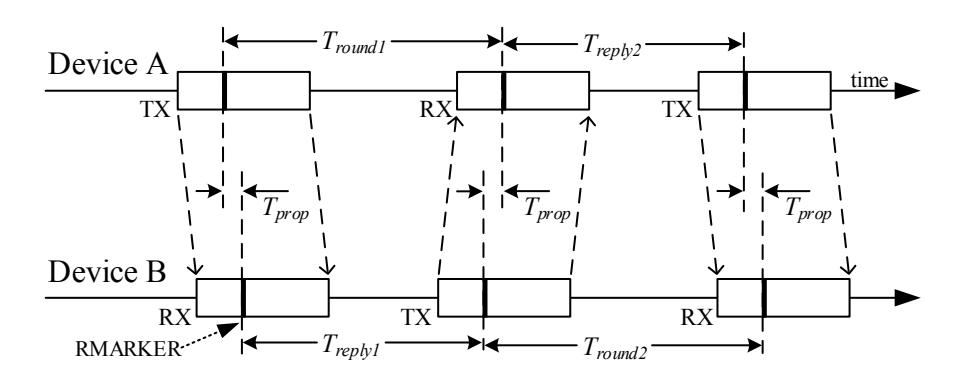

| FIGURE 32: DOUBLE-SIDED TWO-WAY RANGING WITH THREE |

| MESSAGES 249 |

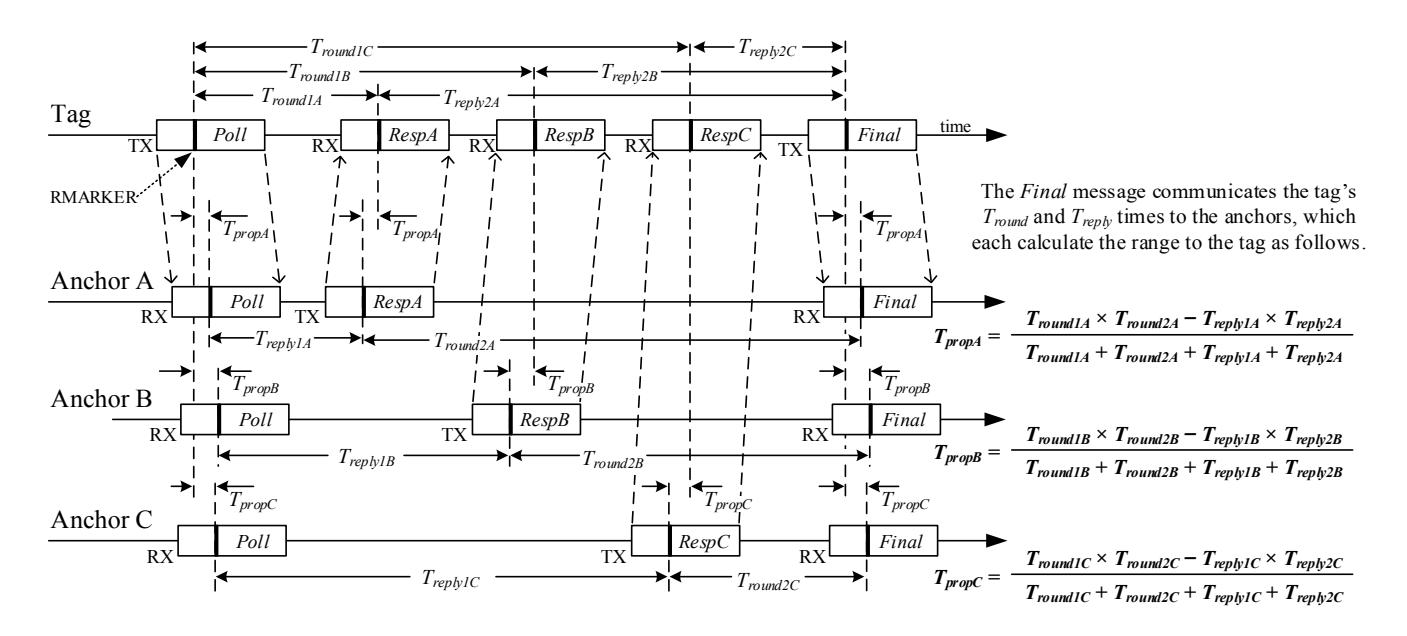

| FIGURE 33: RANGING TO 3 ANCHORS WITH JUST 5 MESSAGES |

| WHERE EACH ANCHOR CALCULATES ITS OWN RANGE RESULT |

| 250 |

| TABLE 1: DW3000 VARIANTS 7 |

|---|

| TABLE 2: BRIEF DESCRIPTION OF DOCUMENT SECTIONS 8 |

| TABLE 3: SPI TRANSACTION TYPES 12 |

| TABLE 4: MAIN DW3000 OPERATIONAL STATES / MODES 19 |

| TABLE 5: CONFIGURATIONS MAINTAINED IN THE AON MEMORY |

| ARRAY 25 |

| TABLE 6: DEFAULT DW3000 OPERATIONAL CONFIGURATION 26 |

| TABLE 7: GPIO DEFAULT FUNCTIONS 27 |

| TABLE 8: DW3000 SUPPORTED UWB CHANNELS AND |

| RECOMMENDED PREAMBLE CODES 28 |

| TABLE 9: PREAMBLE PARAMETERS 30 |

| TABLE 10: PREAMBLE DURATION FIELD VALUES IN EXTENDED |

| LENGTH FRAME PHR 32 |

| TABLE 9: PREAMBLE DURATION FIELD VALUES IN EXTENDED |

| LENGTH FRAME PHR 37 |

| TABLE 11: RECOMMENDED PAC SIZE 39 |

| TABLE 12: FRAME TYPE FIELD VALUES 51 |

| TABLE 13: DECRYPTED STS KEY BYTES (WITH BIG ENDIAN |

| FORMAT) 59 |

| TABLE 14: DECRYPTED STS KEY BYTES (WITH LITTLE ENDIAN |

| FORMAT) 60 |

| TABLE 15: DECRYPTED STS KEY BYTES (WITH LITTLE ENDIAN |

| FORMAT AND SWAPPED BY SE PRIOR TO ENCYPTION) 60 |

| TABLE 16: OTP MEMORY MAP 68 |

| TABLE 17: REGISTER MAP OVERVIEW 71 |

| TABLE 18: REGISTER FILE: 0X00-0X1 – GENERAL CONFIGURATION |

| REGISTERS OVERVIEW 73 |

| TABLE 19: PREAMBLE LENGTH SELECTION 86 |

| TABLE 20: PREAMBLE LENGTH REPORTING 101 |

| TABLE 21: SFD TYPES 110 |

| TABLE 22: REGISTER FILE: 0X02 – STS CONFIGURATION AND |

| STATUS OVERVIEW 123 |

| TABLE 23: RECEIVER TUNING PARAMETERS 126 |

| TABLE 24: REGISTER FILE: 0X05 – GPIO CONTROL AND STATUS |

| OVERVIEW 130 |

| TABLE 25: REGISTER FILE: 0X06 – DIGITAL RECEIVER |

| CONFIGURATION OVERVIEW 145 |

| TABLE 26: CONSTANTS FOR FREQUENCY OFFSET CALCULATION 149 |

| TABLE 27: REGISTER FILE: 0X07 – ANALOG RF CONFIGURATION |

| BLOCK OVERVIEW 149 |

| TABLE 28: RF_ENABLE AND RF_CTRL_MASK VALUES 150 |

| TABLE 29: RF_TX_CTRL_2 VALUES 152 |

| TABLE 30: PG_DELAY RECOMMENDED VALUES 152 |

|

TABLE 31: REGISTER FILE: 0X08 – TRANSMITTER CALIBRATION

BLOCK OVERVIEW 156 |

| TABLE 32: SUB-REGISTER 0X08:18 – PG TEST VALUES 161 |

|---|

| TABLE 33: REGISTER FILE: 0X09 – FREQUENCY SYNTHESISER |

| CONTROL BLOCK OVERVIEW 162 |

| TABLE 34: REFERENCE VALUES SUB-REGISTER 0X09:00 – PLL |

| CONFIGURATION 163 |

| TABLE 35: REGISTER FILE: 0X0A – ALWAYS-ON SYSTEM CONTROL |

| OVERVIEW 165 |

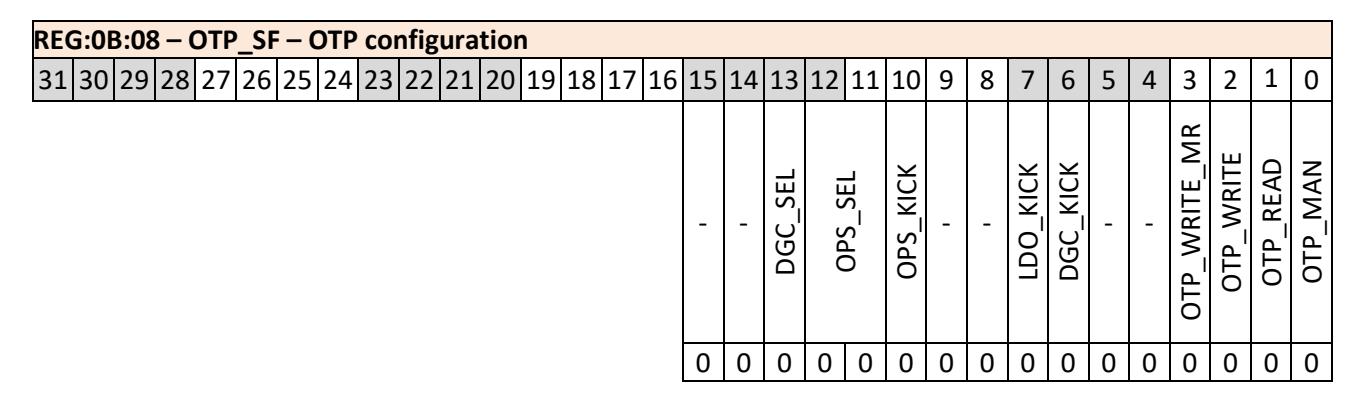

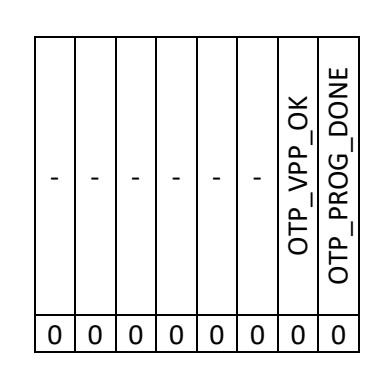

| TABLE 36: REGISTER FILE: 0X0B – OTP MEMORY INTERFACE |

| OVERVIEW 174 |

| TABLE 37: RECEIVER OPERATING PARAMETER SETS 178 |

| TABLE 38: REGISTER FILES: 0X0C, 0X0D, 0X0E – CIA INTERFACE |

| OVERVIEW 179 |

| TABLE 39: REGISTER FILE: 0X0F – DIGITAL DIAGNOSTICS |

| INTERFACE OVERVIEW 205 |

| TABLE 40: REGISTER FILE: 0X11 – PMSC CONTROL AND STATUS |

| OVERVIEW 218 |

| TABLE 41: EXAMPLE SPI INDEXED READ OF ACCUMULATOR CIR |

| MEMORY 229 |

| TABLE 42: REGISTER FILE: 0X17 – AES KEY RAM OVERVIEW 230 |

| TABLE 43: REGISTER FILE: 0X18 – DOUBLE BUFFER DIAGNOSTIC |

| REGISTER SET OVERVIEW 231 |

| TABLE 44: REGISTER FILE: 0X1F – FINT STATUS AND INDIRECT |

| POINTER INTERFACE OVERVIEW 233 |

| TABLE 45: LIST OF SUPPORTED FAST COMMANDS 238 |

| TABLE 46: DOCUMENT HISTORY 254 |

Decawave reserves the right to change product specifications without notice. As far as possible changes to functionality and specifications will be issued in product specific errata sheets or in new versions of this document. Customers are advised to check with Decawave for the most recent updates on this product.

Copyright © 2019 Decawave Ltd

Decawave products are not authorized for use in safety-critical applications (such as life support) where a failure of the Decawave product would reasonably be expected to cause severe personal injury or death. Decawave customers using or selling Decawave products in such a manner do so entirely at their own risk and agree to fully indemnify Decawave and its representatives against any damages arising out of the use of Decawave products in such safety-critical applications.

Caution! ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

The DW3000, as supplied from Decawave, has not been certified for use in any particular geographic region by the appropriate regulatory body governing radio emissions in that region although it is capable of such certification depending on the region and the manner in which it is used.

All products developed by the user incorporating the DW3000 must be approved by the relevant authority governing radio emissions in any given jurisdiction prior to the marketing or sale of such products in that jurisdiction and user bears all responsibility for obtaining such approval as needed from the appropriate authorities.

The DW3000 is a family of fully integrated low power, single chip CMOS radio transceivers IC implementing HRP UWB PHY as specified by the IEEE802.15.4 standard [1], including the BPRF mode specified by the IEEE802.15.4z amendment [2]. There are currently two versions a non-PDoA and an PDoA device with 0xDECA0302 and 0xDECA0312 device identifiers respectively.

| IC Variant | Type of package | PDoA support |

Operating

Temperature |

|---|---|---|---|

| DW3110 | WLCSP52 | No | |

| DW3120 | WLCSP52 | Yes | |

| DW3210 | QFN40 | No |

-40℃

to +85℃ |

| DW3220 | QFN40 | Yes |

This user manual describes the operation and programming of the DW3000 and discusses some of the design choices to be considered when implementing systems using it. Information already contained in the DW3000 Datasheet is not reproduced here and it is intended that the reader should use this user manual in conjunction with the DW3000 Datasheet. The document is divided into a number of sections each of which deals with a particular aspect of the DW3000 as follows: -

| Section | Section Name | Information covered |

|---|---|---|

| 2 | Overview of the DW3000 |

Gives an overview of the DW3000, describes how to

interface to the device and details its various operating modes |

| 3 | Message transmission | Describes the functionality and use of the transmitter |

| 4 | Message reception | Describes the functionality and use of the receiver |

| 5 |

Media Access Control (MAC)

hardware features |

Describes the MAC level functionality provided by the IC. |

| 6 | Secure ranging / timestamping | Describes the secure timestamping capability of the device |

| 7 | Other features of the IC | Describes other features supported by the device |

| 8 | The DW3000 register set |

Describes the register set in detail, lists all user accessible bit

fields in each register and their respective functions. |

| 9 | Fast Commands |

Describes the supported "fast commands". Single octet SPI

transaction command to place device into TX or RX. |

| 10 | Calibration |

Describes the parameters of the DW3000 that require

calibration; the methodology that should be used in calibrating them and how often they require calibration. |

| 11 | Location schemes |

Discusses some of the issues to be considered and trade-offs

to be made when building systems based on the DW3000 |

| 12 | APPENDIX 1: Two-way ranging |

Gives an introduction to the use of the DW3000 in two-way

ranging proximity systems |

| 13 |

APPENDIX 2: Abbreviations and

acronyms |

Provides a list and explanation of abbreviations and

acronyms used in the rest of the document |

| 14 | APPENDIX 3: References | Lists the documents referred to in this user manual |

| 15 | Document History | Gives the revision history of this document |

Decawave also provides DW3000 device driver software as source code. This source code includes a set of API functions to initialise, configure and control the DW3000. It provides API functions for transmission and reception, and for driving the functionalities of the IC. The DW3000 driver source code is targeted for the ARM Cortex-M but is readily portable to other microprocessor systems. The API code comes with a number of simple examples that exercise the API and show how to use various features of the DW3000, including an example of two-way ranging [3].

The DW3000 consists of an analog front-end (both RF and baseband) containing a receiver and transmitter and a digital back-end. The latter interfaces to a host processor, controls the analog front-end, accepts data from the host processor for transmission and provides received data to the host processor over an industry standard SPI interface.

The main differences to DW1000 are that the DW3000 has:

DW3000 is backwards compatible with DW1000 for a sub-set of use case configurations. As DW3000 has a reduced channel set, the only common channel is channel 5 (6.5 GHz). Both 16 and 64 MHz PRFs are supported as well as the 850 kb/s and 6.81 Mb/s data rates.

Although the DW3000 is operationally backwards compatible with DW1000 on channel 5, modified software is needed since the DW3000 control register interface is different to that of the DW1000. Decawave provides an easy-to adopt DW3000 device driver and API for backwards compatibilit y [3].

The DW3000 host communications interface is a slave-only Serial Peripheral Interface (SPI) compliant with the industry protocol. The host system must include a master SPI bus controller in order to communicate with the DW3000.

The host system controls the DW3000 via the SPI, reading and writing configuration and status registers, data buffers and issuing commands. This section describes the general format of the SPI transactions. For details of the SPI bus signals, their voltage levels, operational mode configuration and timing parameters please refer to the DW3000 Datasheet [5]. The SPI-accessible buffers and registers of the DW3000 are detailed in section 8 – The DW3000 register set , and the commands are detailed in section 9 – Fast Commands .

The operating mode of the SPI is determined when the DW3000 is initialised as a result of a device reset or is woken up from a sleep state. At this time GPIO lines 5 and 6 are sampled, (see Figure 8) , and their values used to select the SPI polarity and phase mode respectively. Please refer to the IC Datasheet [5] section "SPI Operating Modes" for details of the operation resulting from this.

It is possible to set the SPI mode within the DW3000's one-time programmable (OTP) configuration block to avoid needing any external components and leave the GPIO free for alternative use. This is a one-time activity and cannot be reversed thus care must be taken to ensure that the desired SPI mode is correctly set if this method is used. Please refer to section 7.3 – Using the on-chip OTP memory for more details of OTP configuration.

For full details of the SPI operating modes and their configuration, please refer to the DW3000 Datasheet.

Each SPI transaction starts with a one or two octet transaction header followed by a variable number of octets making up the transaction data. The size of an SPI transfer is not limited, however when writing to any of the DW3000 registers care must be taken not to write extra data beyond the published length of the selected register (see section 8 – The DW3000 register set ) as doing so may cause the IC to malfunction.

Physically the SPI interface is full duplex in that every transaction shifts bits both into and out of the DW3000. Logically however each transaction is either reading data from the DW3000 or writing data to it. All SPI communication shown here is from the SPI-Master (host microprocessor) point of view. Thus an SPI read means reading data from DW3000 and an SPI write means writing data into DW3000. As shown in Figure 1, for a read transaction all octets beyond the transaction header are ignored by the DW3000, and for a write transaction all octets output by the DW3000 should be ignored by the host system. The SPI transaction header selects the SPI transaction format, shown i n Figure 2:

Note: The octets are physically presented on the SPI interface data lines with the high-order bit sent first in time (MSB first). The first bit in the transaction sequence determines the direction of the communication, which is 0 for the SPI read and 1 for the SPI write operation.

| SPI transaction type | Description |

|---|---|

| Fast command transaction | Write a single octet command specified by the "Fast Command" field |

| Short addressed transaction | Read or write any of the 32 register file (IDs) in the range 0x00 to 0x1f as |

| specified by the 5-bit base address field. | |

| Full addressed transaction | Read or write any of the 32 register files, with a sub-address (an octet |

| offset index) in the range 0x00 to 0x7F as specified by the 7-bit sub | |

| address field | |

| Masked write transaction | A write only transaction allowing changes to sub-fields within any register |

| file with sub-address. This transaction includes an AND-ing mask to clear | |

| selected bits in the destination register and an OR-ing mask to set selected | |

| bits in the destination register. This command removes the need for the | |

| host to do a read-modify-write when it needs to set a sub-field in a | |

| register. | |

| Note: The masked write transaction should not be used on "write-1-to | |

| clear" event status bits. |

SPI transactions are enveloped by the assertion of the active low chip select line, SPICSn. The high-to-low assertion (low) of SPICSn initialises the SPI transaction handler so that the DW3000 interprets the next octet(s) as a new transaction header. The low-to-high de-assertion of SPICSn ends the SPI transaction.

The SPI accessible parameters of the DW3000 are organised into 32 separate register files which are further detailed in sectio n 8 – The DW3000 register set . Every SPI read or write transaction header includes a 5-bit register file ID – 5-bit base address – as shown in Figure 2, that identifies the register file is being accessed by the transaction. Sub-addressing within the selected register file allows efficient access to all the parameters within the DW3000. Depending on the sub-addressing being used, the transaction header is either one or two octets long. These three types of transaction are described in the sub-sections below.

Figure 3 shows the fields within the one octet transaction header of a fast command SPI transaction. The 5 bit fast command hex code is encapsulated by control bits which specify this SPI header as fast command type. In Figure 3 the fast command is a start transmission command ( CMD_TX , hex code 0x1),

| Bit count | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 |

2

3 4 5 6 |

||||||||

|

CMD

TX = 0x1 _ |

||||||||||

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |||

Figure 4 shows the fields within the one octet transaction header read/write command. The 5-bit register file ID is encapsulated by control bits which specify this header as a read/write transaction with a single octet header. This example is accessing th e DEV_ID register (0x00:00). Only the first octet read from the 32-bit DEV_ID register is shown with value of 0x12. Note this value may be different depending on the IC version see § 8.2.2.1 – Sub-register 0x00:00 – Device Identifier.

| Bit count | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| REG = 0x0 | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

read/write data

0 |

0 | 1 | 0 |

Figure 4: Reading first octet from DEV_ID register of the IC

Figure 5 shows the fields within the two-octet transaction header of an extended address write SPI transaction. The 5-bit base address (0x2) and 7-bit sub address (0x1C) are encapsulated by control bits which specify this SPI header as an extended address write type. Figure 5 shows the octets sent to the device to write 2 bytes to register STS_IV (reg ID 0x2 sub address 0x1C). As this is a write type the mode bits (M1 and M0) are set to 0.

| Bit count | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|

REG = 0x2

SUB ADD = 0x1C byte0 = 0x39 byte1 = 0x45 M1 M0 |

|||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

The SPI CRC mode when enabled provides the ability for SPI transactions to have the added protection of a Cyclic Redundancy Check sequence. This mode of operation is disabled by default, but may be enabled (and disabled) via the SPI_CRCEN bit in the SYS_CFG register.

Note: The SPI interface is a local digital interface which should never experience error, so the enabling of SPI CRC checking is generally unwarranted. While SPI CRC checking has a penalty in terms of the added software overhead of the host microprocessor having to calculate a CRC for every SPI write and read transaction, it may be useful for extra reliability reasons, for example where the design has long SPI lines with a possibility of interference, or in the case of design debugging where SPI integrity has not been proven.

When SPI CRC mode is enabled, the DW3000 behaves as follows:

For SPI writes from the host to the DW3000 when SPI CRC mode is enabled, the IC assumes that each SPI transaction ends with an 8-bit CRC calculated over all the preceding bytes written during the SPI transaction, i.e. from the falling edge of SPICSn. When SPICSn is de-asserted the final CRC byte of the SPI transaction is checked by the IC against a CRC it has generated for the transaction. If the CRC from the host does not match a CRC the IC generates internally, then this is considered to be an error, and the error is signalled to the host via the SPICRCE event bit in the system event status register, SYS_STATUS. This event flag may be used to generate an interrupt if the event is unmasked via the SPICRCE_EN bit in the SYS_ENABLE register.

Note: The write command will complete irrespective of the CRC error check status, which means that the data may be written to the wrong register location, and/or the data may be written incorrectly. The 8-bit CRC itself is not written to the addressed location,

The recommend recovery from a write CRC error is to reset the DW3000 completely, reinitialising and reconfiguring it into the desired operating mode for the application.

For host SPI reads of DW3000 registers when SPI CRC mode is enabled, the IC calculates an 8-bit CRC over the whole the SPI transaction, i.e. from the falling edge of SPICSn at the start of reading to its de-assertion at the end of the read. The CRC thus covers the 1 to 3 header bytes written by the host to initiate the read, and all the subsequent bytes output as the host continues the read transaction. The resultant CRC value is placed into th e SPI_RD_CRC register in Sub-register 0x00:18 – SPI CRC read status.

A host wishing to validate the CRC of an SPI read transaction, must calculate its own CRC value across the header bytes it writes and all the data bytes it subsequently reads for the transaction, and then must read the IC calculated CRC from the SPI_RD_CRC register, and compare it to the host calculated CRC. If these don't match then the host has detected an error in the SPI read.

In the event of an SPI read error, the read can just be repeated, except in the unlikely case that the error changed the read into a write. In that case a write CRC error will be triggered and this can be handled as before by resetting the DW3000 and reinitialising/reconfiguring it into the desired operating mode.

The CRC is 8-bits long, based on the CRC-8-ATM which has generator polynomial:

and has a typical implementation as shown in Figure 6, where the circle operator is an exclusive-OR.

Figure 6: SPI CRC polynomial implementation

In the DW3000 the shift register ( r 0 to r7 ) is initialised, at the start of each read or write SPI, with the value specified in th e SPICRCINIT register, which by default is all zeros.

Note: The source code of the DW3000 device driver and API [3] includes functions to generate and check the SPI CRC along with a simple example that demonstrates their use. The maximum SPI rate supported by DW3000 when the SPI CRC mode is enable is 20 MHz.

The DW3000 can be configured to assert its IRQ pin on the occurrence of one or more status events. The assertion of the IRQ pin can be used to interrupt the host controller and redirect program flow to handle the event.

The polarity of the IRQ pin may be configured via the HIRQ_POL bit in the Sub-register 0x0F:24 – Digital diagnostics test mode control. By default, on power up the IRQ polarity is active high. This is the recommended polarity to ensure lowest power operation of the DW3000 in SLEEP and DEEPSLEEP device states. This pin will float in SLEEP and DEEPSLEEP states and may cause spurious interrupts unless pulled low.

The occurrence of a status event in SYS_STATUS register may assert the IRQ pin depending on the setting of the corresponding bit in the SYS_ENABLE register.

By default, on power-up, the SPIRDY interrupt generating event enable SPIRDY_EN is set to 1 so that the interrupt enabled.

The DW3000 provides a number of GPIO pins as listed in the DW3000 Datasheet [5]. These can be individually configured at the user's discretion to be inputs or outputs. The state of any GPIO configured as an input can be read by the host controller over the SPI interface. When configured as an output the host controller can set the state of the GPIO to high or low. Some of the GPIO lines have multiple functions as listed in the DW3000 Datasheet.

The configuration and operation of the GPIO pins is controlled via GPIO_CTRL register. By default, on powerup, all GPIOs are configured as inputs.

This pin is used for external clock synchronisation purposes. See section 7.1 – External Synchronisation for further details.

The DW3000 has a number of different operational states. These are listed and described in Table 4 below and the transitions between them are illustrated i n Figure 7.

| State Name | State Description | |||||

|---|---|---|---|---|---|---|

| OFF |

In the OFF state the DW3000 is completely powered off, with no voltages applied to

any of its input pins. Power consumption = 0 µA. No I/O pins should be driven or power will leak through the I/O cells. |

|||||

| WAKE_UP |

During the WAKE_UP state the AON sequencer starts up all of the primary power and

clock blocks in order to achieve host comms in the INIT_RC state. The device will automatically transition from the WAKE_UP state to INIT_RC state. |

|||||

| INIT_RC |

Lowest power state with SPI access, but limited to 7 MHz. System is clocked off a

divide-by-four of the FAST_RC clock, i.e., the IC runs at approximately 30 MHz. |

|||||

| IDLE_RC |

Lowest power state allowing full speed SPI access. The FAST_RC oscillator is used as

the system clock source, i.e., the IC runs at approximately 120 MHz. |

|||||

| IDLE_PLL/IDLE |

In the IDLE_PLL state the DW3000 internal clock generator PLL is locked running at its

nominal 125 MHz rate and ready for use but it is gated off to most circuitry to minimize power consumption. In the IDLE_PLL state SPI communications can operate at up to 38 MHz, the maximum SPICLK frequency. In the IDLE_PLL state the analog receive and transmit circuits are powered down. The external host can control the DW3000 to initiate a transmission or reception and thus cause the DW3000 to progress into TX or RX state respectively. If a delayed TX or RX operation is initiated (see section 3.3 – Delayed transmission and 4.3 - Delayed receive) then the DW3000 will enter the TX_WAIT or RX_WAIT (until the delayed time has elapsed) and then enter TX or RX state. |

|||||

| SLEEP |

In the SLEEP state the IC consumes < 1 µA from the external power supply inputs. All

internal LDOs are turned off. In the SLEEP state the DW3000 internal low power oscillator is running and is used to clock the sleep counter whose expiry is programmed to "wake up" the DW3000 and progress into the WAKE_UP state. While the IC is in the SLEEP state, the external system should avoid applying power to GPIO, SPICLK or SPIMISO pins as this will cause an increase in the leakage current. While device is in the SLEEP state the SPI communication is not possible. Note: prior to entering SLEEP state AINIT2IDLE configuration bit in SEQ_CTRL register should be cleared. This will ensure that the device will remain in IDLE_RC state after wake up and the host can then load LDOTUNE_CAL values from OTP prior to changing into IDLE_PLL state. |

|||||

| State Name | State Description |

|---|---|

|

With the exception of the OFF state, the DEEPSLEEP state is the lowest power state of

the device. In this state the IC consumes < 250 nA from the external power supply inputs. |

|

|

In DEEPSLEEP all internal circuitry is powered down with the exception of the always

on memory which can be used to hold the device configuration for restoration on wake up |

|

|

Once in DEEPSLEEP, the DW3000 remains in this state until the occurrence of a wake

up event. This can be either: |

|

|

1.

the SPICSn line pulled low or 2. the WAKEUP line driven high |

|

| DEEPSLEEP | for the duration quoted in the DW3000 Datasheet [5] (nominally 500 μs). |

|

Once the DW3000 has detected a wake up event it progresses into the WAKE_UP

state. While the IC is in DEEPSLEEP state, the external system should avoid applying power to GPIO, SPICLK or SPIMISO pins as this will cause an increase in leakage current. |

|

|

Note: Asserting the RSTn pin (hardware reset) will also take the device out of

DEEPSLEEP, however device will be fully reset in that case. |

|

| While device is in the DEEPSLEEP state the SPI communication is not possible. | |

|

See Note: above (in SLEEP state) on clearing of AINIT2IDLE prior to entering

DEEPSLEEP state. |

|

| TX_WAIT |

This state is very like the IDLE_PLL state except the IC is implementing a delay prior to

transmission, typically aiming to transmit the RMARKER at a specified time. At the apprioiate moment the TX analog blocks are turned on and the device transitions into the TX. |

| RX_WAIT |

This state is very like the IDLE_PLL state except the IC is implementing a delay prior to

turning on the receiver. At the apprioiate time the RX analog blocks are turned on and the device transitions into the RX state. |

|

In the TX the DW3000 actively transmits a packet (generally containing the contents

of the transmit buffer) on the configured RF channel with the configured transmit parameters (PRF, data rate, preamble code etc.) |

|

| TX state |

Once the transmission is complete the DW3000, will go back to the IDLE_PLL state,

following which it may enter RX state (e.g. if using wait for response command) or go to a low-power state depending on the programmed configuration. If the ATX2SLP bit is set (in SEQ_CTRL) the DW3000 will enter the SLEEP or DEEPSLEEP state automatically, see "Auto-to-sleep" path in Figure 7 (as long as no host interrupts are pending). |

| State Name | State Description |

|---|---|

|

In the RX state, the receiver is active, either hunting for preamble or (once it has

detected preamble) actively receiving preamble searching for the start of frame delimiter (SFD), and subsequently receiving the rest of the packet. In the RX state, the RF synthesizer and all RX blocks are active. |

|

| RX state |

After an event that ends the reception, (either a good frame/packet reception, or some

error or timeout event that aborts reception) the DW3000 will return to the IDLE_PLL state unless ARX2SLP bit is set (in SEQ_CTRL) in which case the IC will enter the SLEEP or DEEPSLEEP state automatically, see "Auto-to-sleep" path in Figure 7 (as long as no host interrupts are pending). |

|

Note that it is not possible to be in the RX and TX states simultaneously – the DW3000

is a half-duplex transceiver device. |

The chipping rate specified for the HRP UWB PHY by the IEEE 802.15.4 standard [1] is 499.2 MHz, and all IC system clocks are referenced to this frequency. Where the system clock frequency is quoted as 125 MHz, this is an approximation to the actual 124.8 MHz system clock frequency (crystal 38.4 MHz × 13 ÷ 4). Similarly, where the system clock period is quoted as 8 ns, this is an approximation to the actual period of 1/(124.8×10 6 ) seconds.

The 1 GHz PLL clock, where referenced, is an approximation to its actual frequency of 998.4 MHz.

A 63.8976 GHz sampling clock is associated with ranging for the IEEE802.15.4 standar d [1], where a 15.65 picosecond time period is referred to, it is an approximation to the period of this clock.

The PRF values of 16 MHz and 64 MHz quoted in this document are approximations to the values dictated by the IEEE802.15.4 standard [1]. PRF mean values are slightly higher fo r SHR compared to the PHR and data parts of the packet. Please refer t o [1] for full details of peak and mea n PRFs .

Where a data rate of 6.8 Mb/s is referred to, this is equivalent to the 6.81 Mb/s data rate in [1]. Note that the data rates quoted are (rounded) nominal values based on the data symbol rate multiplied by the Reed-Solomon (RS) coding rate, 0.87 which is 330/378 because the RS coding adds 48 parity bits for every 330 bits data (or part thereof). Please refer t o [1] for more details.

When the external power source is applied to the DW3000 for the first time (cold power up), the internal Power On Reset (POR) circuit compares the externally applied supply voltage (VDD1) to an internal power-on threshold (approximately 1.5 V), and once this threshold is passed the AON block is released from reset and the external device enable pin EXTON is asserted. This is shown in Figure 8.

Then the VDD2a and VDD3 supplies are monitored and once they are above the required voltage as specified in the Datasheet (2.2 V and 1.4 V respectively), the fast RC oscillator (FAST_RC) and crystal (XTAL Oscillator) will come on within 500 µs and 1 ms respectively. However if time for VDD2a or VDD3 exceeds 10 ms then the device will need to be reset once these supplies are up. Please refer to the Datasheet [5] for more details.

The DW3000 digital core will be held in reset until the crystal oscillator is stable. Once the digital reset is deasserted the digital core wakes up and enters the INIT_RC state, (see Figure 7 an d Figure 8) . Then once the configurations stored in AON and OTP have been restored (into the configuration registers) the device will enter the IDLE_RC state IDLE_RC . Then the host can set the AINIT2IDLE configuration bit i n SEQ_CTRL and the IC will enable the CLKPLL and wait for it to lock before entering the IDLE_PLL state.

Figure 8: Timing diagram for cold start POR

In the very low power DEEPSLEEP state, the IC is almost completely powered down except for a small amount of "always-on" memory necessary to maintain IC configurations. This is the lowest power mode of the IC where the power drain is approximately 200 nA. To wake the IC from DEEPSLEEP state requires an external agent to assert the WAKE_UP input line or the external host microprocessor to initiate an SPI transaction to assert the SPICSn input.

The DW3000 also includes a low power SLEEP state where the IC can wake itself from sleeping as a result of the elapsing of a sleep timer (see 8.2.11.6.1 for sleep timer configuration) that is running from a lowpowered oscillator internal to the DW3000 IC. In this SLEEP state the power drain is approximately 1 µA. The IC will wake from the SLEEP state when the sleep timer elapses, or the WAKE_UP or SPICSn inputs may be used to wake the device before the timer elapses.

The frequency of the low power oscillator is dependent on process variations within the IC, but is typically around 20 kHz. There are facilities within the IC to measure the frequency of this LP oscillator and also to trim it.

Figure 9: Timing diagram for warm start (@ VDD = 3V)

Waking from SLEEP and DEEPSLEEP states can happen in following ways:

• Driving the WAKEUP pin high for approximately 500 μs, (assuming WAKE_WUP configuration bit is set in AON_CFG) .

• Driving the SPICSn pin low for approximately 500 μs, (assuming th e WAKE_CSN configuration bit is set i n AON_CFG) . This can be achieved by doing a dummy SPI read of sufficient length.

Note: When using the SPICSn pin to wake up the device it is important that the SPIMOSI line is held low for the duration of the SPICSn to ensure that a spurious write operation does not occur.

In addition return from SLEEP also occurs when

• The internal sleep timer counter expires, (assuming the WAKE_CNT configuration bit is set in AON_CFG along with an appropriate SLEEP_TIM value).

In all three wake up cases the device is returned to the IDLE_PLL state if the AINIT2IDLE configuration bit in SEQ_CTRL register was set when the device configuration was uploaded prior to entering sleep state, otherwise the device will stay in IDLE_RC . Additional state transitions can be automatically enacted thereafter depending on configurations.

Asserting the RSTn pin (hardware reset) will also take the IC out of SLEEP or DEEPSLEEP states, however device will be fully reset in that case.

Prior to entering the SLEEP or DEEPSLEEP states the main DW3000 configuration register values are saved (copied) into the Always-On (AON) memory, and upon waking, prior to exiting the INIT_RC state the saved values are restored from the AON memory.

Power is maintained to the AON memory at all times, even in SLEEP and DEEPSLEEP states. The copying of configuration data (saving or restoring) and boot up time of the OTP takes ~85 µs to complete (when restoring from SLEEP and DEEPSLEEP states, se e Figure 9). Restoration of configurations during the WAKE_UP state is only done if the ONW_AON_DLD configuration bit is set in AON_DIG_CFG.

Note: The host should wait for the restoration of configurations to be completed before using SPI to avoid internal IC conflicts that may lead to the corruption of the configuration values. The preffered option is to wait for the assertion of the SPIRDY interrupt.

| Configuration Register | Configuration Register |

|---|---|

| AON_DIG_CFG [23:0] | GPIO_MODE [31:0] |

| XTAL [7:0] | DTUNE0 [15:0] |

| PLL_CAL [7:0] | RX_SFD_TOC [15:0] |

| PANADR [31:0] | PRE_TOC [15:0] |

| SYS_CFG [31:0] | DTUNE3 [31:0] |

| FF_CFG [15:0] | |

| TX_FCTRL [47:0] | PLL_CFG [15:0] |

| DREF_TIME [31:0] | CIA_CONF [31:0] |

| RX_FWTO [23:0] | FP_CONF [31:0] |

| SYS_ENABLE [47:0] | IP_CONF [31:0] |

| TX_ANTD [15:0] | STS_CONF_0 [31:0] |

| ACK_RESP_T [31:0] | STS_CONF_1 [31:0] |

| TX_POWER [31:0] | SEQ_CTRL [31:0] |

| CHAN_CTRL [15:0] | TXFSEQ [31:0] |

| AES_IV0 [31:0] | LED_CTRL [15:0] |

| AES_IV1 [31:0] | RX_SNIFF [31:0] |

| AES_IV2 [31:0] | DGC_CFG [15:0] |

| AES_IV3 [31:0] | RF_SWITCH [31:0] |

| DMA_CFG [31:0] | GPIO_PULL_EN [15:0] |

| AES_KEY [127:0] | CIA_ADJUST [15:0] |

| STS_CFG [15:0] | |

| STS_KEY [127:0] | |

| STS_IV [127:0] |

| Table 5: Configurations maintained in the AON memory array |

|---|

| Configuration Register | |||||||

|---|---|---|---|---|---|---|---|

| GPIO_MODE [31:0] | |||||||

| DTUNE0 [15:0] | |||||||

| RX_SFD_TOC [15:0] | |||||||

| PRE_TOC [15:0] | |||||||

| DTUNE3 [31:0] | |||||||

| PLL_CFG [15:0] | |||||||

| CIA_CONF [31:0] | |||||||

| FP_CONF [31:0] | |||||||

| IP_CONF [31:0] | |||||||

| STS_CONF_0 [31:0] | |||||||

| STS_CONF_1 [31:0] | |||||||

| SEQ_CTRL [31:0] | |||||||

| TXFSEQ [31:0] | |||||||

| LED_CTRL [15:0] | |||||||

| RX_SNIFF [31:0] | |||||||

| DGC_CFG [15:0] | |||||||

| RF_SWITCH [31:0] | |||||||

| GPIO_PULL_EN [15:0] | |||||||

| CIA_ADJUST [15:0] | |||||||

When waking from SLEEP or DEEPSLEEP it is necessary to load the LDOTUNE_CAL value that is programmed into OTP during IC production test calibration.Default configuration on power up and after a reset

DW3000 is a highly configurable transceiver with many features. The register default (reset) values have been selected with the intention of minimising the amount of user configuration required. The default configuration is summarised in Table 6.

| Parameter | Default Value | ||||||

|---|---|---|---|---|---|---|---|

| Channel | 5 (CF is 6489.6 MHz) | ||||||

| Data Rate | 6.8 Mb/s | ||||||

| PHR Rate | 850 kb/s | ||||||

| PRF | 64 MHz | ||||||

| Preamble Length | 64 symbols | ||||||

| Preamble Code | 9 | ||||||

|

Scrambled Timestamp

Sequence (STS) |

off | ||||||

| STS Sequence Length | n/a | ||||||

| SFD | IEEE802.15.4z [2] length 8 | ||||||

Channel numbers and preamble codes are as specified in the standard, IEEE802.15.4 standar d [1]. Some further details are given below on the specifics of the default device configuration. For full details please refer to the register map where the default value of each register is given, § 8 – The DW3000 register set .

Note: the above default configuration needs to be modified in oder for the DW3000 to correctly interoperate with the DW1000 on CH5.

Much of the system configuration is configured in the SYS_CFG register, please see section Sub-register 0x00:10 – System configuration for a full description of the register contents and defaults.

By default, interrupt polarity is active high and all interrupts are disabled, see HIRQ_POL in th e DIAG_TMC register for interrupt polarity and the SYS_ENABLE and SYS_STATUS registers for interrupt configuration and information, see sections Sub-register 0x00:3C – System event enable mask and Sub-register 0x00:44 – System event status .

GPIOs are all set to mode 0 (as defined in the GPIO_MODE register), their default function is shown i n Table 7.

| GPIO Pin | Default Function |

|---|---|

| GPIO0/RXOKLED | GPIO0 |

| GPIO1/SFDLED | GPIO1 |

| GPIO2/RXLED | GPIO2 |

| GPIO3/TXLED | GPIO3 |

| GPIO4/EXTPA | GPIO4 |

| GPIO5/EXTTXE/SPIPOL | GPIO5 |

| GPIO6/EXTRXE/SPIPHA | GPIO6 |

| SYNC/GPIO7 | SYNC |

| IRQ/GPIO8 | IRQ |

Frame wait timeout (see SYS_CFG register bi t RXWTOE and Sub-register 0x00:34 – Receive frame wait timeout period ) and preamble detection timeout (see Sub-register 0x06:04 – Preamble detection timeout count) are off, whilst SFD detection timeout (see Sub-register 0x06:02 – SFD detection timout count) is on.

Othe r SYS_CFG register settings such as automatic receiver re-enable (RXAUTR) and MAC functions such as frame filtering (FFEN) , double buffering (DIS_DRXB) and automatic acknowledgement (AUTO_ACK) are all off by default. Automatic CRC generation in the MAC frame data is on (DIS_FCS_TX) .

External synchronisation and the use of external power amplifiers are deactivated by default, see sections 7.1 – External Synchronisation and 7.2 – External power amplification .

Channel 5, preamble code 9 and 64 MHz PRF are set by default in th e CHAN_CTRL register, see Sub-register 0x01:14 – Channel control for more information.

The transmit data rate is set to 6.8 Mb/s in the TX_FCTRL register, see TXBR field in Sub-register 0x00:24 – Transmit frame control . The receive data rate is never set it can be decoded from the PHR bits.

Transmit RF channel configurations are set for channel 5 by default – see Sub-register 0x07:1C – RF TX control register 2. The transmit preamble symbol repetition length is 64 symbols, see Sub-register 0x00:24 – Transmit frame control, TXPSR field for configuration details.

Receiver RF channel configurations are set for channel 5 by default, to match the transmitter.

Digital receiver tuning registers are configured by default for 64 MHz PRF, 6.8 Mb/s data rate and a preamble symbol repetition of length 64. See Sub-register 0x06:00 – Digital RX tuning register for programming details.

The CIARUNE bit (CIA run enable) is enabled by default, which means that th e CIA algorithm will execute on every packet reception, which in turn will calculate accurate time-of-arrival. If the running the CIA is not required then th e CIARUNE control in Sub-register 0x11:08 – Sequencing control can be turned off (set to zero). This may be useful in a data communications only application, to save power and time.

The IEEE802.15.4 standar d [1] has 16 defined channel/bands for the HRP UWB PHY. The DW3000 supports the subset of these listed i n Table 8 below. Depending on the channel and the pulse repetition frequency (PRF) the IEEE802.15.4 standard [1] HRP UWB PHY defines a choice of two or four preamble codes. The standard defined preamble code options are also listed i n Table 8. The combination of channel number and preamble code is what the standard terms a complex channel .

|

Channel

number |

Centre

frequency (MHz) |

Bandwidth

(MHz) |

Preamble Codes

(16 MHz PRF) |

Preamble Codes

(64 MHz PRF) |

|||

|---|---|---|---|---|---|---|---|

| 5 | 6489.6 | 499.2 | 3, 4 | 9, 10, 11, 12 | |||

| 9 | 7987.2 | 499.2 | 3, 4 | 9, 10, 11, 12 | |||

The preamble codes specified by the standard for use on a particular channel were chosen to have a low cross correlation factor with each other with the intention that the complex channels could to operate independently from each other as separate networks. In practice, as there is still some cross correlation, there will be some break-through between different codes especially in conditions of close proximity with long preambles.

The IEEE802.15.4 standar d [1] includes a feature called dynamic preamble select (DPS) , where devices switch to using one of th e DPS specific preamble codes for the ranging exchange, and perhaps a different one for each direction of communication. The idea is to make it more difficult to eavesdrop or spoof, by randomly changing the DPS preamble codes in a mutually agreed sequence only known to the valid participants. This is supported by the DW3000 where at 64 MHz PRF the preamble codes additionally available for DPS are: 13, 14, 15, 16, 21, 22, 23 and 24.

The UWB specified in the IEEE802.15.4 standar d [1] is sometimes called impulse radio UWB because it is based on high speed pulses of RF energy. During the PHR and Data parts of the packet, information bits are signalled by the position of the burst, in a modulation scheme termed burst position modulation (BPM).

Each data bit passes through a convolution encoder to generate a "parity" bit used to set the phase of the burst as either positive or negative, this component of the modulation is termed binary phase-shift keying (BPSK). Figure 10 shows how the convolutional encoder contributes to this BPM/BPSK modulation. A coherent receiver (i.e. one tracking carrier timing and phase) such as the one in the DW3000 can determine this burst phase and use it in a Viterbi decoder to get an additional 3 dB of coding gain, thereby extending the operational range of the modulation.

Figure 10: BPM/BPSK data and PHR modulation

In addition the quarter symbol interval is sub-divided into 2, 4, or 8 sub-intervals and a pseudo random sequence used to determine both the burst shape and which of the sub-intervals are actually used for the burst transmission. This gives more immunity to interference and whitens the output spectrum allowing a higher signal power to be used in the transmitter.

Forward error correction (FEC) is also included in the PHR and Data parts of the packet. The 19-bit PHR includes a 6-bit single-error-correct double-error-detect (SECDED) code and the data part of the packet has a Reed Solomon (RS) code applied. Both SECDED and RS codes are termed "systematic" meaning that the data can be recovered without using the codes (and of course not benefitting from them in that case), e.g. by a non-coherent receiver. The 850 kb/s and 6.8 Mb/s user data rates quoted, include allowance for the 0.87 average RS coding rate. The PHR is not RS coded so for example at the 850 kb/s nominal rate the PHR is actually sent at 975 kb/s.

The Synchronisation Header (SHR) consists of the preamble sequence and the SFD (start of frame delimiter). In contrast to the BPM/BPSK modulation used for the PHR and data, the synchronisation header is made up of single pulses. The preamble symbol period is divided into approximately 500 "chip" time intervals, (496/508 depending on 16/64 MHz PRF 1 ), in which either a negative or a positive pulse may be sent, or no pulse. The "chip" interval is 499.2 MHz, a fundamental frequency within the UWB PHY, and so the resultant symbol times are thus 496 /499.2 µs for 16 MHz PRF, and 508 /499.2 µs for 64 MHz PRF, (see Table 9 below).

The sequence of pulses sent during the preamble symbol interval is determined by the preamble code. The standard defines 8 preamble codes of length-31 for use at 16 MHz PRF and 16 preamble codes of length-127 for use at 64 MHz PRF. The standard nominates particular codes for particular channels so that at 16 MHz PRF there are just two to choose from per channel, while at 64 MHz PRF there is a choice of four codes per channel. The length-31 codes are spread by inserting 15 zeros after each pulse to give the 496 chip times per symbol while the length-127 codes are spread by inserting 3 zeros after each pulse to give the 508 chip times per symbol. The preamble length and duration is defined by how many times (i.e. for how many

1 The DW3000 supports average pulse repetition frequencies of 16 MHz and 64 MHz

© Decawave Ltd 2019 Version 1.1 Page 29 of 255

symbols) the sequence is repeated. This is determined by the configuration of the number of preamble symbol repetitions (PSR).

| Mean PRF (MHz) | #Chips Per Symbol | Preamble Symbol Duration (ns) |

|---|---|---|

| 16 nominal | 496 | 993.59 |

| 64 nominal | 508 | 1017.63 |

The standard defines PSR settings of 16, 64, 1024 and 4096. The DW3000 supports these (although it will not receive packets with preamble length below 32 symbols) and in addition supports PSR settings of 128, 256, 512, 1536 and 2048.

The preamble sequence has a property of perfect periodic autocorrelation 2 which in essence allows a coherent receiver to determine the exact impulse response of the RF channel between transmitter and receiver. This brings two important benefits. Firstly, it allows the receiver make use of the received energy from multiple paths, turning multipath from an interference source into a positive affect extending operating range. Secondly, it lets the receiver resolve the channel in detail and determine the arrival time of the first (most direct) path, even when attenuated, which brings precision advantages for RTLS applications.

Note: The DW3000 includes a packet format specified by new IEEE802.15.4z amendment [2] which incorporates a cryptographically generated scrambled timestamp sequence (STS) that can be used to obtain an RX timestamp that has improved integrity in terms of its robust to accidental or deliberate interference, e.g. as a result of packet collisions, for more details of this please refer to sectio n 6 below. The SFD marks the end of the preamble and the precise start of the switch into the BPM/BPSK modulation of the PHR. The time-stamping of this event is deterministic in terms of symbol times and it is this in conjunction with determining the first arriving ray within that symbol time that allows the accurate timestamping needed for precision RTLS applications. The standard specifies the SFD, which consists of the preamble symbols either not sent, or sent as normal or sent inverted (i.e. positive and negative pulses reversed) in a defined pattern 8 symbol times long for 850 kb/s and 6.81 Mb/s data rates. The length-8 SFD sequence is: 0, +1, 0, -1, +1, 0, 0, -1. The IEEE802.15.4z amendment also specifies length-8 SDF without zeros, ( -1, -1, -1, +1, -1, -1, +1, -1), which gives improved performance in a coherent receiver such as the DW3000 that supports it.

The PHY header (PHR) is modulated using the BPM/BPSK modulation scheme defined in section 2.7 above, but it does not employ the Reed Solomon code used for data, instead is employs a 6-bit SECDED parity check sequence as part of its 19-bit length.

2 V. P. Ipatov, "Ternary sequences with ideal autocorrelation properties," Radio Eng. Electron. Phys., vol. 24, pp. 75–79, 1979

| Bit 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| R1 | R0 | L6 | L5 | L4 | L3 | L2 | L1 | L0 | RNG | EXT | P1 | P0 | C5 | C4 | C3 | C2 | C1 | C0 |

| Data Rate | Frame Length |

Ra

fra ng me ing |

Ex

He te ad ns er ion |

Duration | Preamble | SECDED Check Bits | ||||||||||||

Figure 11 above shows the bits of the PHR. These are transmitted bit-0 first in time. The DW3000 fills in the Data Rate, Frame Length, Ranging frame, and Preamble Duration fields of the PHR based on the user configuration of the appropriate parameters in TX_FCTRL and generates th e SECDED sequence accordingly. The Header Extension bit of the PHR is always zero and is reserved by IEEE for future extensions.

Standard IEEE 802.15.4-2020 UWB packets can carry up to 127 bytes of payload, se e Figure 11: PHR bit assignment. The DW3000 also supports a mode of operation with frame lengths up to 1023 bytes. This mode of operation is enabled via the PHR_MODE selection bits of Sub-register 0x00:10 – System configuration , which changes the defifinition of the PHR bits. While this makes the PHR non-compliant with IEEE 802.15.4 this PHR format is actually defined as an option in the IEEE 802.15.8 standard.

In this mode the PHY header (PHR) is redefined to carry the 3 extra bits of frame length. In order to communicate extended length frames between two DW3000 devices both ends must be set to the long frame PHY header mode via the PHR_MODE selection bits of Sub-register 0x00:10 – System configuration . If the setting is only at one end of a link any attempt at communication will fail with PHR errors being reported. When this long frame mode is selected, the DW3000 will be unable to successfully communicate with any device operating with the IEEE 802.15.4 standard frame encoding, and because the SECDED error check sequence of the PHR in this long frame mode is inverted this will cause PHR error events in advance of any attempt to receive the payload.

Note that the probability of an error occurring within a frame increases as the frame length is increased, and as a result of this increasing the frame length may or may not improve system throughput depending on the error rate and the need to retransmit frames when there is an error.

In long frame mode only the high order bit of the TXPSR value from TX_FCTRL is sent in the PHR and reported in the RXPSR value in RX_FINFO.

The PHR encoding for the extended length frames is shown below i n Figure 15:

|

Bit

0 |

1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 14 | 16 | 17 | 18 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| R1 | R0 | L9 | L8 | L7 | L6 | L5 | L4 | L3 | L2 | L1 | L0 | P0 | S5 | S4 | S3 | S2 | S1 | S0 |

|

Data

Frame Length Rate |

Du

Pre rat am ion ble |

SECDED Check Bits | ||||||||||||||||

The Data Rate field has the same encoding as used for the IEEE802.15.4 standard PHR.

The frame length field L9-L0 is an unsigned 10-bit integer number that indicates the number of octets in the PSDU from the MAC sub-layer. Note that the high order bit of the length is transmitted first in time.

A single bit, P0, provides the Preamble Duration field, indicating the length of the SYNC portion of the SHR shown in Table 11.

| Table 10: Preamble duration field values in extended length frame PHR |

|---|

| P0 |

Preamble length for

BPM-BPSK modulation mode |

||||||

|---|---|---|---|---|---|---|---|

| 0 | 64 to 1024 symbols | ||||||

| 1 | 1536 to 4096 symbols | ||||||

The preamble duration field, TXPSR, may be used by a receiver to set the value of the preamble duration for an ACK frame to 64, 128, 256, 512, 1024, 1536, 2048 and 4096 symbols. Alternatively, the FINE_PLEN field may be used to set any multiple of 8 as a preamble length from 32 to 2048. The application may use the count of received preamble symbols, as reported i n IP_DIAG12 register, to additionally inform the choice of preamble length for any response frames.

The SECDED field, S5–S0, is a set of six parity check bits that are used to protect the PHR from errors caused by noise and channel impairments. The SECDED calculation is the same as that defined in IEEE802.15.4 standard [1] except the bits C5–C0 are inverted to get S5–S0 as follows:

S0 = NOT (C0), S1 = NOT (C1), S2 = NOT ( C2), S3 = NOT (C3), S4 = NOT (C4) and S5 = NOT (C5) This is as specified in the IEEE 802.15.8 standard for frames up to 1023 octets.

The transmission of packets is one of the basic functions of the DW3000 transceiver. The packets can be sent both with and without data payload. The DW3000 supports four packet formats, the IEEE802.15.4 standard [1] packet format, and three new IEEE802.15.4z amendment [2] defined formats where a scrambled timestamp sequence (STS) is introduced into the packet as shown in Figure 13. When the STS modes are enabled the DW3000 transmitter will insert the STS in the position shown, and the receiver will expect it to be present accordingly. The packet begins with a synchronisation header consisting of the preamble and the SFD (start of frame delimiter). The PHY header (PHR) defines the length (and data rate) of the data payload part of the packet. The STS when inserted allows for secure timestamping, and ranging, see § 6.

The DW3000 basic transmit sequence is as shown in Figure 14, beginning in the IDLE_PLL state awaiting instruction from the host controller.

In order to transmit, the host controller must write data for transmission to TX_BUFFER, and select the preamble length, frame length, data rate and PRF in the Transmit Frame Control and Channel Control registers, TX_FCTRL and CHAN_CTRL. The PRF will be set according to the chosen preamble code (TX_PCODE) . Assuming all other relevant configurations have already been made, the host controller initiates the transmission by issuing a TX command (e.g. CMD_TX ). Once transmission is initiated, the DW3000 sends the complete packet of preamble , SFD, PHR and the PHY Payload (MAC Frame). The STS will be included optionally depending on the configured packet format (se e Figure 13) . In the STS packet configuration 3 (SP3) the PHR and PHY Payload is omitted.

As an aid to MAC layer framing, the IC calculates the FCS (CRC) during the transmission of the (MAC) data from th e TX_BUFFER based on the frame length (TXFLEN) and automatically appends it.

The end of transmission is signalled to the host via the TXFRS event status bit in SYS_STATUS, and the DW3000 returns to IDLE_PLL mode to await new instructions.

Figure 14: Basic transmit sequence

Further transmission features are described in the following sections:

During packet transmission the event nominated to time-stamp termed the RMARKER, where the RMARKER is defined in the IEEE standard to be the time when the beginning of the first symbol following th e SFD is at the local antenna, or more precisely the peak pulse location associated with the first chip following the SFD.

The DW3000 digital transmit circuitry takes note of the system clock counter as the RAW transmit timestamp at the point when it begins sending the first chip following th e SFD. It then adds to this the transmit antenna delay (configured in TX_ANTD) to get the antenna adjusted transmit time-stamp that it writes to th e TX_STAMP field of TX_TIME.

See also section 10.3 – IC calibration – antenna delay.

For delayed transmission, the transmit time is programmed into DX_TIME and then the delayed transmission is initiated by issuing the CMD_DTX command. Alternatively a delayed transmission can be achieved by programming a "reference time" into the DREF_TIME and an offset into th e DX_TIME, after which delayed transmission command , CMD_DTX_REF, is issued instead.

One of the design goals of delayed transmission was that the specified transmission time would be predictable and aligned with the transmit timestamp. This was achieved in that the transmission time specified is the time of transmission of the RMARKER (not including the TX antenna delay), that is the raw TX time, TX_RAWST before the antenna delay is added. This allows for the time of transmission of a message to be pre-calculated and embedded in the message being transmitted.

Note: The value programmed into DX_TIME (and in DREF_TIME) is in time units of 4 ns, or more precisely 2 ÷ (499.2×10 6 ). To calculate the time of transmission of th e RMARKER at the antenna, the low 9 bits of the delayed TX time should be zeroed before adding the TX antenna delay, and the high 32-bits of the 40-bit result written int o DX_TIME, (or a reference time programmed into DREF_TIME and an offset into the DX_TIME) . Note: the least significant bit of DX_TIME is ignored so its effective resolution of is really 4 ÷ (499.2×10 6 ) or approximately 8 ns.

In performing a delayed transmission, i.e., after the CMD_DTX is issued, the DW3000 calculates an internal start time for when to begin sending the preamble to make the RMARKER raw timestamp agree with the programmed transmit time. The DW3000 then remains in TX_WAIT state until the system time (SYS_TIME) reaches the correct point to turn on the transmitter and begin preamble.

One use of delayed transmission (and reception), is to control the response times in two-way ranging, (described in APPENDIX 1: Two-way ranging), and especially to allow the prediction and embedding of the TX timestamp (or response delay) into the transmitted message to reduce the number of messages necessary for a ToF measurement. Delayed transmission (and reception) also helps to minimise the response times to save power, however in working towards this the host microprocessor may sometimes be late invoking the delayed TX, i.e., where the system clock has passed the specified start time (i.e. internal start time mentioned above) and then the IC would have to complete almost a whole clock count period before the start time is reached. The HPDWARN event status flag in SYS_STATUS warns of this "lateness" condition so that during application development the delay may be chosen large enough to generally avoid this lateness. The HPDWARN status flag also serves to facilitate detection of this late invocation condition so that recovery measures may be taken should it ever occur in deployed product. For delayed transmission it is the internal start time mentioned above that is used when deciding whether to set the HPDWARN event for the delayed transmit. As long as the preamble start time is in the near future, the HPDWARN event flag will not be set. If a long delay was intended then HPDWARN flag can be ignored and the transmission will begin at the allotted time. If a long delay was not intended then the transmission can be stopped by issuing transceiver off command CMD_TXRXOFF .

Standard IEEE 802.15.4-2015 UWB packets can carry up to 127 bytes of payload. The DW3000 also supports a mode of operation with frame lengths up to 1023 bytes. This mode of operation is enabled via the PHR_MODE selection bits of Sub-register 0x00:10 – System configuration , which changes the defifinition of the PHR bits. While this makes the PHR non-compliant with IEEE 802.15.4 this PHR format is actually defined as an option in the IEEE 802.15.8 standard.

In this mode the PHY header (PHR) is redefined to carry the 3 extra bits of frame length. In order to communicate extended length frames between two DW3000 devices both ends must be set to the long frame PHY header mode via the PHR_MODE selection bits of Sub-register 0x00:10 – System configuration . If the setting is only at one end of a link any attempt at communication will fail with PHR errors being reported. When this long frame mode is selected, the DW3000 will be unable to successfully communicate with any device operating with the IEEE 802.15.4 standard frame encoding, and because the SECDED error check sequence of the PHR in this long frame mode is inverted this will cause PHR error events in advance of any attempt to receive the data payload.

Note that the probability of an error occurring within a frame increases as the frame length is increased, and as a result of this increasing the frame length may or may not improve system throughput depending on the error rate and the need to retransmit frames when there is an error.

In long frame mode only the high order bit of the TXPSR value from TX_FCTRL is sent in the PHR and reported in the RXPSR value in RX_FINFO.

|

Bit

0 |

1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 14 | 16 | 17 | 18 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| R1 | R0 | L9 | L8 | L7 | L6 | L5 | L4 | L3 | L2 | L1 | L0 | P0 | S5 | S4 | S3 | S2 | S1 | S0 |

|

Data

Frame Length Rate |

Du

Pre rat am ion ble |

SECDED Check Bits | ||||||||||||||||

The PHR encoding for the extended length frames is shown below i n Figure 15:

The Data Rate field has the same encoding as used for the IEEE802.15.4 standard [1] PHR.

The frame length field L9-L0 is an unsigned 10-bit integer number that indicates the number of octets in the PSDU from the MAC sub-layer. Note that the high order bit of the length is transmitted first in time.

A single bit, P0, provides the Preamble Duration field, indicating the length of the SYNC portion of the SHR shown in Table 11.

| P0 |

Preamble length for

BPM-BPSK modulation mode |

|---|---|

| 0 | 64 to 1024 symbols |

| 1 | 1536 to 4096 symbols |

The preamble duration field, TXPSR, may be used by a receiver to set the value of the preamble duration for an ACK frame to 64, 128, 256, 512, 1024, 1536, 2048 and 4096 symbols. Alternatively, the FINE_PLEN field may be used to set any multiple of 8 as a preamble length from 32 to 2048. The application may use the count of received preamble symbols, as reported i n IP_DIAG12 register, to additionally inform the choice of preamble length for any response frames.

The SECDED field, S5–S0, is a set of six parity check bits that are used to protect the PHR from errors caused by noise and channel impairments. The SECDED calculation is the same as that defined in IEEE802.15.4 standard [1] except the bits C5–C0 are inverted to get S5–S0 as follows:

S0 = NOT (C0), S1 = NOT (C1), S2 = NOT ( C2), S3 = NOT (C3), S4 = NOT (C4) and S5 = NOT (C5) This is as specified in the IEEE 802.15.8 standard for frames up to 1023 octets.

The reception of a packet is enabled by a host request enabling of the receiver. This can be done while the device is in either IDLE_RC or IDLE_PLL state. If the device was in IDLE_RC it will firstly clalibrate, enable PLL and switch to IDLE_PLL state and then goin into RX state. However, prior to the first RX enable following device power up, the receiver needs to be calibrated. This is done by performing RX calibration, for more details on this see the dwt_pgf_cal() API [3] an d RX_CAL register. The RX calibration is automatically done on wakeup as long a s ONW_PGFCAL bit is set. It is also recommended that the receiver is re-calibrated if the operating temperature changes by 20 °C.

Figure 16: Receive sequence

To enable the receiver, the host issues an RX start command (see section on Fast Commands) . The receiver will start by searching for preamble continually until preamble has been detected or acquired, then a demodulation will be attempted. A preamble detection timeout may be set to allow the receiver to stop searching for preamble after a desired period (which is programmable i n PRE_TOC) . A receive sequence is shown in Figure 16.

The preamble sequence is detected by cross-correlating in preamble acquisition chunks (PACs ) which are a number of preamble symbols long. The size of chunk used is selected by the PAC configuration in DTUNE0. The PAC size should be selected depending on the expected preamble size. A larger PAC size gives better performance when the preamble is long enough to allow it, but if the PAC is too large for the preamble length the receiver performance will be impaired, or fail to work at the extremes – (e.g. a PAC of 32 will never receive packets with just 32 preamble symbols). Table 12 gives the recommended PAC size configuration to use in the receiver depending on the preamble length being used in the transmitter.

|

Expected preamble

length of packets being received |

Data Rate |

Recommended

PAC size |

|||

|---|---|---|---|---|---|

| 32 | 6.81 Mb/s | 4 | |||

| ≥ 64 | 6.81 Mb/s | 8 | |||

| ≥ 128 | 850 kb/s | 16 | |||

Aborting reception with use of preamble detection timeout (PRE_TOC) is very useful following sending a message where a response is being awaited. Here if the preamble is not detected then the awaited response is not coming. The preamble detection time-out can be used to abandon the reception at the earliest possible time, saving power.

Once the preamble sequence is detected, the receiver begins accumulating correlated preamble symbols and building a channel impulse response (CIR) , while in parallel looking for th e SFD sequence (a particular sequence of preamble symbols, see § 2.8 – Synchronisation header modulation scheme for details).

The detection of SFD is a key event in the reception of a packet, because it marks th e RMARKER, which is time-stamped (see section 4.1.7 – RX message timestamp ), and it marks the change from preamble demodulation to the BPM /BPSK demodulation of th e PHR and data or STS demodulation if enabled.

It is possible to abort reception if the SFD is not detected within a certain time after preamble is detected. This functionality is configured via DRX_SFDTOC. This SFD detection timeout guards against false detection of preamble (which has a finite chance of happening) that could otherwise lead to a prolonged period receiving nothing. By default, the SFD detection timeout is 65 symbol times (to match the default preamble length of 64 symbols and a PAC size of 8). It is not recommended to disable the SFD detection timeout.

The SFD sequence is either 8 or 16 symbols long for the supported data rates of 6.8 Mb/s or 850 kb/s. The type of the SFD sequence used is defined by SFD_TYPE configuration bits i n CHAN_CTRL register, and are described in Table 22.

If the STS is enabled, see Figure 13, the receiver will construct another CIR from that. The time-of-arrival (ToA) can also be derived from this CIR estimate.

The STS itself consists of a series of equally spaced pulses whose polarity is derived from an AES128 based cryptographically secure pseudo random number generator as specified in the IEEE802.15.4z amendment.

This can help when constructing a secure ranging environment (see 6 Secure ranging / timestamping) and it also improves immunity to packet collisions on the air.

The main role of the PHY Header (PHR) is to convey the length of the data portion of the packet, and to indicate the data rate being employed for data demodulation. See paragraph 2.9 - PHY header and paragrap h 2.10 for details of the PHY header. For data rates of 850 kb/s and 6.8 Mb/s th e PHR is modulated / demodulated as per the 850 kb/s data rate (note that because Reed Solomon encoding is not applied to the PHR, its bit rate is approximately 1 Mb/s). If th e PHR is indicating 850 kb/s then the data demodulation continues at this rate, but if th e PHR is indicating 6.8 Mb/s then the demodulation changes to this rate at the end of the PHR as data demodulation begins.

It is also possible to configure the PHR rate to be the same as the data rate, i.e. to use 6.8 Mbit/s with PHR_6M8 configuration bit i n SYS_CFG, 8.2.2.4.

Section 2.7 – Data modulation scheme describes the modulation scheme. In the receiver a Viterbi decoder is used to recover the data bits (this is also used for PHR reception) which are then passed through the Reed Solomon decoder to apply, if it can, any further corrections. Every octet thus received is passed through a CRC checker that checks the frame against the transmitte d FCS.

As the data octets are received they may also be parsed by the frame filtering function if enabled, see section 5.4 – Frame filtering for more details.

Successful reception of a frame is signalled to the host via th e RXFR an d RXFCG event status bits in SYS_STATUS. Other status bits in this register may be used to flag reception of other parts of the frame or, events indicating failure, i.e. RXPTO (Preamble detection Timeout), RXSTO (SFD timeout) , RXPHE (PHY Header Error), RXFSL (Reed Solomon error), RXFTO (Frame wait timeout), etc.

| Features related to reception | Section |

|---|---|

| Receive message time-stamping | 4.1.7 – RX message timestamp. |

| Delayed reception | 4.3 - Delayed receive |

| Receiving long frames | 02.10 – Extended PHY header |

The IEEE802.15.4 standar d [1] nominates the time when the RMARKER arrives at the antenna as the significant event that is time-stamped, also shown i n Figure 13.

The DW3000 digital receiver circuitry takes a coarse timestamp of the symbol in which th e RMARKER event occurs and adds in various correction factors to give a resultant adjusted time stamp value, which is the time at which the RMARKER arrived at the antenna. This includes subtracting the receive antenna delay as configured in the RXANTD register (i n CIA_CONF) and adding the correction factor determined by the first path (leading edge) detection algorithm embedded in the DW3000. The resulting fully adjusted RX timestamp is written into RX_STAMP, IP_TOA an d STS_TOA registers .

See also section 10.3 – IC calibration – antenna delay , and section 6 – Secure ranging / timestamping .

The two-antenna port variants of DW3000 chip can measure the phase of incoming signal. This information can be used to help determine the direction of arrival and location of the transmission when combined with knowledge of the antenna response. More details of how this is performed will be given in an associated application note. This section will focus on the information provided by the device itself.

Depending on the variant of th e device there will be one or two antenna ports. Devices with two antenna ports are referred to as PDoA parts while the others are non-PDoA parts (see Table 1) . The two variants have different capabilities when it comes to Phase Difference of Arrival (PDoA) support.

For the "PDoA" parts, if the packet contains an STS then, depending on the configured mode, the device can compute the PDoA. There are two methods for computing the PDoA: PDoA Mode 1 and PDoA Mode 3.

PDoA Mode 1 functions with any packet containing an STS but is less accurate than PDoA Mode 3. On another side PDoA Mode 3 requires the STS length (in units of 512 chips, ~1 μs) to be an integer multiple of 128 (128, 256, 512). It is more accurate than Mode 1 but the packets will be longer (se e PDOA_MODE in SYS_CFG register on how to configure the required mode).